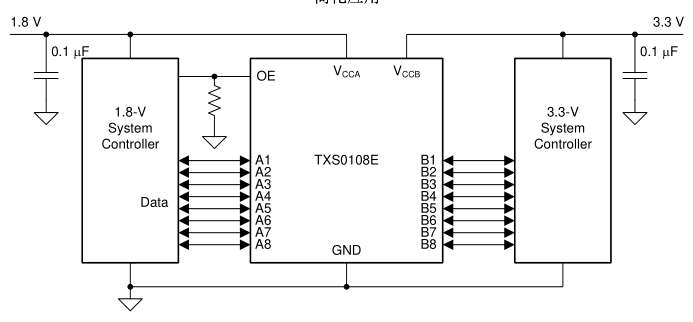

有一AD9643模块,其数字部分电平为1.8V,为了能够跟3.3V电平的主机进行通信,需要使用电平转换器。而又因AD9643的SPI为半双工,因此需要使用一双向电平转换芯片。

为了实现该应用,我们使用德州仪器TXS0108E芯片,注意区分型号,同系列有多个不同功能的转换器。

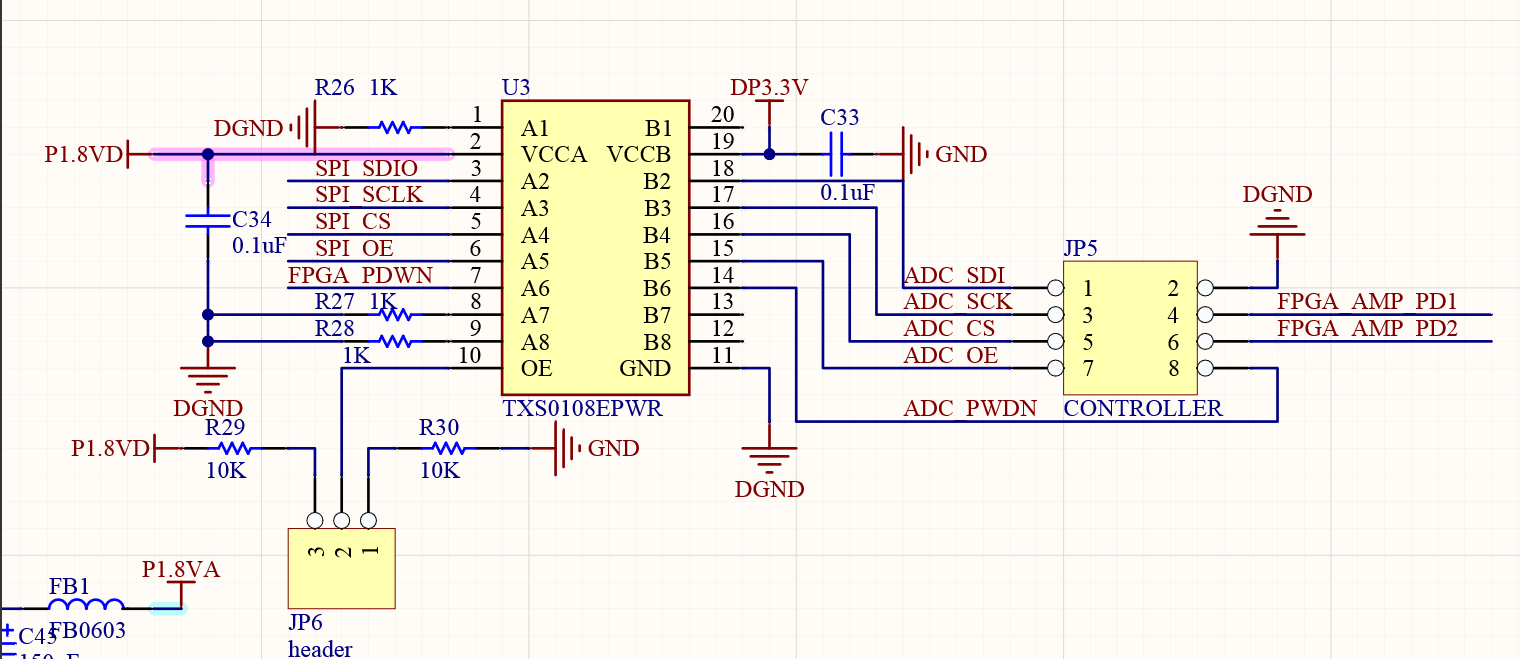

原理图如下图所示:

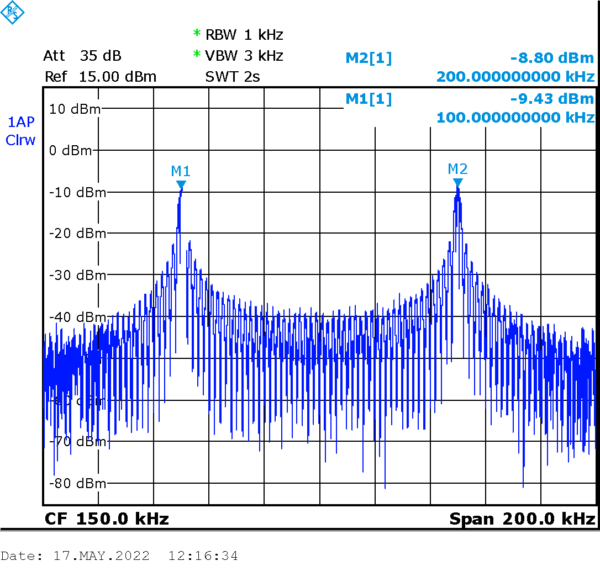

在使用过程中,发现SPI一直有误码,导致芯片不能够被正常的配置。

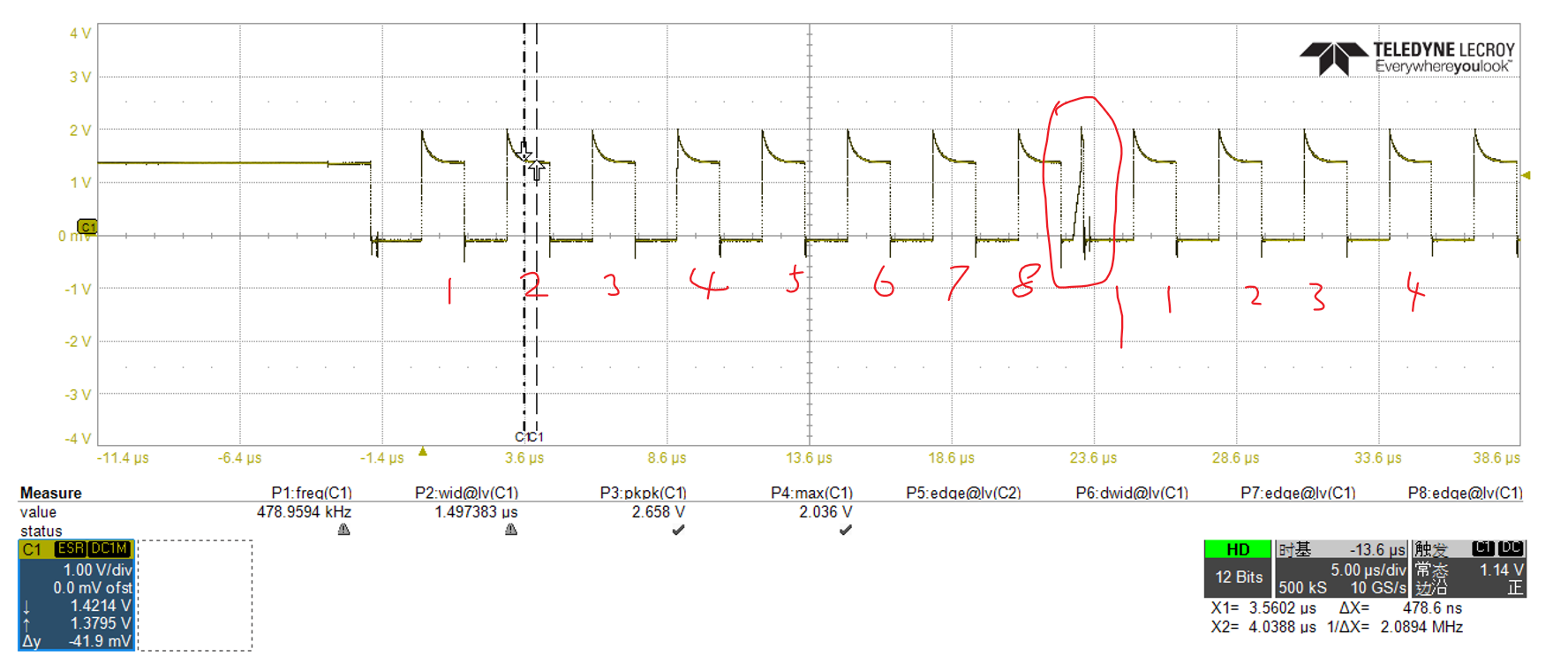

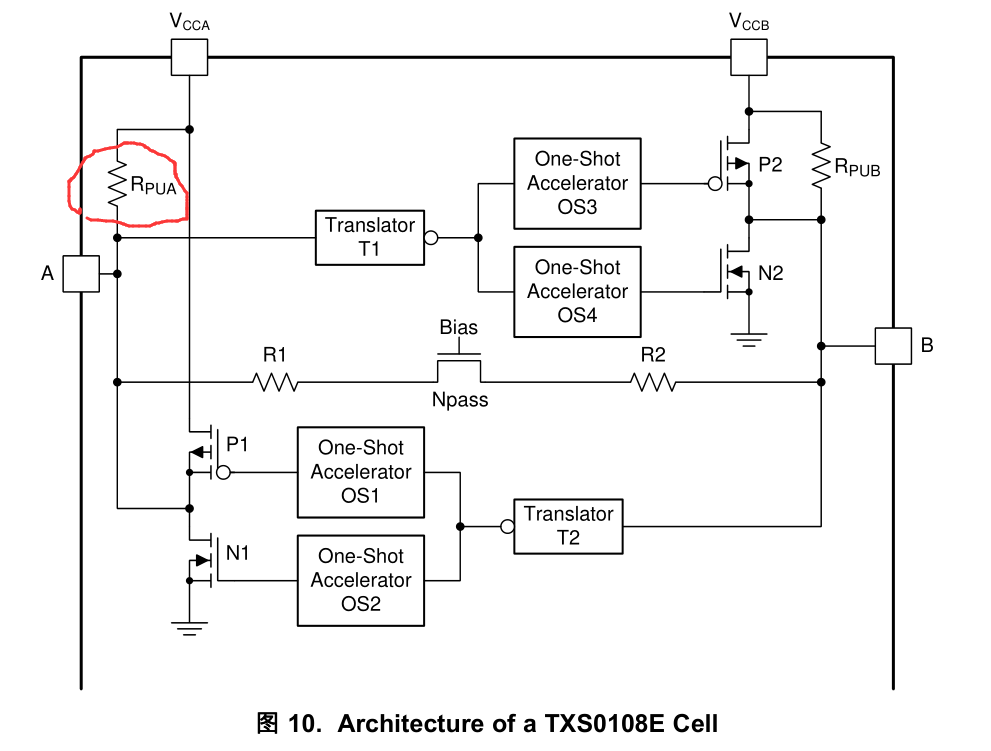

通过观察波形可以发现这个故障,在SPI主从机切换的一瞬间,主机切换到高阻态,因为芯片内部有上拉会导致有一侧的吸电流突然释放,电平转换器又是自动切换方向的,当他识别到这个向上的电压,他会认为你发送了东西,导致在从机时钟线上出现一个正脉冲,扰乱了后面所有的时序。

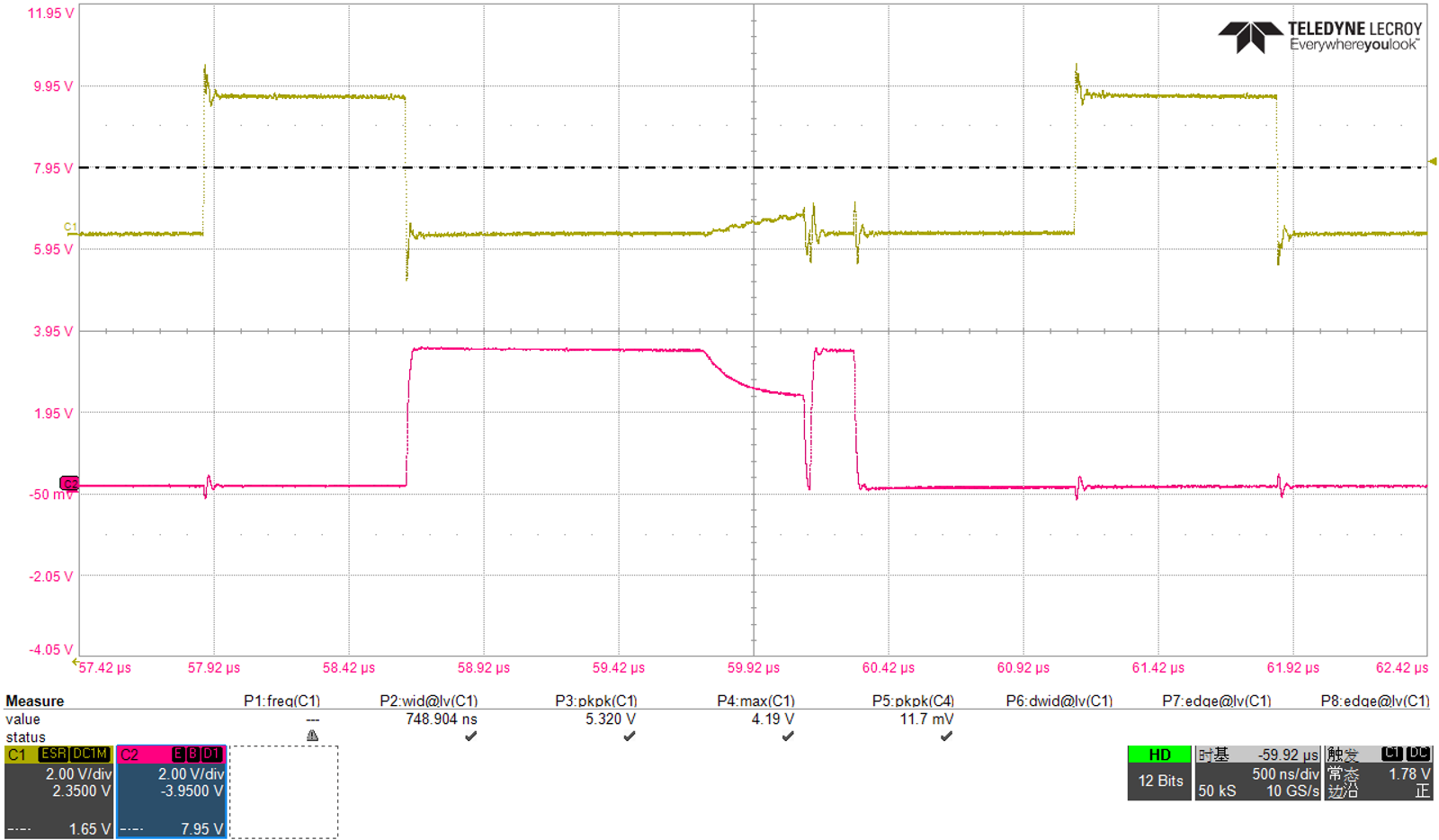

为了解决这个问题,我们在SCLK SDIO 单片机端 下拉10K电阻之后,时序恢复正常,无误码。虽然此时在中间切换的瞬间,上下两个拉电阻同时作用,导致电平处于一个大约500mV的水平,不能够触发高电平,但是属于一种危险现象,虽然故障临时得到了解决,但是仍然不完美。

在此可以看到虽然SDIO仍有波形异常,但是位于非判决时间,带来的影响不大。振铃通过添加线间电阻解决

在文章的最后,我想说的是可能这种半双工的通信方式本身就不适合在上面做电平转换,容易引入很多不稳定的因素,另外我认为这跟TI芯片设计辣鸡也有关系,只能说这是一种妥协,我另外还测试过一个国产替代TI的芯片,误码现象更严重,整个电平一团糟。最好的解决方法还是完全替换掉这个方案,或者增加一根线使用外置MUX来切换一个全双工SPI,虽然这么做不那么优雅,但是的确可以临时解决问题。

在之后的设计中,我们直接使用FPGA内部的逻辑电路来连接SPI,避免了使用电平转换器,从根源上解决了这种问题。