好久不见,这次是时隔3个月的更新~

还记得🐟在做飞安级静电计前端时,文末使用的大杀器——EmoeDAQ么。做完静电计这个项目后,🐟想把这个为了醋包的饺子给完善一下。

其实早在2021年🐟就想做精密ADC模块了,当时的项目命名为 EmoeMetrology,事实证明我高估了我的财力…想做n位半,就得有精度至少有n+1位半的标准仪器来校准。而要做8位半,校准所需要的标准基准只能说约瑟夫森结 + 高精度Kelvin-Varley Divier这种等级的计量标准了……

不过,🐟有万能的群友们的支持!8位半做不到,可以做6位半。这次我们来做一个精度6位半的数据采集器模块~

本文目录

1-何为DAQ?

DAQ是 Data AcQuisition 的缩写,意为数据采集器/系统。实际上他的作用就是将各种各样的模拟信号转换为数字信号,方便工程师/科学家的测试测量。听起来和ADC的概念很像吧?其实DAQ的核心就是ADC,不过在前面加上了信号调理电路,拓展了ADC的输入范围,并且为待测模块和DAQ系统后方提供电气保护和电气隔离。

下图是Wiki上的DAQ系统信号链示意图,物理信号经过传感器变为电信号,此信号输入DAQ模块,经过DAQ前端的信号调理后输入ADC进行模数转换,最后变为数字量输出到上位机/其他电子系统中进行分析与处理。

市面上也有很多大公司有DAQ产品在售,多数为PXI系统仪器,需要搭配PXI机箱+控制器使用。比如National Instruments(现在被艾默生收购)的DAQ系列产品线,从compactDAQ到标准PXI仪器板卡一应俱全。

然而这些板卡和模块的售价都十分感人…即使是电子厂里淘汰的二手货,🐟也囊中羞涩用不起。(如果有钱…谁又愿意自己搓呢(bushi)

当然,自己做DAQ不仅是因为包里没米,还因为🐟贪玩。

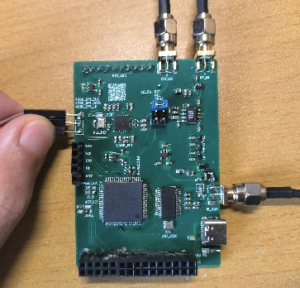

2-EmoeDAQ-24

此次设计的板卡代号为EmoeDAQ-24,数字尾缀是ADC分辨率的意思,也就是这张板卡的分辨率是24bit。EmoeDAQ-24的预期指标如下:

-

通过USB-C供电,+5V功耗小于0.2W

-

配备铝合金外壳,小体积(与EmoeNAP同尺寸)

-

输入侧与USB接口及数字部分电气隔离,隔离等级1.5kVrms

-

2个差分输入通道:

- 24bit 有效分辨率,6位半精度(能显示±2 000 000字)

- 噪声尽可能小,预期最高无噪声分辨率22bit

- 全差分电压输入,输入范围为差分±5V(小信号档位下为±250mV)

- 输入阻抗>1GΩ,输入偏置电流<10nA

- 采样率从5Sa/s至1kSa/s可调(主打精密DC精度)

-

1个电压输出通道:

- 高达24bit有效分辨率,经过校准后实现6位半输出精度

- 输出范围0V至+5V

- 高容性负载驱动能力

同时,我们希望EmoeDAQ可通过串口控制并传送数据,控制协议兼容主流数字万用表的SCPI协议及格式,这样可以非常顺畅地与主流仪器的上位机软件兼容。

3-Design

在Design之前,我们来分析一下,为了达成设计目标,有哪些电路与细节需要注意。🐟梳理了目录如下:

- ADC关键参数选型

- ADC的电压基准源

- ADC的驱动器与抗混叠滤波器

- 系统的隔离电源与接口

那么我们开始design step by step。

在这一切(痛苦)开始之前,我们先来看一张图,经典的Accuracy Translator:

这张图从左往右依次是:动态范围(dB)、有效分辨率/百分比、PPM(百万分之一)、折算成万用表的精度(几位半),来源于Linear的 AN-82-Understanding and Applying Voltage References

最右侧那一栏名为 "HP Mirrored Scale",可能是因为衡量万用表精度为几位半的这个评价方法是由HP最早提出的。

看完这张图,我们就对测量精度有了非常直观的了解。如果一个系统达到了6位半精度,系统的动态范围将达到127dB以上,接近130dB、有效分辨率约为21bit、系统精度达到0.5ppm。

根据这些参数,我们就可以开始设计、评估我们的信号链了。

3.1-ADC选型

对于精密ADC,我们需要重点关注以下几个指标:

- ADC架构(S-D/SAR)

- 不同数据速率下的ENOB(Effective Number of Bits)

- 积分/微分非线性度(Integral/Differential NonLinearity, INL/DNL)

- 是否单调,无失码(No Missing Codes)

- 零输入失调误差与漂移

- 增益误差与漂移

- 如果带输入缓冲器/PGA,注意这些器件开启时的性能恶化影响与输入范围变化

- 外部参考电压输入范围与吸纳电流要求

- 自身噪声水平(低频)

如果我们的应用场景是交流信号采集,我们还需要关注THD+N、SNR、SFDR等一系列指标。但我们这次主打DC精度,就不挑啦。

因为 几乎所有的ADC都不能做到无噪声分辨率等于实际量化分辨率(除了个别超低噪声精密ADC,在严格控制的实验室环境可以做到),所以如果我们想要一个无噪声分辨率为21bit的ADC,那我们目光应该向至少24bit看齐。

前段时间,🐟的目光被这颗变态的ADC吸引住了——AD4630/32-24:

经过对比,单论线性度来说,这应该是目前市面上精度最高的ADC了,没有之一。0.9ppm (最大)积分非线性度(INL),典型能达到0.1ppm!而别的24/32bit ADC普遍都还停留在典型值3ppm以上的水平。如果用这颗ADC设计DMM,未经校准的情况下就能依靠器件保证6位半的水平,校准后甚至可能达到7位半精度。

那么代价是什么呢?这颗ADC采用了非常先进的设计,在一个封装内集成了多个ADC用于闭环自校准提高精度,所以价格十分的昂贵。

考虑到成本问题,在一众24bit的ADC中,🐟选择了AD7175-2这颗24bit的Σ-Δ型ADC。因为这颗ADC可以pin to pin兼容AD7177-2,可以通过更换芯片+更改软件的方式将24bit提升至32bit,能让ADC的动态范围提升不少,方便我们后期升级。并且7175-2的性价比相当不错。

在ADC输入缓冲器禁用的情况下,7175-2的INL典型值可达1ppm,器件保证最大3.5ppm,实际可以达到5位半的直流精度。寄希望于校准,我们可能可以实现6位半的直流精度。

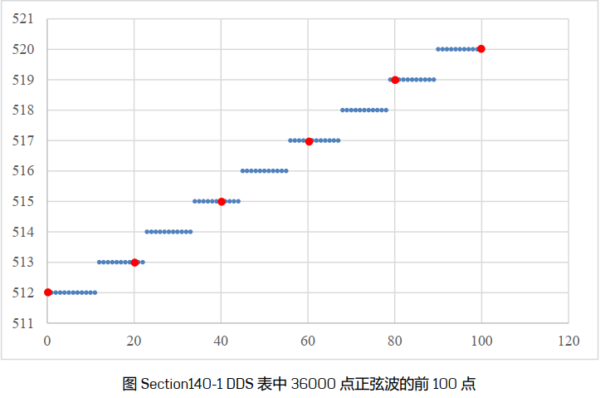

在看他的噪声测试图例时,我感到一丝疑惑:这nm是真的存在的?

在使用外部5V基准、输出速率5SPS时,ADC读数一个LSB都不跳动,这意味着此时ADC输入端的噪声小于1个LSB,也就是 5*2/2^{24} = 596nVpp ……兄弟,有点恐怖.jpg

不管这个数据是真是假,至少可以确信AD7175-2在数字滤波器拉满的情况下,能实现21bit以上的有效分辨率,在噪声性能上满足了6位半的要求。

至于零输入失调和增益误差,这些都是可以通过系统校准来修正的,关键在于这些误差的温度漂移情况。如果在25°C室温下对系统进行了校准,换到10°C室温下,系统精度又飘得很严重,那就不太好了。7175-2的失调漂移为80nV/°C、增益漂移为0.4~0.75ppm/°C,算是不错的指标。

那么就决定是你了,AD717x-2。

3.2-基准电压源选择

在之前的 精密电压源设计 一文中,我们曾探讨过精密电压源的指标需要注意如下参数:

- 输入输出电压,及最小压差

- 初始精度误差(容差)

- 温度漂移系数

- 噪声

- 短期稳定性与长期稳定性

- 负载灵敏度

- 线路灵敏度

- 动态负载响应

- 封装形式与湿度敏感性

- 热迟滞

- ……

同时,在 精密电路硬件设计指南 一文中,🐟也陈列过一些精密电压基准IC在布局、Layout、焊接等方面需要注意的事项。

这些讲完后,这次来讲点不一样的——基准电压源的类型及特性。以下内容参考ADI的MT-087:基准电压源

基准电压源IC的核心架构可分为几类:

- 齐纳(Zener)/雪崩(Avalance)二极管型,也就是常见的稳压管

- 带隙(BandGap)基准

- 深埋齐纳二极管型

Zener管的基准最简单,就像一个三端稳压器一样,使用方便成本低,可以做比较高电压的基准。当然性能也是最差的一档,温漂、噪声、最小压降等指标均不如人意,仅仅用在成本敏感的应用场景中。

带隙电压基准是在硅片上的电路做出来的,原理是匹配晶体管Q1-Q2之间的电流密度差在R3上会产生一个电压 \Delta V_{BE},此电压在R2上被比例放大,再加上Q3的BE结电压VBE,得到输出电压VR。

这种结构中\Delta V_{BE}和VBE的温度系数极性相反,所以他们求和后的输出呈现出的温度系数大大减小。当这两个电压求和后输出等于1.205V时,输出的温度系数最小。

最简单的BandGap模型

带隙基准应该是现在应用最为广泛的基准,因为他可以集成到硅工艺IC中,稳定性好,供电电压低,噪声非常低,精度也可以Trim到较高水平。常见的集成基准源的ADC/DAC器件中,基准源基本都是BandGap。分立BandGap基准源比较典型的有ADI的ADR45xx系列、TI的REF50xx系列。

最后要介绍的是深埋齐纳基准。

在IC中,表面工艺的二极管结点击穿容易受到晶体瑕疵以及其他污染的影响,因此,表面形成的齐纳二极管比深埋齐纳二极管噪声更大、稳定性更差。深埋齐纳IC基准电压源采用更具优势的嵌入式齐纳二极管。这样可以使噪声和漂移性能相比于表面式齐纳二极管显著提高

具体到chip level的话大致就是,深埋的Zener的die上杂质更少?希望有懂工艺的大佬给俺讲讲…

ADR1001 开盖的die shot

当然性能是有代价的。深埋齐纳基准的功耗更大,而且通常为了发挥性能,需要配备恒温电路,所以这东西的静态功耗和动态功耗都远高于之前的BandGap。

3.2.1-需要关注的噪声

对于精密DC应用来说,我们主要需要关注基准电压源的0.1Hz-10Hz带宽内的噪声 ,因为更高频率的噪声成分会被ADC的数字滤波器平均而衰减掉,对测量最终的噪声影响不太大。

0.1Hz-10Hz处在基准电压源的1/f噪声区间内,属于超越噪声。假如ADC以20SPS的数据率采样,对结果造成影响的噪声就集中在这个频段。🐟做了个统计表,对比了下市面上几款精密电压基准的性能。

在对比噪声时我们需要注意一点,需要 把不同输出电压的噪声归一化。比如基准A输出5V,噪声5uVpp,基准B输出2.5V,噪声同样5uVpp,但这两个基准的噪声并不相等,归一化后A的噪声是B的一半。

图中可以看出,噪声性能最强悍的当属ADR1000,其次是LTZ1000和ADR1399。这些都属于深埋齐纳基准,价格昂贵。比较性价比的选择是ADR45xx系列,REF50xx系列虽然更便宜,但噪声过大,我们不选用。

同时,经典型号LM399广泛用于各种6位半DMM中,但注意到LM399的噪声性能已经被后来的BandGap超越了,但399的长期稳定性仍然远强于BandGap。所以现在一种流行的做法是用399提供长期稳定性自校准基准,然后用低噪声的BandGap作为ADC的参考基准,兼得长期稳定性和超低噪声性能。

如果我们设计的目标是宽带系统,比如20k、500k这样的带宽,那么我们同样需要考虑基准的宽带噪声性能。如果有必要时,我们需要对其进行滤波处理。

3.2.2-更低噪声?

LTC6655是一系列超低噪声的精密电压基准IC,Jim Williams对2.5V输出的6655的0.1Hz-10Hz带宽内噪声进行测试得到了775nVpp的结果。然而在超高动态范围的系统中,这样的性能仍然无法喂饱ADC。

在Linear Technology的 DN-568:Reference Filter Increases 32-Bit ADC SNR by 6dB 中,LT的工程师为我们展示了利用有源滤波器对基准的输出噪声进行滤波,以提高32bit ADC的信噪比和动态范围。

需要注意的是,有源滤波器的运放选型比较苛刻:对于第一级运放(图中LTC2057),要求其具有低失调和低漂移,并且为chopper型超低噪声运放最佳,因为chopper型运放自身并无1/f噪声,如此一来就不会反倒增加基准电压源的噪声。第二级运放要求具有低噪声的同时,还需要具有高驱动能力,以驱动ADC参考输入端上的大容量电容负载。

当然,也可以使用低成本的无源RC滤波器来滤除基准源噪声,并且这样不会为系统增加额外的失调误差,听起来是不是很棒?

遗憾的是,如果不谨慎选择RC的值,就极有可能造成噪声谱密度上的尖峰(Peaking)。如下图所示。同时,电阻的增加也会使得系统的直流精度下降,还会影响基准的带载能力和瞬态响应。

在这篇 模拟对话:为何基准电压噪声非常重要? 中,ADI给出了另一个有源滤波器来限制基准噪声的例子。这里使用了chopper输入的ADA4522和超低输入噪声的AD797。

那么我们在EmoeDAQ-24的设计中有必要使用有源滤波器吗?🐟觉得是没必要的,因为我们这里关注极低频直流性能,对于高频段噪声并不关注。同时,我们的ADC分辨率只有24bit,按照满量程10V(±5V)折算下来,1LSB=600nV,也就是说如果我们希望做到24bit的有效分辨率,信号链中的总噪声要小于300nVpp(1/2 LSB)。如果只要做到21bit,那么可以将这个要求放宽8倍(3bit),也就是噪声小于2.4uVpp即可。这个数值是可以实现的。

尽管增加滤波器确实能提升系统性能,但🐟想既然性能够用,就costdown一下(原谅我囊中羞涩吧

3.3-ADC的输入电压范围

驱动ADC最重要的一点首先是:输入信号必须满足ADC的输入范围要求。

对于差分ADC来说,我们需要同时满足共模输入(Common-Mode,CM)和差模输入(Differential Mode)电压要求。查阅AD7175-2的数据手册,可以看到其对输入电压的要求如下:

此处,我们假设各部分电压为:

- AVDD1 = +5.2V

- AVSS = 0V(GND)

- REF+ = +5V(ADR4550)

- REF- = 0V(GND)

那么:

- ADC的差分输入范围为 ±VREF=±5V(AIN_P – AIN_N,或AIN_N – AIN_P)

- ADC的绝对输入电压限制为 -0.05V至 5.25V(输入缓冲器禁用)

- 如果启用输入缓冲器,输入范围就是GND至AVDD1

如何解读这些范围呢?我们以仿真的电压结果来讲解:

我们用全差分放大器AD4937搭建一个单端转差分的电路,增益为1,共模电压为2.5V。输入信号为一个摆幅为1Vpp,直流偏置1V,频率1kHz的单频正弦信号。

测量各个输出电压节点电压如下图所示,从上到下依次为 输出的差分电压、输出的反相端电压、共模电压、输出的同相端电压,以及输入电压。除了差分电压外,下面信号的电压都是相对于GND(0V)测得的。

很形象的说,差分放大器的2个输出电压是"骑"在共模电压上且镜像的。

理想情况下,输入信号为0时,2个输出VoutP和VoutN都等于共模电压2.5V,但是其差分电压(VoutP-VoutN)为0V。当输入不为0时,VoutP和VoutN会向两边偏离,但(VoutP+VoutN)/2恒等于Vcm。

当输入电压为+5V时,VoutP对地电压将达到+5V,而VoutN对地电压为0V,VoutP-VoutN=+5V,此时将达到ADC的正差分输入范围最大值;

当输入电压为-5V时,VoutP对地电压将变成0V,而此时VoutN对地电压为+5V,VoutP-VoutN = -5V,此时将达到ADC的负差分输入范围最大值。

那么我们现在回头来看ADC的输入范围要求:差分输入范围典型值为±VREF,绝对输入电压范围约等于ADC的模拟供电电源轨

——前者描述的是输入端的差分电压,也就是ADC能够正确量化的电压范围。而后者描述的是任意一个输入对地的电压,如果任意一个输入端的对地电压超出此限制,就有可能导致读数异常,甚至烧毁ADC输入。

该怎么保护你,我的ADC 😭

3.3.1-保护ADC

怎么保护我们的ADC呢?通常的做法是:通过ADC的驱动器(运算放大器)的输出来限制ADC的输入范围,只要ADC Driver输出电压不超过此范围,那么ADC就是安全的。

很简单,只要让ADC Driver的电源轨等于ADC的模拟电源轨,即可实现保护功能~因为运放通常不可能实现高于电源轨的输出,所以只要运放没有内部一路被高压打穿,就不可能输出高于/低于电源轨的电压,从而保护了ADC。

3.4-ADC的驱动器

在前面我们已经演示了使用全差分放大器实现单端转差分的电路,把那个电路稍微改一改,反相输入端不接地,接差分反相输入,即可成为支持全差分输入的ADC驱动电路。

此时,同相输入端电压为1+sin(wt),反相输入端电压为1V直流,输出差分电压为sin(wt),由于同相输入和反相输入的DC分量相等,在输出中DC被抵消,故差分输出的两端对地电位关于Vcm对称。

有同学可能就会有疑问了,如果限制运放的供电来保护ADC,那么谁来保护运放呢?😭

3.4.1-驱动器之前…

很遗憾,上面提到的全差分放大器并不能提供极高的输入阻抗。低输入阻抗的后果就是测量高阻源时读数误差非常大,几乎到了不可用的程度。因此我们需要在差分放大器之前加一个高阻输入缓冲。

这些高阻输入缓冲需要有非常高的输入阻抗和低输入偏置电流,来满足DAQ模块的系统性能要求。同时还要求这些信号链中的运放都具有超低输入电压噪声,以及非常低的输入失调电压漂移。初始失调电压大一丢丢其实问题不是很大,因为我们可以通过系统校准来消除静态失调影响,但失调漂移必须严格控制,你也不希望你的电压测量值3分钟漂1mV吧.jpg

同样,这些输入缓冲放大器也采用和后面的全差分放大器同样的电源供电,来确保输出不会超量程。这样,这些缓冲放大器就保护了全差分放大器。那么,谁来保护你呢,输入buffer?😭

3.4.2-驱动器之前之前…

别急,我们还没说完。

还记得我们的DAQ有2个输入通道吗?

虽然AD7175-2有5个输入端,可以组成2对差分输入,还能余一个单端输入,但这样会增加额外的硬件成本(多一通道的运放)…在多通道DAQ中,常用的一种做法是使用模拟开关/继电器去切换输入通道,实现单个ADC时分复用采集多个输入信号的效果。

如果不是频繁的切换,我们可以用继电器来实现这个功能,但需要注意继电器的 接触热电势影响,对于精密测量设备来说,这项误差也是十分显著的。如果需要频繁切换输入通道,比如经常需要执行高速扫描采集的应用,继电器唱歌可不好听…这种情况下还是用高性能模拟开关比较好。

于是乎,我们又在高阻输入缓冲运放前加了一个DP4T(Double Pole Four Throw)的模拟开关,用于切换输入通道。但我们只有2个通道呀,为什么要用DP4T而不用DPDT呢?请看下图。

答案是,我们可以将开关切换到3通道,给后级输入通上一个-VDAC电压,然后再将开关切换到4通道,给后级输入通上一个+VDAC电压,对系统实施闭环自测试,同时为系统进行增益和失调校准。

当然,这个校准过程需要更高一级的计量标准传递下来,简单来说需要一个至少7位半的数字万用表,来监测VDAC电压,并且将更准确的数值输入到DAQ中,DAQ再获取自己测到的测量值,根据更准确的值计算出增益和失调误差,完成系统级的增益和失调校准。

那么。。。谁来保护你呢,模拟开关?😭

3.4.3-模拟开关当自强

唉,谁让模拟开关天天干脏活累活呢,就连designer也开始心疼起了这些器件,在设计时专门针对过压、ESD、高电流场景下做了保护措施。

比如ADI和TI这2款模拟开关,小小身躯能挡住±55V以上的高压输入而不被击穿失效(即使电源轨只有±5V,甚至在系统断电情况下,能挡住外部高压不向后灌电流),同时还具备抗ESD击穿、闩锁免疫等强大特性。

模拟开关:我保护我自己😎

3.4.4-模拟开关支楞不起来…

前面提到的强大模拟开关并不是易得之物…如此强大的功能带来的副作用就是:价格+++++

那么如何在模拟开关支楞不起来的情况下,保护那些比较柔弱的模拟开关呢(

我们需要ESD器件,通常是ESD二极管,来保护模拟开关输入管脚免遭外部静电放电或高压短脉冲的损伤。

加上ESD二极管,至少我们可以对端口被静电干穿放心一些了…但过压仍然是个问题,在这里🐟用了一个前级RC滤波+共模滤波器+后级RC共模滤波的输入级,这样输入信号进入端口,传输到模拟开关输入时有着至少330R以上的直流阻抗,一定程度上可以保护模拟开关输入。

如果输入电压实在过高,达到了ESD二极管的击穿值(这里我用的8V,因为正常输入最高可到+5V左右,选用5V的ESD容易误触发),ESD二极管将首先阵亡。ESD阵亡后如果模拟开关承受不住过压开始失效,输入电流也会被限制在一定值以下,只要电压别高得离谱(比如100V),这个前端能存活的可能性还是很大的。

3.4.5-输入电流

这时候我们就可以看看输入级信号路径了,同时检查输入电流能否满足我们的设计指标。

不考虑电容的漏电流影响,输入端的电流由几部分组成:

- ESD二极管的漏电流

- 模拟开关的输入/关断漏电流

- 缓冲运放的输入偏置+失调电流

通过氪金选型法,我们可以选到输入电流在100pA以下的运放,以及输入漏电流10pA以下的模拟开关。然而ESD二极管的漏电流却是个难以降低的指标…很多ESD二极管的漏电流都在uA级,需要选择低漏电型的ESD才能实现我们的设计目标,然而🐟找了一圈只发现一个10nA漏电流的ESD二极管(图中型号,还是个国产),所以系统的输入电流主要由这个ESD的漏电流主导了。

3.5-ADC的抗混叠滤波器

那么,这样就够了吗?很显然,我们还需要考虑一个任何模数转换系统都需要考虑的问题——带宽(Bandwidth)。

本小节参考ADI的 MT-002:What the Nyquist Criterion Means to Your Sampled Data System Design,非常推荐移步学习一下。

在数模转换系统中,采样信号带宽 是至关重要的参数。

在很早一篇文章 —— 中高速模拟信号采集系统 中,我们曾简单地从时域中探讨过为什么ADC需要抗混叠,这次我们从频域来看看。

现在我们用理想的脉冲采样器以Fs的采样率对频率为Fa的理想单频正弦信号进行采样,同时确保Fs>>2*Fa以满足奈奎斯特采样定理,从频域中观察输出的采样结果是这样的(下面的图中上部分):

我们会发现除开在Fa处的主信号外,Fa和Fs进行一次混频后得到了Fs±Fa,并且混频产物在频域中被以1/Fs为周期无限延拓了(当然,延拓的次数越高,能量越小,不然无法满足能量守恒定律了…)这是因为理想采样脉冲信号是一个理想冲激信号,其频谱为sinc函数,在频域中无限延拓。

如果此时被采样信号频率Fa’仅仅略小于Fs,并且Fa’=Fs-Fa,那么现在再用同样的理想采样系统对Fa’进行采样,我们会发现,我们好像得到了与之前相同的结果(上图中下部分)。如果你写出理想采样的表达式,通过计算傅里叶变换也可得出这个结论。即 如果我们不对ADC的输入端信号的带宽做任何限制,任由频率高于1/2采样率的信号自由进出,那么ADC的转换结果将出现无法预测的镜像频率和杂散响应。

即使能保证ADC输入是绝对的单频信号且信号频率低于1/2采样率,信号中的宽带噪声同样会因为采样"折叠"到我们的采样分析带宽内,从而增大系统的底噪,降低了系统的SNR。

所以,建议为任何ADC的输入端都增加抗混叠滤波器以限制输入信号的带宽,这样能确保采样信号的完整性,提高系统的信噪比。

3.5.1-题外话:带通采样

最常见的ADC用法是采集DC至某个频率FC处的一段信号,系统整体响应是低通型;而在某些应用中,比如通信/射频,ADC可能采集的是从某个频率FL开始,到某个更高的频率FH结束的一段信号,系统整体响应是带通型。针对不同的系统和ADC器件,所选用的抗混叠滤波器类型不同

比如在很多中频接收机中,需要采样一个中心频率300MHz、信号带宽40MHz的中频信号,此时选用1GSa/s以上的ADC难以实现信噪比和性价比、功耗和逻辑资源开销的平衡(总之越高速的越难伺候),这时的普遍选择是使用 宽带中频ADC,以较低的采样率对中频信号进行欠采样(也叫谐波采样、带通采样等),将信号从高频率处搬运到第一奈奎斯特区(DC-0.5Fs)进行处理。这个采样过程等效为一次频谱搬移,相当于中频ADC充当了数字混频器的作用。

LTC2208具有130Msps的采样率,但前端的采样保持器有着700MHz的满功率模拟带宽,意味着它可以通过合理设计的欠采样处理700MHz以内的信号。

又有同学可能要疑惑了,奈奎斯特采样定理不是说采样率要高于采样信号的最高频率的2倍以上,才能获得完整的信息么?

其实奈奎斯特采样定理的真正含义是:带宽为BW的信号必须以等于或大于其带宽两倍(2BW)的速率进行采样,方可保留信号中的全部信息。

注意此处的用词并不是频率,而是带宽,bandwidth。对于LTC2208来说,如果中频信号的带宽大于65MHz,它就无法完整量化信息了。如果中频信号的中心频率在500MHz,带宽为50MHz,实际信号的频率范围为475MHz~525MHz,通过合理设计抗混叠滤波器,LTC2208是完全可以准确量化此中频信号的。

如果你对于射频接收机感兴趣的话,可以移步 雷达信号处理-[3]-数字下变频(DDC) 欣赏一下CNPP同学的超外差接收链路。

3.5.2-精密ADC的抗混叠滤波器

这一块感觉是个比较难的课题,难以通过仿真得出结论,通常需要大量的重复实验来测试,并且针对不同的ADC型号,设计取值不尽相同。所以我在此也仅仅是引用ADI的实验数据和结论,抛砖引玉一下。

此节参考来源:非常见问题第209期:如何组合使用低通滤波器和ADC驱动器获取20 V p-p信号

在精密ADC中,ADC采样时内部输入开关切换到输入引脚上,接通驱动器输出,为内部采样保持电容充电,采样结束后,内部输入开关切换到ADC上进行保持,并开始ADC转换。当转换完成再次将开关切到输入上(输入有输入驱动器+无源RC组成的抗混叠滤波器),变成采样模式时,由于外部电压变化或电容电荷泄放等原因,将导致ADC采样电容对外有一反冲电流,造成输入信号的波动。

此电压波动的大小和稳定速度取决于RC滤波器的时间常数、驱动器输出阻抗等一系列因素,同时如果它稳定的足够快,在ADC高速采样期间对结果造成的干扰非常小,那么可以视为不恶化ADC性能;如果此影响过大,就会导致ADC的THD、SNR性能恶化。

同时这个效应在越精密的ADC中越严重,因为ADC的分辨率越高,就对这些微小扰动越敏感。标称-120dB THD的24bit ADC,如果因为抗混叠滤波设计不当,THD掉到-100dB也是有可能的。

ADI在相同输入信号的条件下,测了2组不同电阻、不同带宽的数据,可以看出,使用较大电阻有助于提高THD,但降低了SNR;同样的,使用更小的电容可以提升THD性能,但因为系统带宽的增加,SNR恶化。

ADC的抗混叠滤波器设计步骤大致是:

- 确定系统信号带宽

- 根据带宽选取合适的R/C值

- 测试性能,迭代优化

在带宽确定的情况下,R和C中任意一个确定下后就确定了另一个。增大R减小C会增加ADC输入端的热噪声(当然,如果不是高精度ADC无所谓,别太离谱就行),同时小电容会使得反冲电流更大。增大C减小R 可能会让驱动器不堪重负(毕竟是个大容性负载),容易导致信号振铃(驱动器变得不稳定),大电容可以降低反冲电流。

总之是个头疼的过程,建议如果厂商给出了参考设计或者推荐取值,可以省事直接用。如果有仿真工具(比如ADI的Precision Studio)也可以用仿真工具确定取值。

3.6-系统的隔离电源与接口

在飞安计前端项目中,我们使用EmoeDAQ的原型机完成了数据采集,得益于EmoeDAQ的电气隔离,极大程度地消除了测试信号链中的电源环路噪声,最终得到了非常干净的电流测量结果。

隔离在测试测量中是非常常用的手段。共地测试通常会带来各种各样的问题:环路耦合噪声、高共模电压、电平/接口不兼容…通常的台式万用表使用工频变压器,将市电输入降到低压,分几路相互隔离的输出,分别供给DMM的数字系统、对外接口、模拟系统使用,并且在数字与模拟系统之间使用光隔离器或磁隔离器实现控制信号的电气隔离。

这样,DMM的输入就是完全浮空(Floating)的,也就能支持一些特殊场景下的测试测量应用(比如高压电源等)。

当然隔离并不是无限度的。当隔离两端的电压差超过一定值,隔离介质就会被击穿失效,这个限值就是隔离系统的隔离等级。比如常见的数字隔离器可以耐受隔离两侧500V峰值压差,短脉冲耐受可以到4kV,更高级的隔离器甚至能耐受8kV。

上面是ADI的一个磁隔离器芯片内部die装配图

可以看到中间的隔离barrier上下层各有一个小线圈,用于传输隔离的1bit数据。输入信号经过芯片调制传送到隔离barrier上的发送线圈,通过电磁场耦合到接收线圈,送到接收端解调恢复信号,就完成了数字信号的电气隔离传输

在EmoeDAQ中,因为我们是小体积设计,并且希望通过USB的+5V电压为整个系统供电,那么我们的隔离设计除了接口外还必须包含一个足够功率的电源。ADI还有这种隔离接口+电源的集成芯片,同时提供隔离电源和接口,方便体积受限的隔离电路设计,比如下图的ADuM5242,他提供了2个数字隔离接口的同时,还提供了50mW带载能力的隔离电源,很方便隔离ADC应用。

但EmoeDAQ的模拟电路部分还是挺多的,这些电路功耗总和不小,不是50mW这个级别…并且,这芯片太贵啦。

在这里我们选择了分立的隔离电源方案,利用推挽变压器驱动器+变压器实现隔离电源。

同时为了优化系统EMI,在推挽输入侧电源轨上串联一颗2.2uF的馈通电容滤波器,抑制高频开关尖峰的传导辐射,以免对外部USB电源总线造成过高的额外干扰。

变压器输出端用2个小功率的开关二极管对输出全波整流,得到正负电源轨,后经过无源滤波器和低噪声LDO稳压,为后面的模拟电路、ADC和电压基准等芯片提供干净的电源。

关于低噪声电源,请参考之前的文章 精密低噪声电源设计

到这里为止,EmoeDAQ的设计就告一段落!

接下来我们只需要把系统的各个部分组合在一起,绘制完原理图,就可以愉快地开始Layout了~

紧接着而来的就是惊心动魄(摸鱼划水)的软件开发、系统校准与测试环节。由于篇幅所限,一篇文章就不写太长了,敬请期待本文的下篇吧\^_^

参考链接

- Wiki-DAQ

- NI – DAQ

- AN-82-Understanding and Applying Voltage References

- AD4630-24 datasheet

- AD7175-2 datasheet

- 精密电压源设计

- 精密电路硬件设计指南

- MT-087:基准电压源

- DN-568:Reference Filter Increases 32-Bit ADC SNR by 6dB

- 模拟对话:为何基准电压噪声非常重要?

- MT-002:What the Nyquist Criterion Means to Your Sampled Data System Design

- 中高速模拟信号采集系统

- 雷达信号处理-[3]-数字下变频(DDC)

- 非常见问题第209期:如何组合使用低通滤波器和ADC驱动器获取20 V p-p信号

- 精密低噪声电源设计

![雷达信号处理-[1]-噪声信号与雷达基带信号产生](https://www.emoe.xyz/wp-content/uploads/2021/11/4-2-600x316.jpg)

TPD4E1B06这个ESD的漏电流在2.5V,25℃时最大值为0.5nA,很便宜

MAX30034这个ESD的漏电流在5V,25℃时最大值为1nA,典型值3pA,比较贵