本文目录

微观尽头——精密信号测量:理论分析

在上一篇文章中,我们欣赏了HP 3458A的精妙绝伦的多斜率积分ADC架构原理,同时也对精密信号测量有了基本的概念,那么这次让我们来试着自己做一个精密信号测量电路。

商业数字万用表(DMM)

我们可以参考市面上比较厉害的数字万用表的参数,比如吉时利的DMM6500。为什么是这款呢?因为我用过最高端的DMM是这个(

这款6位半的数字万用表能测量10pA到10A的电流,1uΩ到100MΩ的电阻,以及100nV到1000V的电压,同时具有5英寸的电容触控屏,可以将采集到的数据以曲线、表格等形式呈现出来以供分析。(怎么搞得我像是打广告的(雾))

这台万用表的核心ADC器件是一个16位、1MSPS的ADC,光靠这片ADC是无法实现6位半精度的(22位有效精度),我猜测他们应该是使用过采样算法将有效精度提升至了6位半。

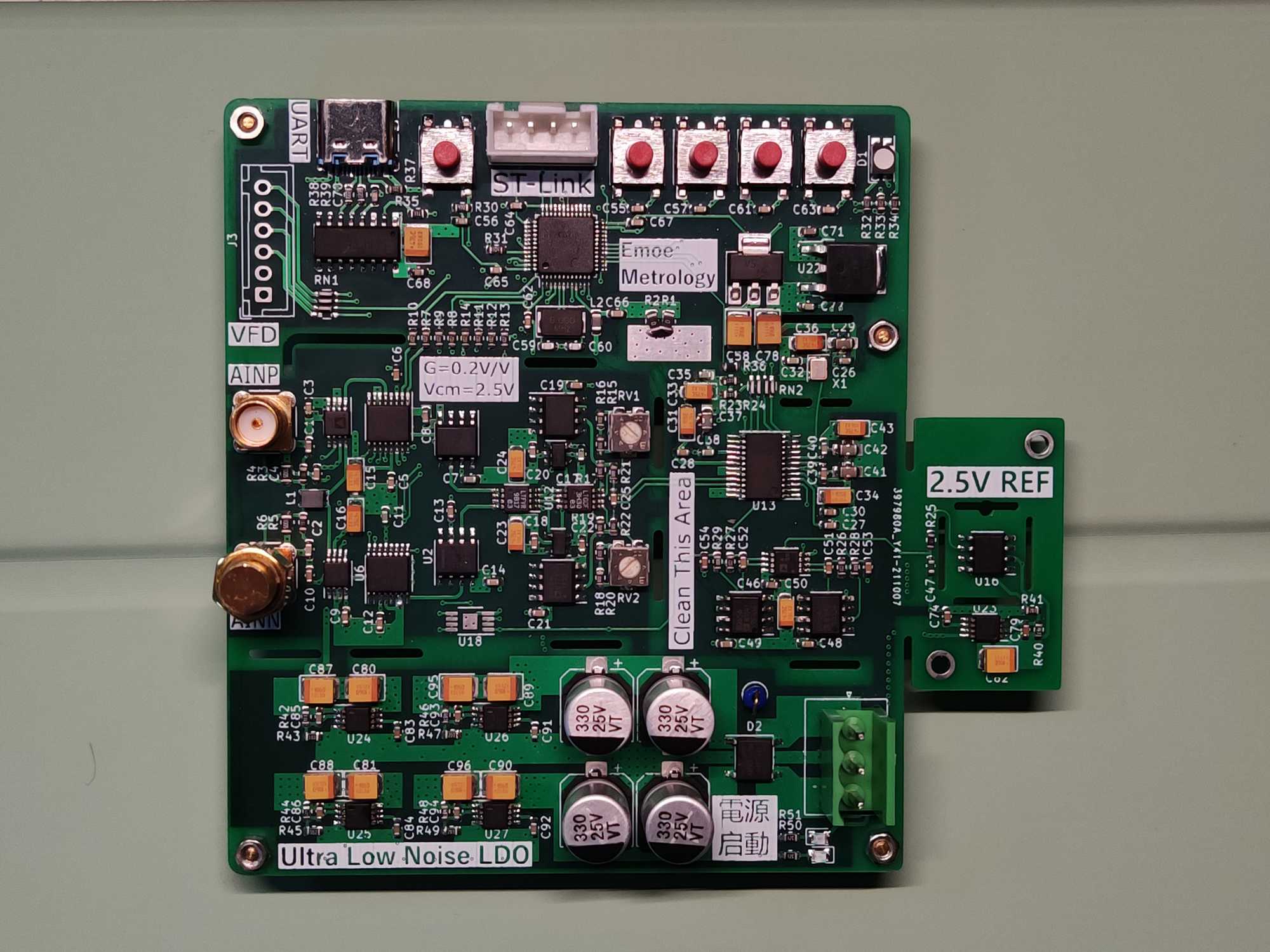

EVM

当然,光靠ADC本身是不能实现如此多的功能、也不能实现如此高的测量范围的,如果要做一台数字万用表,那么必须为ADC设计不同的前端电路来实现各种功能和档位切换,而这个系统对于验证阶段的我们来说太过于复杂。所以我的计划是设计一个ADC评估模块(Evaluation Module,EVM),先用这个模块简单地验证一下ADC和模拟前端的性能参数是否达标,同时也锻炼一下我的精密小信号电路、以及数模混合系统 PCB Layout的能力,积累经验(踩坑)。

所以我将设计一块这样的板子:

- 搭载核心器件——ADC,型号为ADI的AD7177-2(32位集成式ADC)

- 使用市电+变压器为电路供电

- 使用超低噪声LDO为精密模拟电路供电

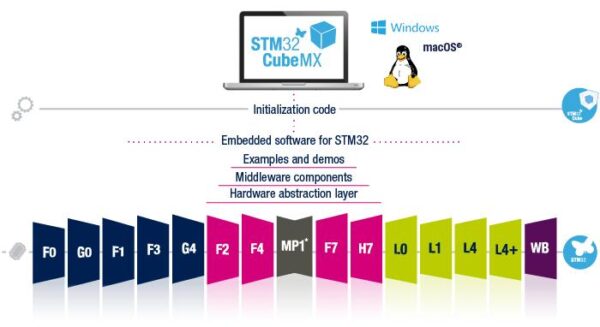

- 板载一块MCU,用于连接ADC和控制模拟前端电路,同时MCU负责处理数据并通过串口将数据回传至电脑

我决定为他命名为——EmoeMetrology 🙂

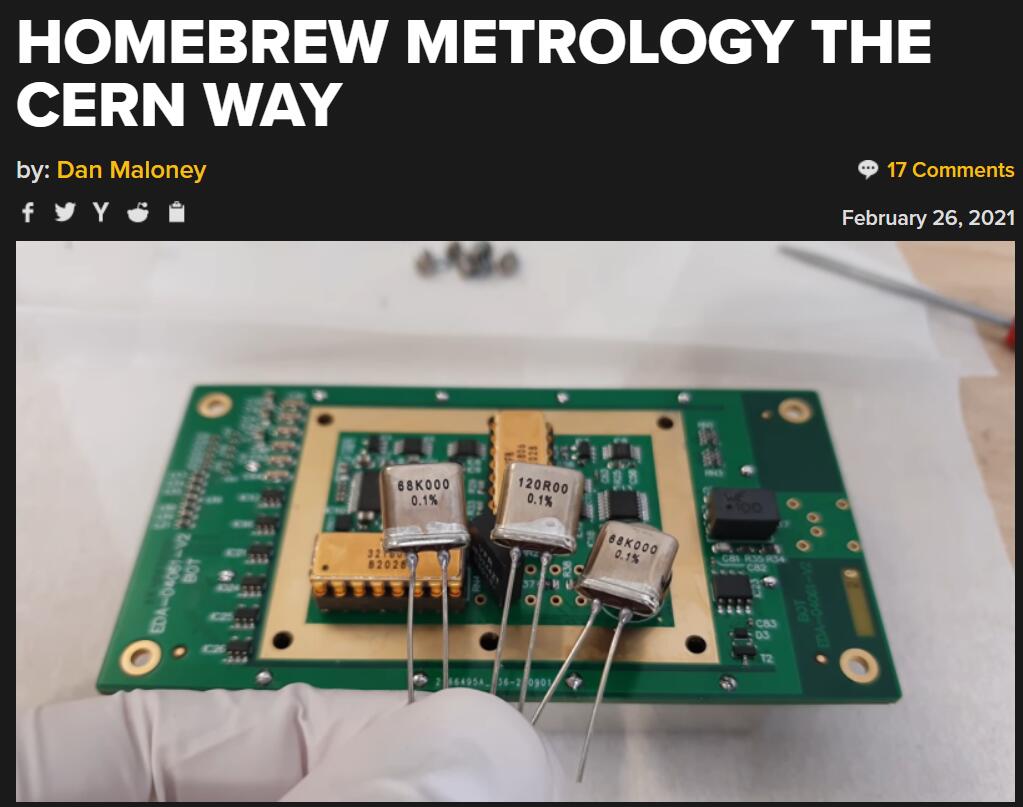

借鉴——CERN HPM7177

前段时间Hackaday上公开了 这么一篇文章,CERN制作的开源8位半数据采集系统,核心的ADC器件是AD7177,所以它们为这个工程命名为HPM7177,这个数据采集系统将用于CERN的 高光度大型强子对撞机 项目,它们需要上百个这样的数据采集器来完成高精度的实验数据采集任务。(不得不说CERN的宣传做的真不戳。)

这里 可以找到他们开源的项目文件,在他们的文件托管服务器上,其中最核心的模拟前端+电压基准的电路图可以在 这里 摸到。

可以看到他们的设计非常精细,为整个模拟电路部分设计了一个恒温腔室,用以确保基准源和模拟前端的热稳定性,同时金属腔体也起到了屏蔽外界电磁干扰的作用。看到那块小板子上的2片金灿灿的芯片了吗?如果我告诉你它其实是电阻你会不会…

好吧,其实它真的是电阻,是Vishay生产的超精准、精密匹配、低温漂、无感薄膜电阻网络。这2片电阻网络一个将用于精密的模拟前端电路,另一个部分会用于基准电压源输出的分压网络。

看见那个银色的圆金属封装芯片了吗?那个就是LTZ1000,地表最强的基准电压源。它拥有0.05ppm/°C的超强绝对温度系数,以及超低的长期漂移特性,上一期我们讲的HP 3458A 数字万用表就使用了LTZ1000作为电压基准源。

嗯,顺便,他们使用了一块Xilinx生产的 XC7A35T FPGA作为整个系统的控制器,那块大底板上的35T就是这块FPGA的最小系统板。

银色的巨大铝块就是恒温腔了,它的底部塞了一块TEC(半导体加热/制冷片),同时配备了控制器,用以控制精密模拟电路部分的恒温状态。

前端电路

但这些都不是重点,重点是我们需要借鉴它的电路图!

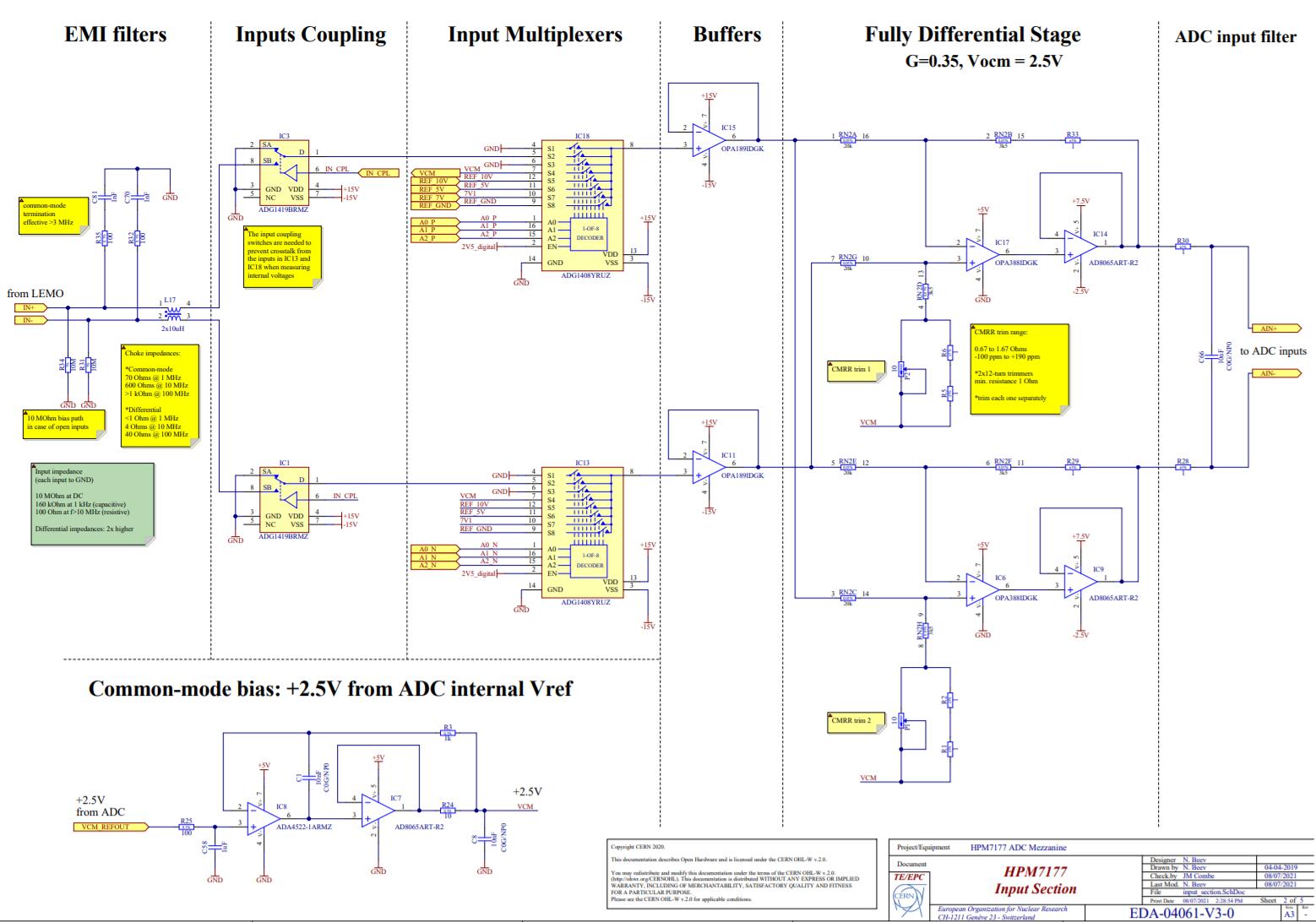

我们可以找到它的模拟前端电路,然后我们来分析一下——

信号流动的方向是从左至右,那么我们也这么来分析。

首先差分信号经由10M电阻接地、同时接了一个RC共模滤波器,然后接入了共模电感,这一部分主要是EMI滤波;

共模电感输出接入了2个模拟开关,这2个模拟开关的另一路输入是接地的,主要用于系统测试用。

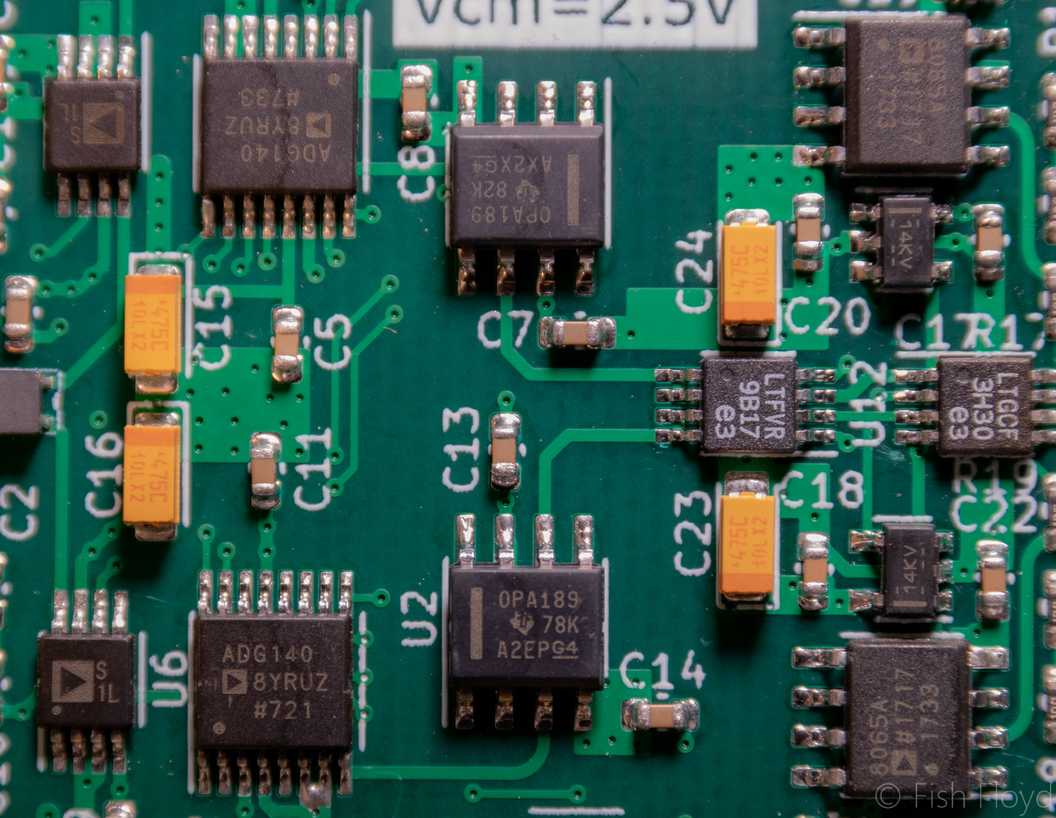

第一级模拟开关输出接入了第二级模拟开关输入,第二级的模拟开关是8选1Mux,除了输入信号接入了之外,还接入了很多的基准电压信号,这一级模拟开关主要用于为整个系统提供全量程的校准。(包括offset校准、INL、DNL校准)

像过火车隧道一样过了2级模拟开关之后,信号接入了一个电压跟随器。这个buffer所使用的运放型号是OPA189,我查了一下,它具有60TΩ的共模输入阻抗……我只能说逆天。如此之高的输入阻抗保证了信号在这一级缓冲之后不会有损失。

经过buffer后,信号来到了全差分放大级。乍一看还挺复杂,但拆分出来看的话,其实就是2个复合差动放大器,他们的输入端反相,然后输出差分信号相减,就可以得到2倍增益的输出。单个差动放大器的增益是3.5k/20k=0.175,然后经过输出差分乘以2,就是图上所标识的0.35了。

在这一级它使用了复合放大器结构,经过查阅数据手册我们就可知其原因——

第一级放大器OPA388属于高精度零漂放大器,但其增益带宽积较低,输出压摆率不高。而第二级放大器AD8065属于高速精密放大器,输出压摆率和增益带宽积都很优秀,将8065用作输出级可以增强这个电路的驱动能力,而OPA388作为前放可确保这个电路的零漂移特性。

当然,下面还为这个差分级提供了共模偏置,他使用了来自ADC内部基准源的2.5V电压,同时为其设置了CMRR调节电路,如果电阻匹配度不佳会导致电路共模抑制比降低,这2个电位器支路可小范围微调CMRR。

基准电路

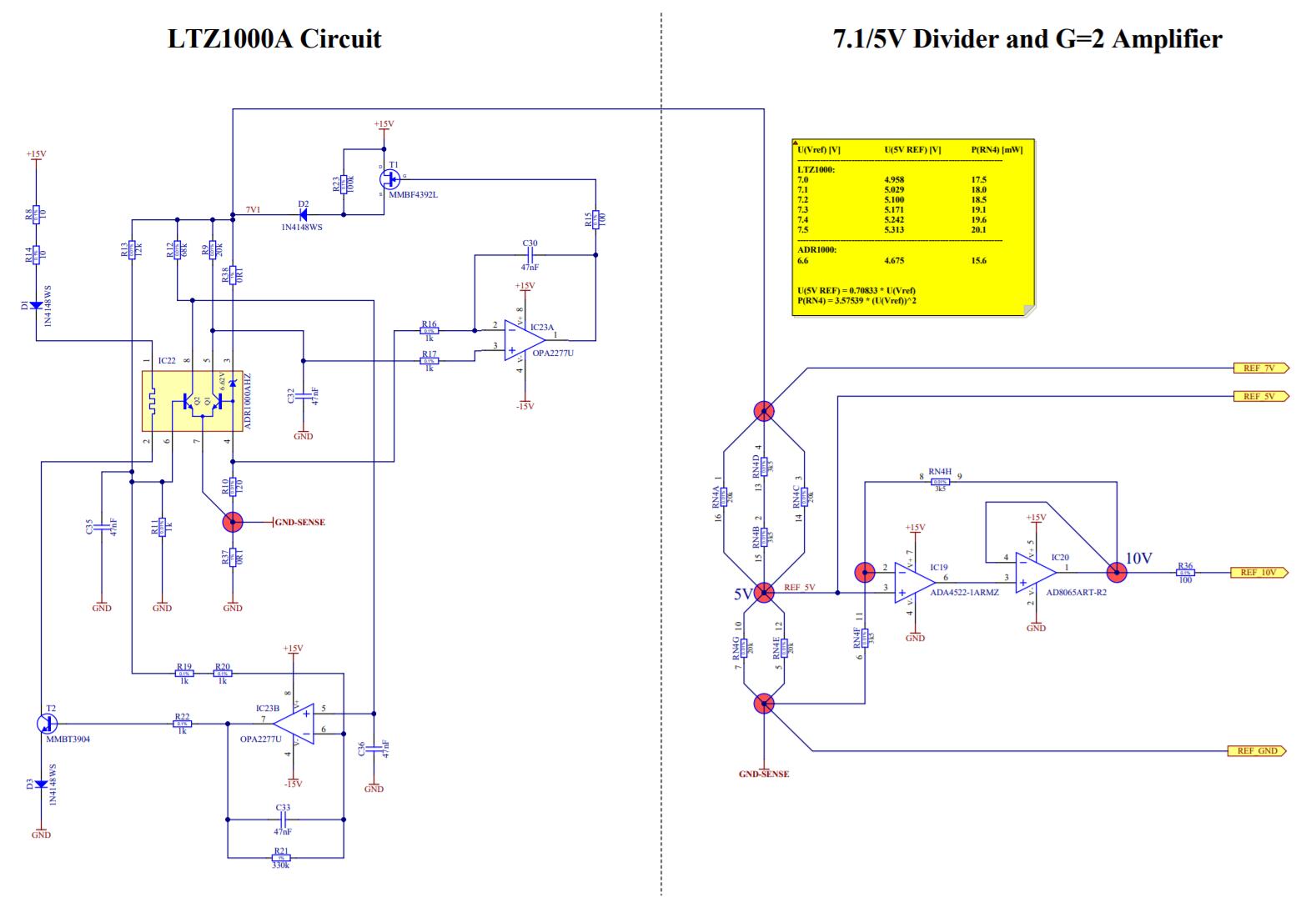

在基准这一块,它使用的LTZ1000内部是带有加热丝的(就是LTZ1000框框里面那一小段蛇形线),所以有些外围电路是用来做加热丝闭环控制的,我们暂时可以不用理会。

LTZ1000输出电压约为7V,它使用了分压电阻网络+放大器的结构,输出了5V、7V、10V 3个电压。其实也没啥好看的…

ADC电路

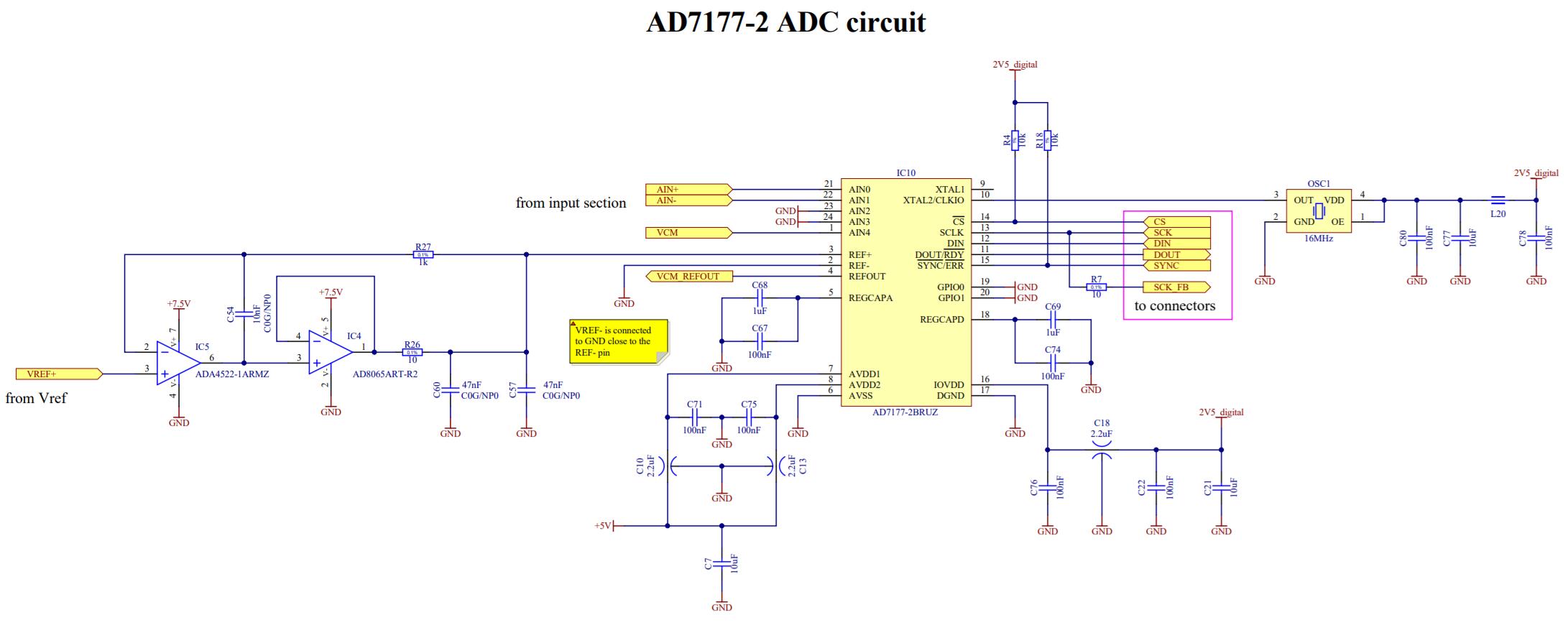

可以看到从左边输入进来的VREF电压经过一个精密复合跟随器和简单的滤波和退耦电路后接入了ADC的外部基准电压输入引脚。同时图上特别标注了一点,需要小心地设计基准电压信号路径和地。

然后剩下的就都是些AD7177-2的各种电源和配置电路了。在AD7177-2的供电网络(正5V模拟供电和2.5V数字供电)前我们都可以看到有0.1uF的退耦电容和馈通滤波器组合,这样的设计是为了最小化电源轨上的高频噪声对电路产生的影响。同时在时钟输入处,使用了一个16MHz的有源晶振,供电串联了高频电感。

信号路径(Signal Path)

至此嘛,最核心的模拟电路前端已经全部讲完了。我们做一张系统的框图,就可以大致把握整个系统该如何去设计了。

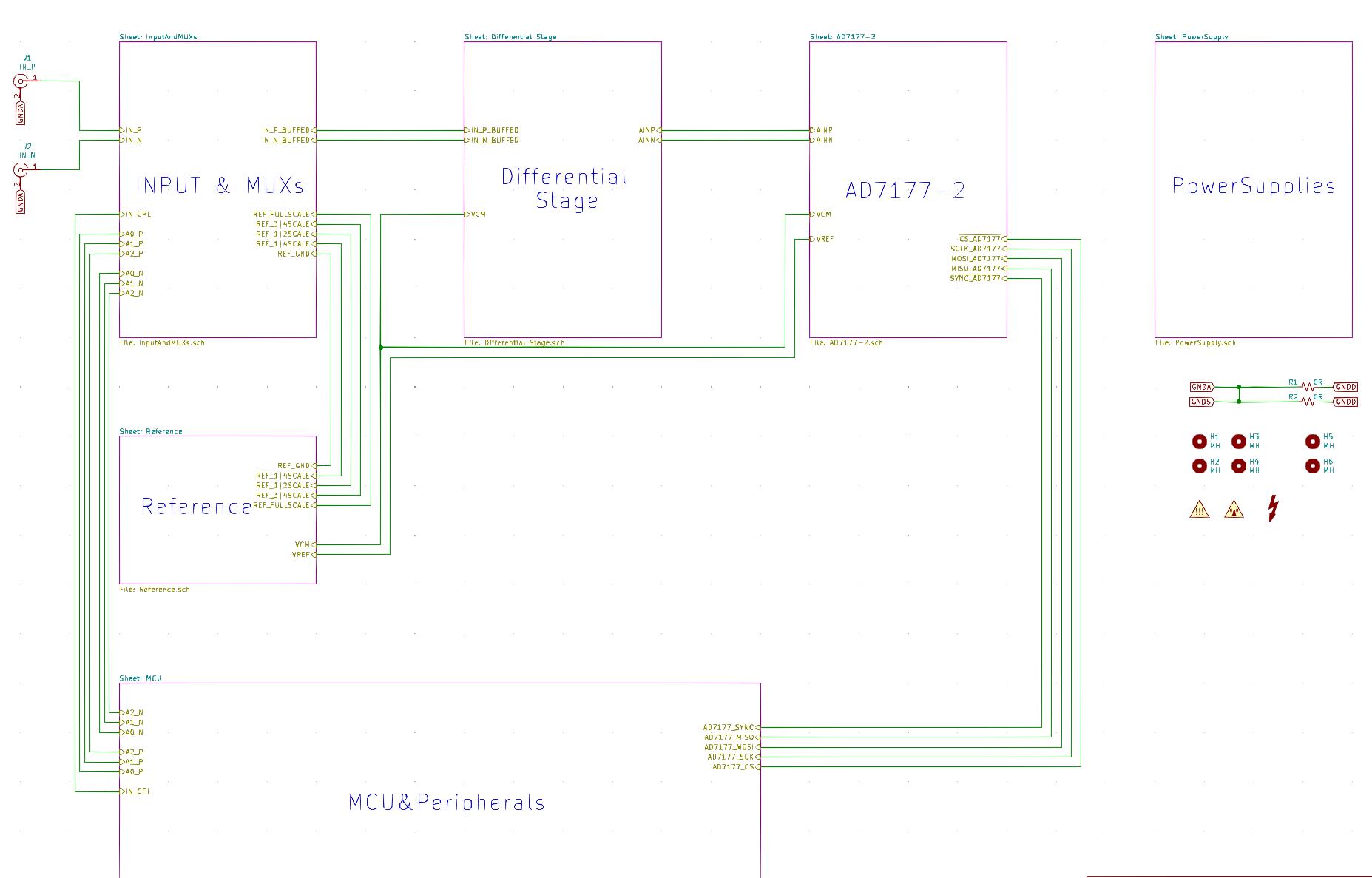

系统主要分为几个部分:

- Input & MUXs | 输入级与模拟开关

- Differential Stage | 全差分增益级

- AD7177-2 | 核心ADC及其外围

- Power Supplies | 系统电源分配网络

- Reference | 基准电压源及其外围

- MCU & Peripherals | 单片机以及外设接口等

老样子,还是用KiCad完成了Schematic Design和PCB Layout,在顶层电路结构图中我划分了整个系统的框图,还算是比较清晰吧——

设计理论 & 经验

这一节可谓是整个系统中的精华之一了。因为我自己造不了轮子,我用了现成的集成式ADC芯片,那么我现在还需要做的就是设计好精密小信号模拟前端和基准电压源的线路布局等。

因为这是一个典型的数模混合系统,在数字域会产生上MHz的高频噪声,而模拟域中 有用信号 的最高频率不过kHz,两者不在一个数量级上,不良的PCB设计会导致数字与模拟域互相干扰(主要是数字干扰模拟,老恶棍了),最终呈现出来的就是系统可靠性、稳定性下降,精度也将无法达到要求(高频噪声增高)。

以我的菜鸡水平,目前能想到的一些需要在设计过程中重点考虑的是:

- 整体电路布局划分

- 电源分配网络

- 电源与输入EMI滤波、抗干扰

- 完整地平面与星形接地法则

- 合适的电源退耦与馈通滤波器

- 运放外围元器件布局

我借助了ADI的众多文档,大致上算是完成了这些复杂的设计。虽然最后的效果不一定有多好。。。那么我就不长篇大论了,直接摆上我看完这些文档的总结经验吧~

去耦技术总结

请参考 MT-101应用指南

-

距离ic不超过2in(5.08cm)的地方放置一个10uF~100uF的大电解

这个电容的作用是充当电路的动态电荷库,从而使电路需要瞬态大电流时,电流无需通过带有更高寄生电感的电源引线,从离芯片更近的电容中直接获取能量。 -

再并联一个更小的(0.01uF~0.1uF)电容

这个电容的作用是将高频噪声短路,从而使高频噪声无法进入IC。 -

所有的退耦电容都应该使用尽可能短的连线连接到一大块 低阻抗地平面,以最小化引线电感

-

(可选的)在IC的电源引脚和电源总线之间串联一铁氧体磁珠,多半时间在调试时可以这样做,有如下好处:

定位系统中的噪声

将高频噪声隔离

避免该支路芯片内部产生的噪声传播到系统的其余部分

模数混合系统共地问题

请参考 MT-031应用指南

我认为这篇文章中最重要的一句话是: 没有任何一种接地的方法能始终保持最佳性能!!!

有股听君一席话,如听一席话的感觉.jpg

接地层的作用

- 去耦高频电流的低阻抗返回路径

- 将EMI/RFI辐射降至最低

- 将外部的EMI/RFI影响降到最低

- 可使用传输线技术(微带线/带状线)传输高速数字或模拟信号,需要可控阻抗

接地技术

- 星形接地(单点接地)

- 避免 "孤岛" 产生

- 避免接地层的相邻大面积区块间有薄弱连接

- 电源层和接地层 彼此相邻 可提供额外的层间电容,有助于电源的高频去耦

- 在物理上分离敏感的模拟元件与多噪声的数字器件,也可针对模拟和数字电路使用分离的接地层,避免叠可将两者间的容性耦合降至最低

- 多PCB系统中,在模拟/数字地间串联背对背肖特基二极管,防止插拔时产生的尖峰损坏敏感器件

- 多关注系统整体布局!

基准电压源

我使用了ADR4525这片电压基准源,数据手册在这

为了保证基准电压源能发挥最佳性能,需要考虑的因素有非常多。

在ADR4525的Datasheet中陈列了诸多影响基准源性能的指标和原因:

- 焊接热阻

- 环境温度

- 环境湿度

- 电源纹波

- 热致输出电压迟滞

- 长期稳定性

- 功率循环迟滞

其中有些参数我们是无法左右的,我们大致能把控的就是温度和湿度,还有电源纹波。

电压基准源的湿度敏感度

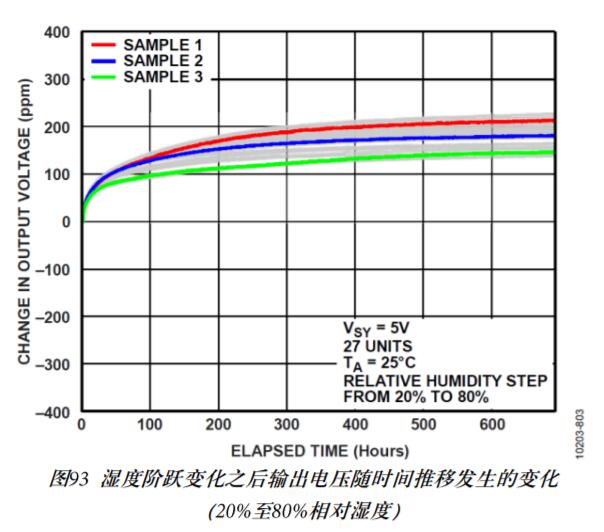

因为ADR4525采用SOIC塑料封装,湿气敏感度等级为MSL-1,符合JEDEC标准,但是从空气中吸收到封装的湿气会 改变裸片内的机械应力,从而使输出电压发生变化。如下图所示,相对湿度阶跃变化随时间推移对输出电压产生的影响。

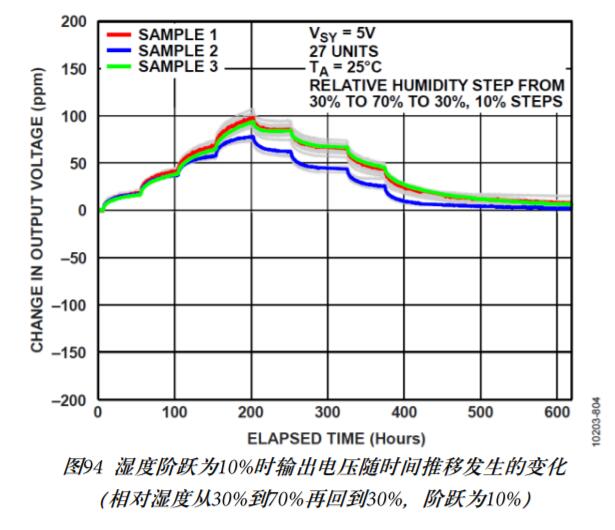

相对湿度从30%到70%再回到30%期间,每增加10%所产生的效应。相对湿度回到30%之后,输出电压将回到其起点。不过这将耗费一定的时间,在短期内带来的变化将会明显地改变整体系统的测量误差和精度。

塑料模具化合物会吸收水分。随着相对湿度的变化,塑料封装材料施加于芯片内部的压力会发生改变,这会导致基准电压源的输出发生轻微变化(通常约为 100ppm)。PCB板的材料可能会吸收水分并对芯片施加机械应力。合适的板材料和布局也至关重要。−40°C 至 125°C 的迟滞曲线PCB板布局对获取最佳稳定性至关重要。PCB板温度和位置变化以及老化程度都会改变施加于焊接到板上的元件的机械应力。FR4和类似材料也会吸收水分,导致电路板鼓起。虽然可以通过降低吸收率来延迟这种征兆,但即使采用保形涂层或电路板灌封也并不能完全消除这种影响。

同时应当省略基准电压源 IC 下面的电源层和接地层,以获得最佳稳定性。

基准电压IC的PCB布局

将IC焊接至PCB上时所引起的机械应力可能会导致输出变压发生偏移和温度系数发生变化。为了减少与应力相关的偏移影响,可以将基准电压源安装与靠近PCB短边附近或拐角处。此外,可以在器件两侧的板上开槽,以减小机械应力。更厚更小的电路板更硬,并且不易弯曲。最后在安装电路板时采取消除应力措施(如柔性支座)。

其他预防措施包括确保焊点清洁和PCB上无残留助焊剂,因为这些残留助焊剂将导致PCB表面导电性能发生变化,在电路中会增加漏电流路径。

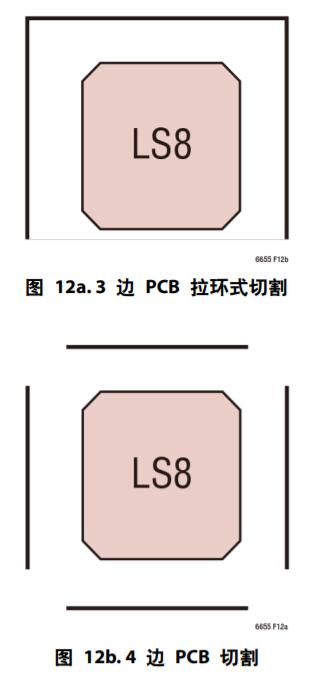

可以运用下图所示的三边拉环式切割PCB板,这将显著降低IC上的应力(如应用笔记-82所述)。为了获得更好的性能,下面还有四边切槽PCB板。切槽应尽可能长,拐角尺寸只需足以容纳走线。现已表明,以这种方法设计的PCB板在相对湿度变化约为60%时,湿敏度可降低至 35ppm 以下。将基准电压源安装在电路板中心位置附近,并在四边切槽,可以将湿敏度进一步降低至 10ppm 以下。PCB板切槽的另一个优势是可将芯片与周围电路热隔离。这有助于减少热电偶效应并提高准确度。

关于更多电压基准源的相关文献,我还参考了下列:

为何基准电压噪声这一指标如此重要?

请参考 Analog Dialogue 第54卷第2期

基准电压源原理

请参考 MT-087应用指南

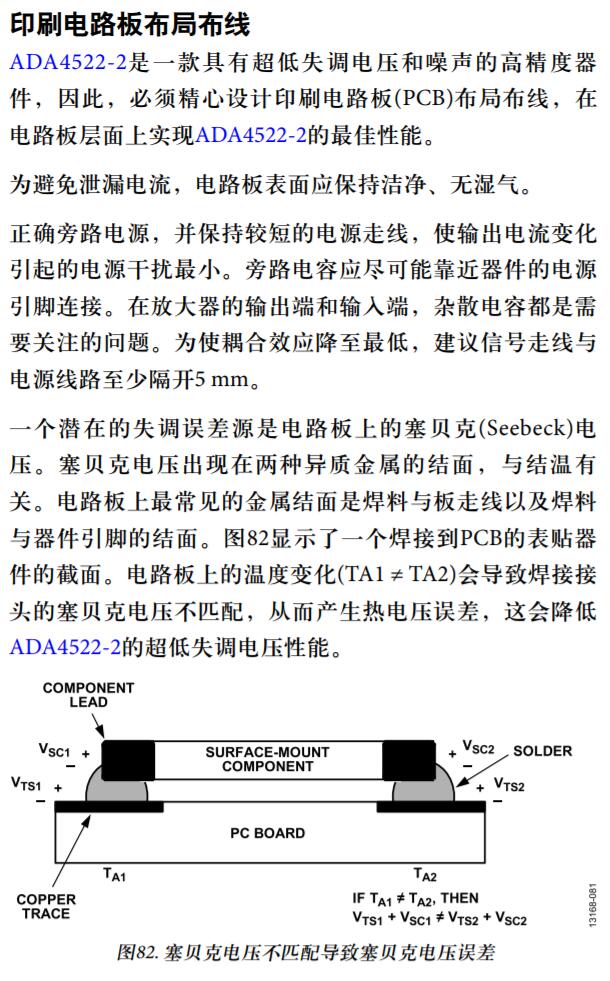

精密运算放大器外围布局布线

请参考 ADA4522的数据手册

考虑的问题如下:

- 避免泄漏电流,保持PCB表面洁净干燥

- 正确旁路电源,保持短连线

- 考虑外围阻容的热均衡,避免 Peltier-Seebeck电压(其实就是热电效应) 降低失调性能

Layout!

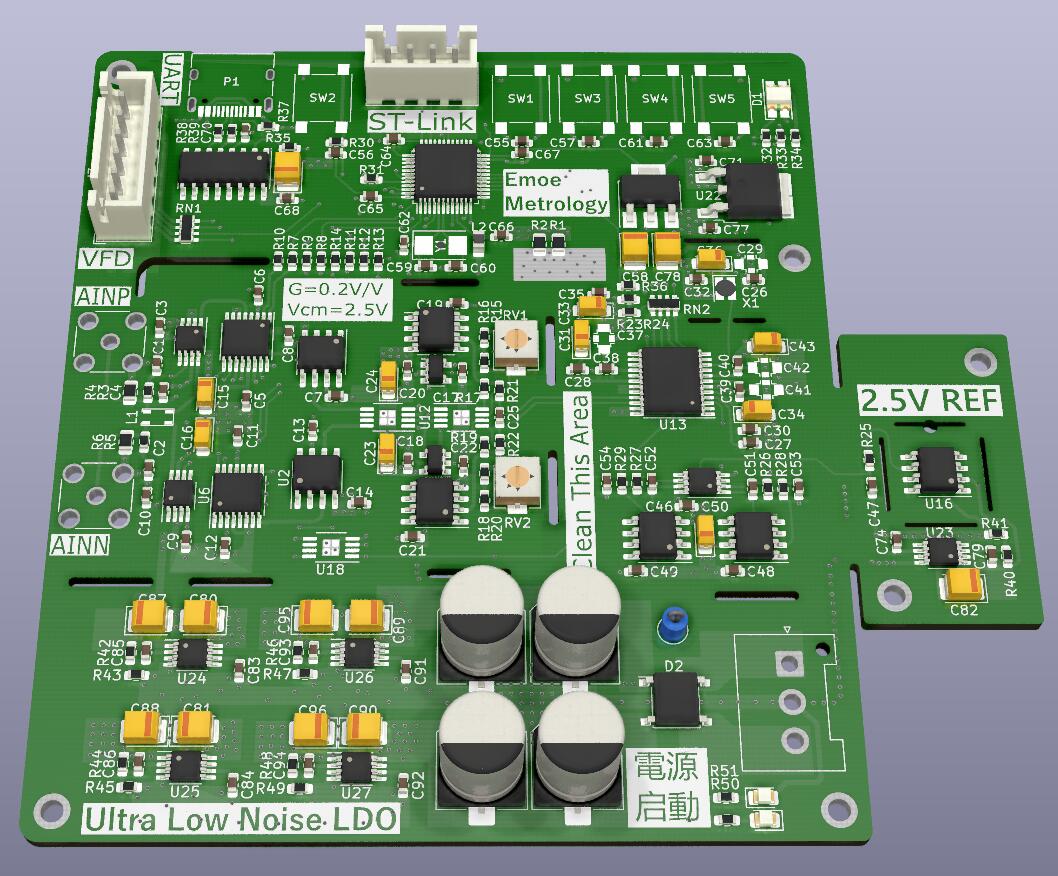

我就来献献丑吧= =

还是用KiCad画的,4层PCB,交由JLC免费打样,FR-4基板,厚度1.6mm,TG值130,最低端的板材。打完样之后想了想,其实我应该加点钱上个好一些的板材的。。。不过原型验证阶段嘛,先跑起来再说~

PCB Editor View:

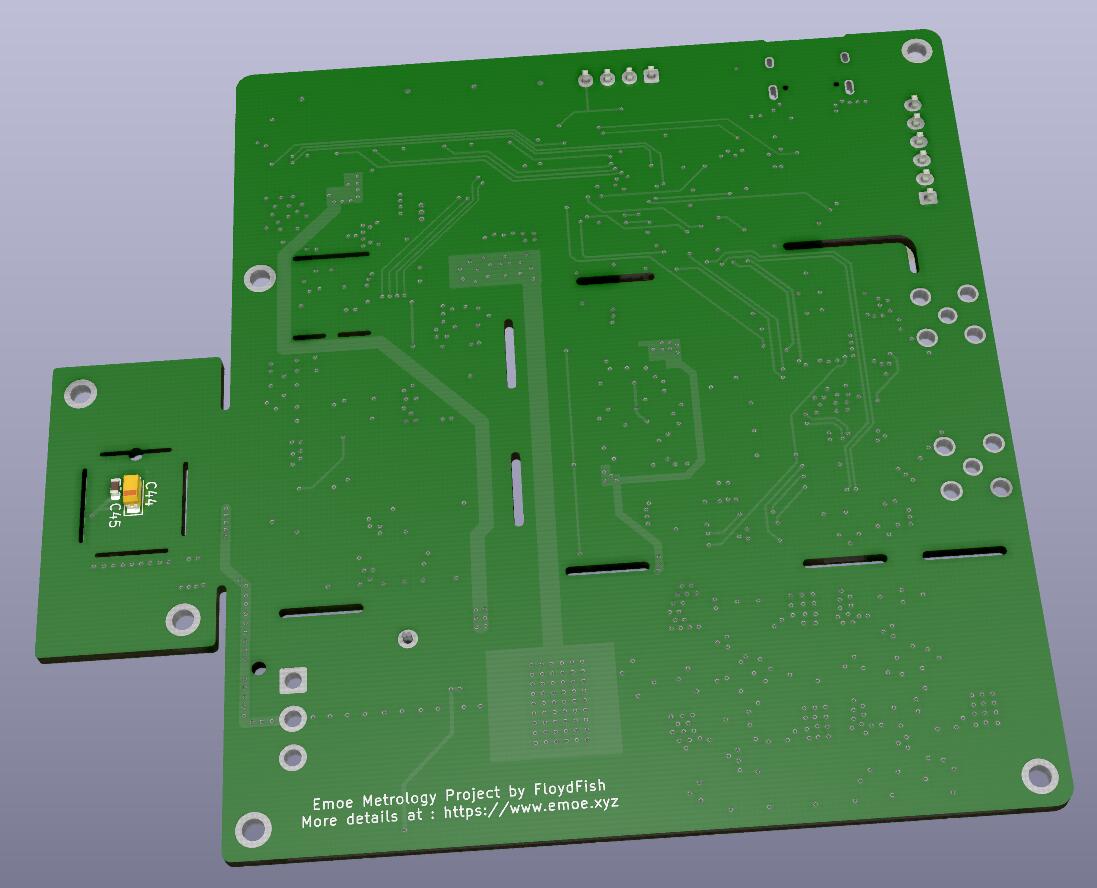

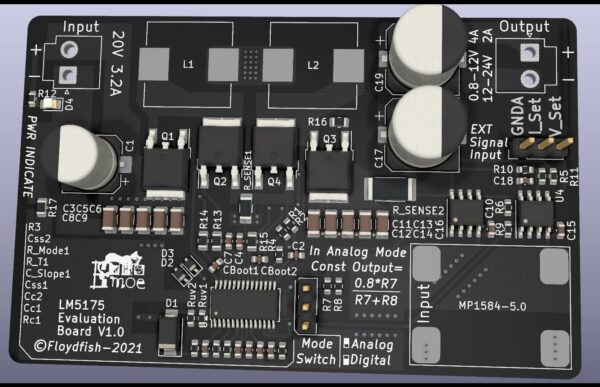

光追渲染图(缺了几个3D Model,问题不大。):

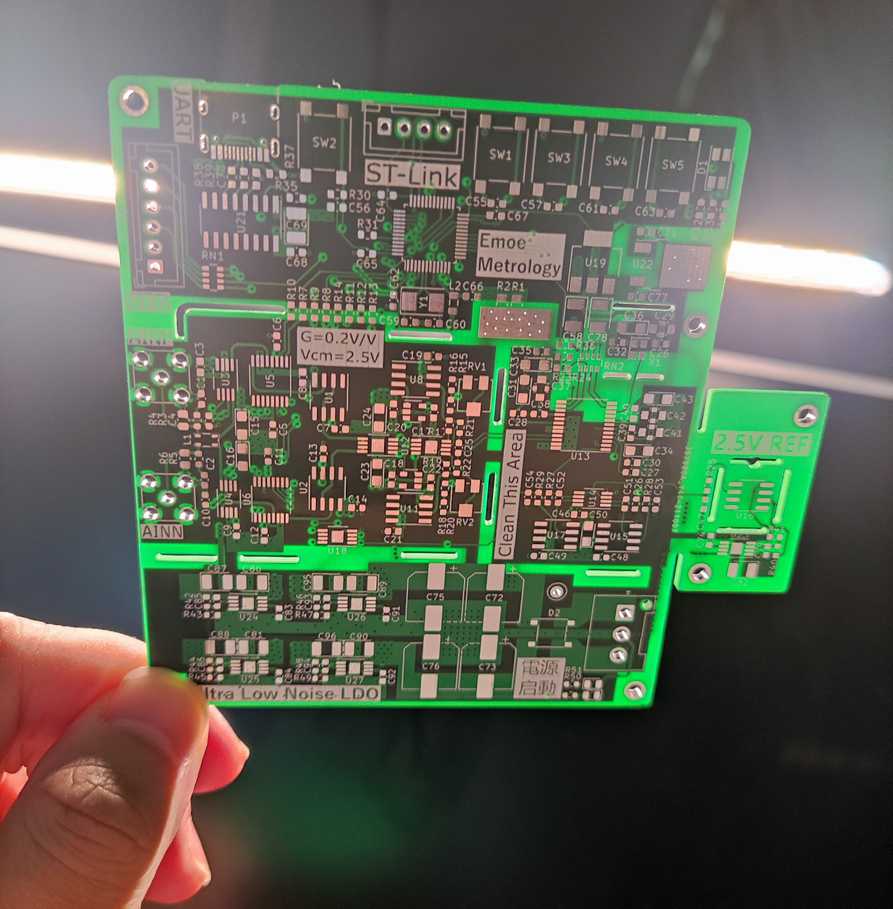

然后是一点实物图:

嘿,我觉得从板子背面看内层的电源轨走线,还挺好看的。

好啦,这期就到这里~接下来我们即将进入激动人心的测试和二次开发环节!敬请期待——

![[魔法电路]-电路中的噪声](https://www.emoe.xyz/wp-content/uploads/2021/11/6-600x313.jpg)

![Read more about the article [综合项目]01-波形发生器设计](https://www.emoe.xyz/wp-content/uploads/2020/09/launchpad_t-300x178.jpg)

激动人心的测试和二次开发环节,出来了吗?

请问,PCB的设计楼主是怎么这么快速学会的,感觉设计的还不错,起码比我好得多哈哈

PCB设计感觉很难说“学会了”,因为评价的标准不一。仅仅把线连上、走通和让电路发挥最佳性能的Layout难度是天壤之别😂

只是把线连上的话,学会EDA软件操作就行。但要设计性能优异的PCB,需要长期的学习和项目积累。

首先设计者肯定要在掌握基本电路和电磁场基础前提下,学习一些信号完整性和电源完整性基础知识。熟知所设计的电路特性:哪里走功率,哪里是微弱信号需要特殊处理,哪里是可能的辐射源,哪里是可能的EMI受害者,处理特定类型的信号(微小信号、射频、时钟、电源等)应该怎么处理…诸如此类,然后分别采取不同的设计规则或措施确保Layout正确

比如本文所画的PCB,我过了半年再来review的时候发现了很多设计不合理的地方,比如部分IC工作时温升较大,与其他IC热隔离不佳,容易影响其他IC工作点;电源、模拟和数字的布局顺序如果调换一下可能会更好