本文目录

噪声放大器(Noise Amplifier)构建指南

在精密模拟信号链中,我们肯定不希望 噪声(Noise) 在我们的电路中跑火车。但想要验证其存在并对其进行精确测量,却又不是那么容易的事情。

在开关电源(DC-DC)中,我们通常会测试其输出的 纹波(Ripple),而这通过示波器就可以很容易地测量到,因为开关电源中的纹波的数量级通常在 10mVpp 以上,示波器努努力是可以测量的。

一.示波器的极限

然而,示波器是有极限的,因为通用示波器(我瞎编的名词)为了达到高带宽,通常需要选择采样率较高的ADC(GSa以上),而这意味着ADC的分辨率不高(8至12位居多,少数16位顶天了)。而ADC的分辨率就直接决定了它所能量化的模拟信号的大小极限——低于ADC LSB的信号都无法被准确量化,全部淹没在滚滚红尘(指示波器前端底噪+ADC底噪)中……

当然,你也可以选择高位数的ADC去搭建专用的采样系统。这种产品当然是有的咯,比如音频谐波分析设备,有高达32-bit分辨率的ADC和上百kSa的采样速度(对就是咱熟悉的Hi-Fi)。这样的系统的SFDR(无杂散动态范围)可达到100dB以上,但是其最高只能采集几十kHz的信号,奈奎斯特和香农两位大佬也为这种方法判了死刑…(指奈奎斯特采样定理)。

二.另辟蹊径

这时候有人可能就要问了,那些模拟芯片大厂的芯片数据手册里那些噪声数据是怎么测出来的呢?

人类肉眼看不见树叶上的细胞,但是借助 显微镜 这一工具我们便可洞察生命的奥秘。同样的,对于我们难以接触到的微弱噪声,我们可以 放大之 !

放大之后的信号,达到了示波器的测量范围内,我们就可以安心地将它送入示波器,观察它的时域波形了。同样的,我们也可以将其喂给频谱仪,看看它的频域特性。

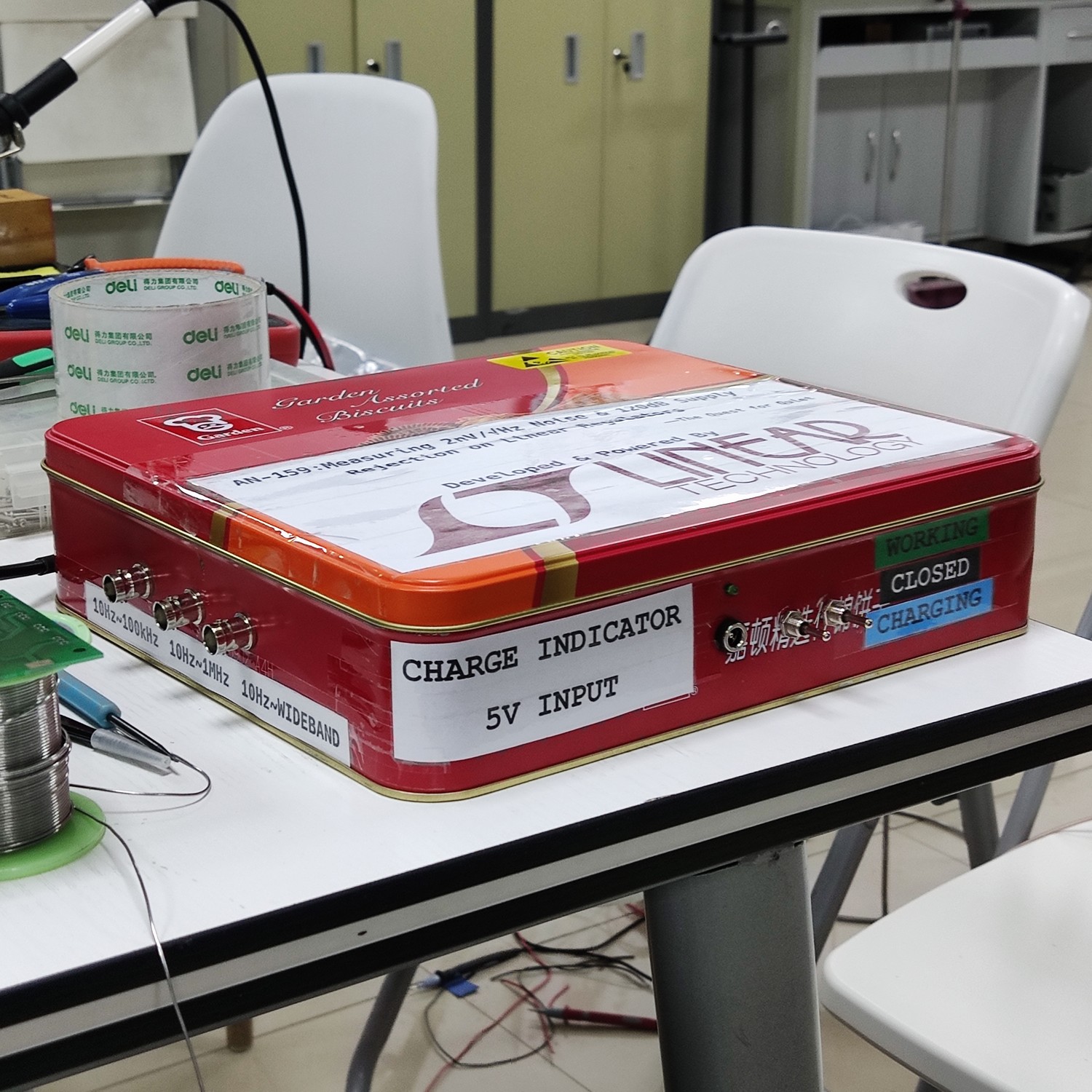

这个饼干盒很有毛子的味…万年风雪!

2.1-放多大?

通常,对于10mVpp的信号,我们无需放大,我手边几个示波器的底噪水平通常在500uVrms~1mVrms之间(咱也没钱接触更贵的,有木有老板借一台玩玩233),所以我们划定这样一个范围: 噪声rms值小于10mVrms的,都需要放大。而对于更小的信号,比如uV、甚至nV级别的信号,我们可能需要极高的放大倍数才能将它们放大至示波器的观测窗口内。

2.2-放大器的挑战

当然,这一路上总不可能一帆风顺。使用放大电路来放大噪声的一个致命问题是: 放大器自身的输入噪声也将跟随信号链被放大。如果我要测量的噪声水平是1uVrms,而我的放大器输入本底噪声水平为5uVrms,放大器放大倍数为10000倍,那么在输出端我们能观测到 10000\sqrt{1^2 + 5^2}=50.99 mVrms 的输出信号。很显然我们要极力规避这种情况出现。放大器过大的底噪将让我们的测量结果不可靠。

所以第一个挑战是,需要极低噪声的前端放大级,并且得保证其噪声水平远低于我们想要测量的最小信号。

第二个挑战是,日益复杂的电磁环境会让我们的电路 夜不能寐。在周围空间中充满着无线电波和电磁干扰的时代,我们不得不考虑采取特殊的屏蔽措施来隔绝这些电磁干扰。你可能又要问了,我见你平时做电路也妹用这种屏蔽结构啊?——那是因为我平时做的电路对uV级别的高频感应、耦合噪声并不敏感,而噪声放大器不允许哪怕一丁点的感应、耦合噪声进入电路中。

第三个挑战是,超级纯净的供电电源(这一环倒是简单些)。因为构建放大器的电路并不能完全抑制电源轨上的纹波和噪声,所以任何形式的开关电源都是不可行的。最好的办法是用 电池。后续我们详细展开。

第四个,也是最重要的之一,是谨慎选择构成电路的元器件、PCB Layout、以及屏蔽结构的搭建。

总之,这是一项不那么容易的工作。想要达到最佳效果,需要极其谨慎地对待任何一个环节。

三.资料准备

主要分为ADI(Linear Technology)的应用指南、模拟对话、技术文章,以及一些相关专业书籍和参考文献;

- AN-83:Performance Verification of Low Noise,Low Dropout Regulators

- AN-124:775 Nanovolt Noise Measurement for A Low Noise Voltage Reference

- AN-159:Measuring 2nV/√Hz Noise and 120dB Supply Rejection on Linear Regulators

- AN-347:Shielding and Guarding

- LIGO:Resistor Current Noise Measurements

- AN-6206(MAXIM, 现在也变成ADI的了…):SIMPLE, EFFECTIVE METHOD AND CIRCUIT TO MEASURE VERY-LOW 1/F VOLTAGE REFERENCE NOISE (< 1mVP-P, 0.1HZ TO 10HZ)

- [魔法电路]-电路中的噪声

- MT-048:Op Amp Noise Relationships: 1/f Noise, RMS Noise, and Equivalent Noise Bandwidth

- Mu-Metal Brochure

- K&J Magnetics: Shielding Materials

- Analog Dialogue:无烦恼,高增益:构建具有纳伏级灵敏度的低噪声仪表放大器

- Analog Dialogue:该噪声会让您夜不能眠

- Analog Dialogue:对电阻使用的经验法则说不

- 无烦恼,高增益:构建具有纳伏级灵敏度的低噪声仪表放大器

那么让我们开始这项激动人心的工作。

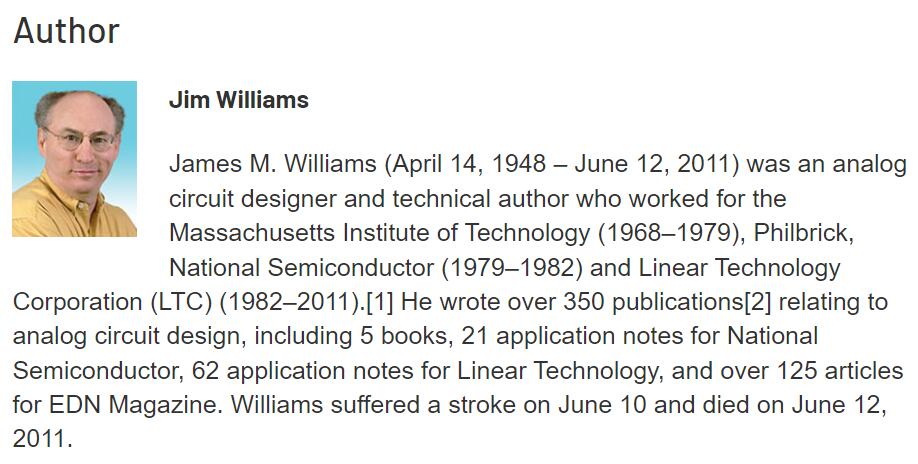

四.Jim Williams的工作-AN124

Jim Williams是一位具有传奇色彩的模拟电路工程师,永远缅怀。

2009年7月,Jim Williams发表了 Application Note 124:775 Nanovolt Noise Measurement for A Low Noise Voltage Reference,文章的副标题是 "Quantifying Silence" (量化寂静),有股诗人的气息🤔

这篇笔记中,为了测量 LTC6655 精密基准电压源芯片的输出噪声,Jim搭建了一个 0.1Hz至10Hz 的噪声放大器,精确地测量了LTC6655的输出电压噪声为775nVpp(0.1Hz~10Hz)。以下是Jim的电路图。

4.1-设计思路

我们来看看Jim是怎么设计这种精密小信号放大电路的:

- 使用1300uF的液态钽电容(经过特殊挑选出的具有极低漏电流种类)和极低噪声的1.2k电阻器构成0.1Hz的高通网络,用于隔绝DC及交流信号耦合;耦合线路完全屏蔽以隔绝任何可能的电磁干扰。

- 使用 噪声极低 的JFET作为输入级,运放A1负责稳定Q1和Q2的直流工作点,JFET和A2构成了具有10000倍电压增益的复合超低噪声放大器。(增益由100k电阻和10Ω电阻设定)。

- 整个低噪声放大前端被放置于金属屏蔽罩中,并且使用干电池供电,因为干电池具有极低的噪声(uV水平)。

虚线框以外的电路是后级信号处理。噪声信号经过10000倍放大之后,已经不惧怕微弱的电磁干扰信号了,所以无需做屏蔽处理,进而可以转为常规放大器、滤波器设计思路。我们重点关注虚线框内的部分。

整个低噪声放大电路被放置于金属屏蔽腔内。利用”法拉第笼”效应屏蔽外界电磁干扰信号

因为对于电压基准源,主要关心它的低频噪声,也就是 1/f噪声,所以Jim设计这个放大器时仅仅只提取了0.1Hz到10Hz范围内的噪声进行放大处理。做好屏蔽、挑选合适的元器件、应用适当的布线技术,这样一个低频噪声放大器就出炉了~

4.2-更高带宽

随着技术进步,更牛逼的新器件如雨后春笋般诞生。其中就有LT生产的几款 超高PSRR(120dB)、极低噪声(0.8uV)的低压差线性稳压器(LDO) —— LT3042<3045\LT3094等型号LDO。

为了测量这些LDO的噪声水平和在宽频率范围内的超高PSRR,Jim之前为低频测量所设计的噪声放大器已不再适用,需要新的高带宽噪声放大器才能满足我们的需求。

五.20uVrms宽带噪声测量-AN83

在2000年,Jim和Todd Owen攥写了 Application Note 83:Performance Verification of Low Noise,Low Dropout Regulators,副标题是 "Silence of the Amps"(电流之静)。

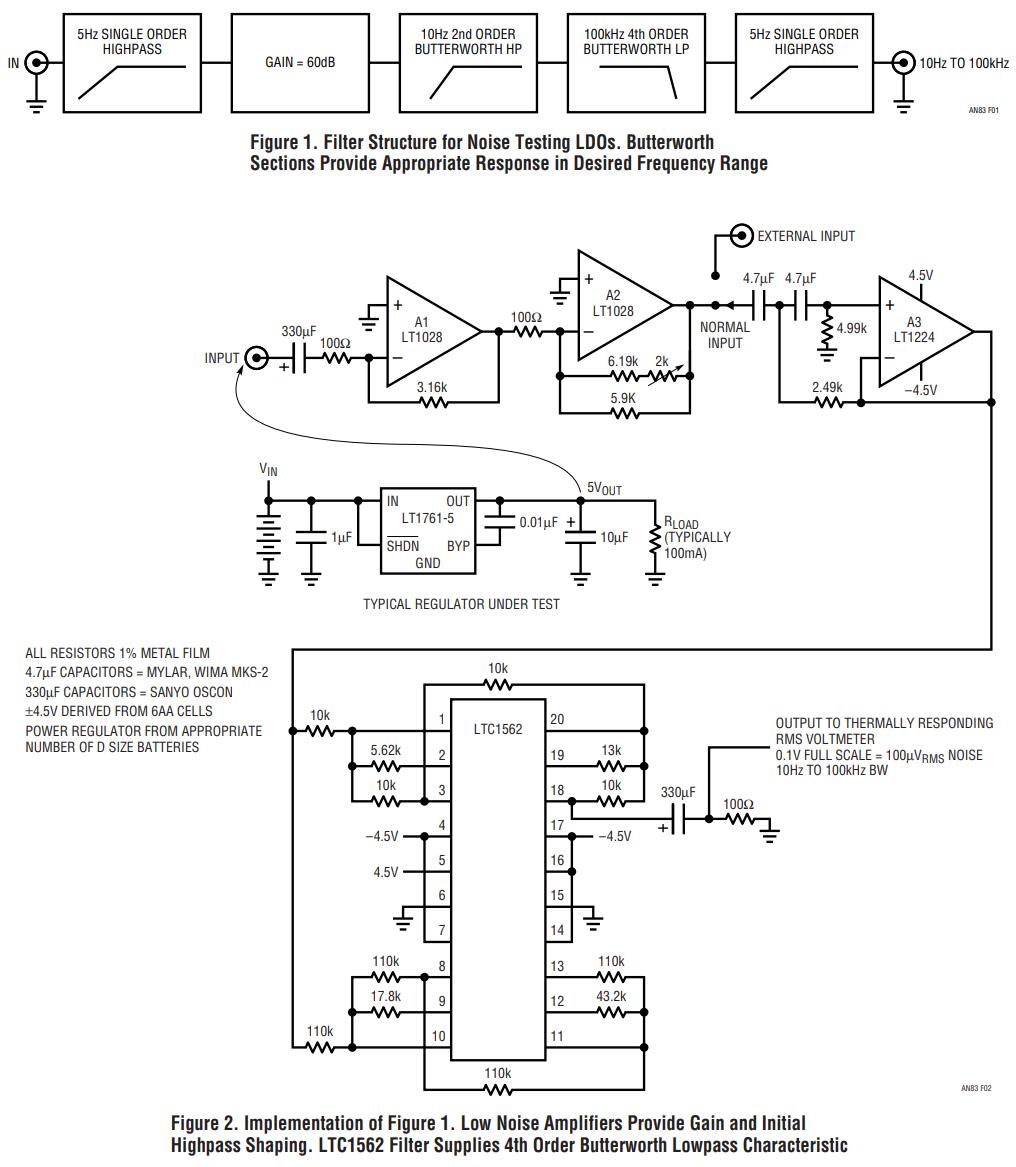

AN-83电路结构及电路图

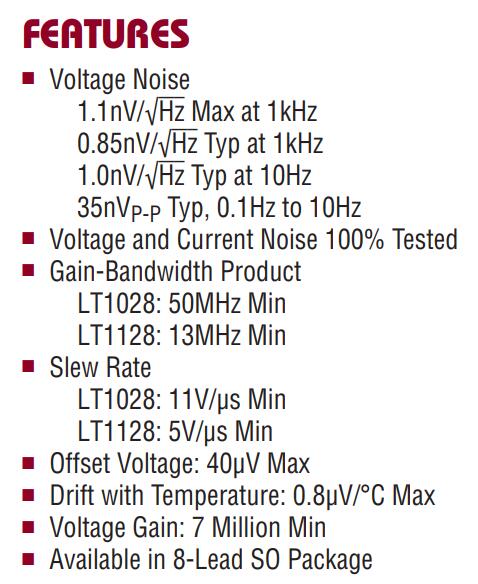

这个电路使用的LT1028是极低噪声高速运算放大器,使用2个LT1028单元构建了1000倍电压增益放大器,每级增益约30多倍,具体参数如下:

其GBW为50MHz,那么对于100k的信号来说30多倍电压增益肥肠合适。但对于更高带宽(比如MHz),这个电路仍然具有局限性。并且,这个电路的设计目的是测量20uVrms的噪声,电路的本底噪声(Noise Floor)为4uVpp(0.5uVrms),本底噪声贡献的测量误差不大,所以可以满足测量需求。

但来到0.8uVrms的领域,0.5uVrms的本底噪声就不可接受了。

六.0.8uVrms宽带噪声测量-AN159

为了测量0.8uVrms的噪声,我们需要噪声放大器的输入级拥有更低的输入噪声。

Todd Owen和Amit Patel为此攥写了 Application Note 159:Measuring 2nV/√Hz Noise and 120dB Supply Rejection on Linear Regulators,副标题是 "The quest for quiet"(寻求宁静)。

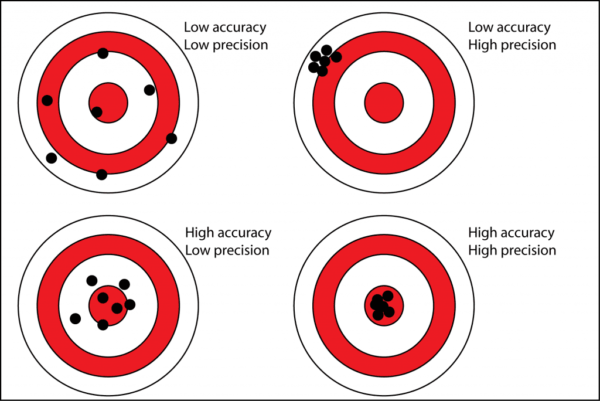

要测量小于1uVrms的噪声是一项 挑战。

假设在10Hz到100kHz的频带内噪声是1uVrms,这等效为 3.16nV/√Hz 的噪声密度(假设为白噪声),这个水平等效于一个 625Ω电阻 的热噪声!要在这个电压水平下测量噪声并达到5%的精度,噪声放大器的输入噪声必须达到 1nV/√Hz 的水平。如果要达到1%的测量精度,噪声放大器的输入噪声甚至要达到 450pV/√Hz 的水平。

6.1-设计考量

在我们对噪声放大器的本底噪声应该是多少心里有数了之后,我们要想想——需要测什么?

通常我们会测量10Hz到100kHz的宽带噪声,这个频段包含了音频频带,以及射频传输的基带数据边带。在锁相环(PLL)和高精确度仪表电路中,我们需要测量1MHz及以上的噪声水平。所以我们需要超越之前的所有工作,将测量的界限拓展至MHz。

如何提取特定带宽内的信号呢?当然是用滤波器咯。但是滤波器并不能保证对于不想要的信号有100%的衰减,所以我们可以选用高阶的butterworth滤波器,这样即可以保证通带平坦度,也可以使滤波器的频率特性尽可能地接近完全截断的"砖墙式"响应。(通带至阻带的快速衰减)。

当然,滤波器的等效噪声带宽也是我们需要考虑的:2阶低通ButterWorth滤波器的等效噪声带宽是 1.11fH,带来的误差过大;4阶低通ButterWorth滤波器的等效噪声带宽是1.026fH,约给最终结果带来1.3%的误差,可以接受。当然,更高阶的Filter会使误差进一步减小,但是增加的器件和设计成本不合算。4阶滤波器的误差与输入参考噪声引入的误差相耦合,表明在5%以内的测量要求放大器的输入参考噪声贡献不超过1%的最大误差。

同样地,增益大小也是我们需要仔细斟酌的。如果增益太低,测量仪器(示波器、频谱仪)的本底噪声将混入输出结果,误差就起飞了,而且输出信号如果小于仪器的底噪,那根本看不到结果。。。综合考量之后,选择了80dB的电压增益值,也就是10000(10k)倍。0.8uVrms的噪声信号经由这个电路放大后,输出将达到8mVrms。

6.2-系统架构&电路图

经过一番设计与调查,我们可以得出这样一个新一代噪声放大器的系统框图:

第一级为0.5Hz高通滤波器,同时发挥了隔直流的作用。

第二级为超低噪声的前放,增益设定为25。这一级需要使用特殊器件来实现。

第三级是5Hz高通滤波器,同样也能隔直流,所以前放的直流误差无关紧要。

下一级又是一个增益单元,增益为20,但是这里不再对噪声有过高的要求,因为此时输入噪声已经被放大了25倍,这一级的噪声只要不太离谱,所贡献的总误差就不会太大。

在经过10Hz的2阶SK高通滤波器后,又是一个20倍增益的增益单元。经过这一级的放大后,电路总增益达到了80dB(25x20x20=10000)。

然后对应地使用缓冲器和滤波器,提取出我们感兴趣的信号频段,作为不同的输出。

具体的电路图如下所示:

输入级的RC值 必须 谨慎选择。这里用的是680uF和499Ω电阻的组合(0.5Hz高通)。电阻值必须很低,不然输入级的偏置电流会导致过大的DC误差,致使前放饱和。但如果电阻值太小,为了实现0.5Hz的高通滤波器,电容值相应地就得变大,太大的电容也难以接受。小电阻也会让这个RC滤波器成为待测设备(LDO)的频率补偿网络的一部分,改变测量的结果。

6.2.1-Critical Stage!

该电路的输入级要求非常严格。它需要在提供 高带宽(MHz级别) 下的 高增益(G=25) 的同时保持 极低的输入噪声(450pV/√Hz)。常规的运算放大器已经不能满足设计要求,即使是地球上最低噪声的运算放大器——AD797(0.9nV/√Hz,GBW=50MHz)都不能满足这个需求。

幸运的是,还是有解决办法的。根据Jim Williams之前的工作(AN-124, 775nV那篇),使用一对精确匹配的差分晶体管对来驱动运放的输入,既可以实现高带宽下的高增益,又能保持极低的输入噪声水准。以大约80的增益运行差分对意味着晶体管的噪声占主导地位,所以运算放大器的噪声不是主要因素。

超低噪声输入级由2对 THAT300 匹配晶体管并联组成(降低输入噪声,原因见下),跟随一个LT1818组成总增益为25的低噪放大级。THAT300是4个被封装在SO-14封装内的精密匹配晶体管,其Vbe差别在500uV内,输入噪声典型值为 800pV/√Hz。因为需要较高的增益带宽积,选择LT1818作为放大器。

将多个输入单元并联可以有效降低本底噪声。放大器电路并联时,噪声水平会随并联数量下降,N级并联可使噪声降低 √N 倍。2对晶体管对并联可将噪声降低至800pV/√Hz,然后通过将4个完整的输入级并联在一起,进一步将输入噪声降低2倍,达到400pV/√Hz。

紧跟着的是330uF和100Ω电阻的串联,可以移除前级放大器中产生的任何直流失调误差。同时他也提供了5Hz的高通滤波,有助于建立整个系统的频带响应。所有的4个输入级并联相加,输入下一级20倍固定增益放大级。由于微弱噪声已经被放大25倍,次级放大器的噪声所带来的影响就不是那么重要了。

10Hz 二阶高通滤波器是一个简单的单位增益 Sallen-Key 结构滤波器。同样的,这一级也有着交流耦合,能够消除任何直流误差带来的影响。信号放大链中的最后一级是一个简单的反相放大器。因为前面的元器件都存在或多或少的误差,所以这一级采用了可变增益设计,可以用电位器微调这一级的增益,范围是15-25。在这一级过后,信号分为3路,分别送入单位增益缓冲器、1MHz截止频率4阶ButterWorth滤波器、100kHz截止频率4阶ButterWorth滤波器,分别提供10Hz-宽带输出、10Hz-1MHz带限输出、10Hz-100kHz带限输出。

6.2.2-选择合适的元器件

对于任何电路,选择合适的元器件都是至关重要的。在超低噪声测量领域,更是如此。在噪声放大器的设计中,低噪声输入级是最为重要的,它直接决定了整个电路的底噪水平、测量精度和性能。当解决了输入级后,设计后级电路可谓 "如释重负"。输入级的RC滤波器元件选择更是重中之重。

电阻的选择没有什么争议,因为要确保极低1/f噪声水平,所以需要选用金属膜电阻。电容则显得更为重要。在Jim之前的AN-124中,为了确保极低1/f噪声,使用了一个液态钽电容,并且经过人工挑选,找出了泄漏电流最低的一个。当测量频率下降至0.1Hz时,这些特性至关重要。但是对于10Hz到宽带噪声,我们可以选择一些成本稍低些(便宜多了,液态钽电容我搜了一圈,都买不到…)的钽电容。但是有一点,输入耦合电容绝对不能使用 多层陶瓷电容,因为它们本身具有 压电陶瓷效应,若电路板有些许震动,电容内部将会产生额外的噪声。虽然这些噪声不大,但对于噪声放大器来说却是致命的存在。另外,陶瓷电容的电压效应(容量随着电容两端的电压发生变化)将会改变RC滤波器的截止频率,从而导致测量带宽误差,这也是我们不希望看到的。钽电容或铝电解电容非常便宜(相对的),而且没有明显的压电陶瓷效应和电压效应。更昂贵的电容比如聚对苯二甲酸乙二酯薄膜电容也可以考虑,但是这种电容不好买而且非常贵,所以打咩打咩。

所以,陶瓷电容pass,液态钽pass,聚对苯二甲酸乙二酯薄膜电容pass,剩下钽电容和铝电解电容。虽然钽和铝电解电容相比之下有更高的噪声水平,但它们不对机械振动敏感,容值不随偏压变化,所以它们是低成本下的最佳选择。在此我们选择标准钽电容,并且使用多个钽电容并联,一是可以拥有更高的耐压,二是可以达到需要的容量(毕竟还挺大的,680uF),并且多个并联也可以利用统计平均(跟之前的运放单元并联降噪原理一样)来降低电容带来的噪声。

同样的,在前放和第二级放大器之间的耦合也基于同样的原因,选择了钽电容作为耦合电容。即使输入噪声已经被放大过了,但陶瓷电容的压电效应还是会产生显著的噪声从而导致误差,所以不用陶瓷电容。

当然,输出级的电容选择就比较随意了,可以选择低成本的贴片陶瓷电容,同时输出信号几乎没有直流偏置,所以陶瓷电容的容值接近我们的期望值。在第一级放大器中300pF的补偿电容、滤波器中的电容都需要选用C0G或NP0材质,亦或是稳定性更高的聚对苯二甲酸乙二酯薄膜电容,因为采用这些电介质的电容几乎没有压电效应和直流偏压导致的容值变化,同时温度稳定性也更好。

整个电路的电源也是至关重要的。因为电路中所有的有源器件都不具备无限的电源抑制比(PSRR),所以电源轨上的任何噪声都会耦合进电路并带来测量误差。在AN-159里,使用了碱性干电池作为电源,因为碱性干电池具有极低的噪声并且避免了在整个设备中可能存在地环路(可能会影响电路正常工作)。

6.2.3-实际电路的限制

考虑到噪声放大器的增益是如此之高(80dB,10000倍),我们必须估算它可接受的输入范围是多少。

首先考虑输出级运放的输出能力,LT1365并不能轨到轨输出,如果采用±4.5V电压为电路供电,它能输出的电压摆幅约为±3.5V,意味着输入信号超过350uVpp就会导致输出饱和。设想最坏的情况,假设波峰因数为10的高斯白噪声,仅仅70uVrms的该噪声就会让输出达到最大。

钽电容的正确偏压也是必须要考虑且在实际使用时要遵守的。对于输入隔直电容,晶体管几乎工作在地点位,所以如果待测试的源是正电源,那么需要将输入耦合钽电容的正极连接到待测源正极。相对的,如果测量负电源,则需要反接。对于前放后面的隔直&滤波电容,需要将电容负极连接到前放的输出级。因为晶体管的基极电流流过499Ω电阻,导致基极电位为负(虽然程度很小),但经过25倍放大后,仍是很可观的负偏压。

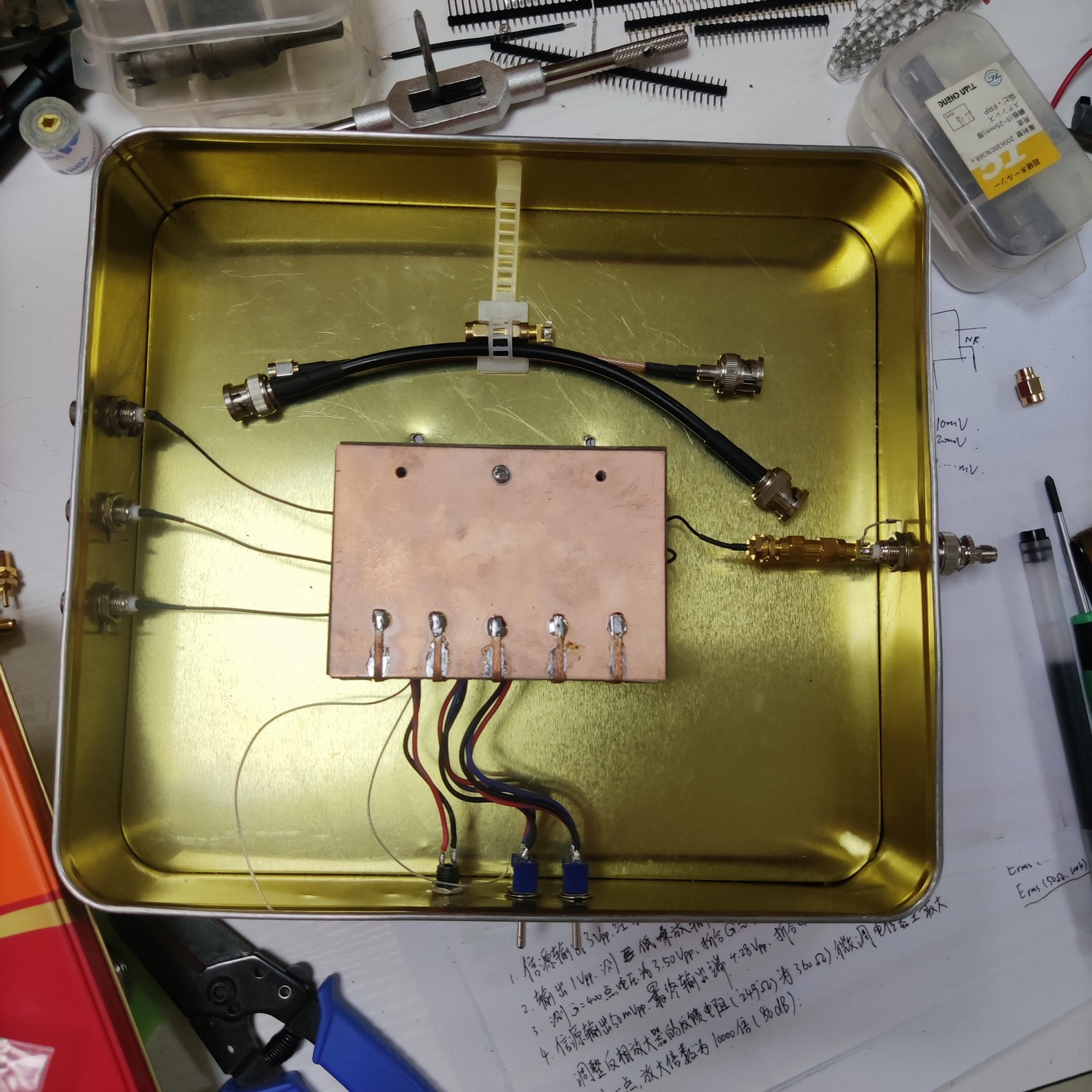

6.3-建造屏蔽盒

下图展示了AN-159所使用的屏蔽盒结构。核心的噪声放大器板子和6节碱性干电池被一起包裹在最内层的 坡莫合金 外壳中。坡莫合金具有高磁导率,可以有效屏蔽极低频磁场(比如工频)。在坡莫合金外,包裹了2OZ厚的双面覆铜板做成的屏蔽壳,金属铜具有高电导率,能有效屏蔽射频干扰。最外层是一个铁罐(饼干盒改造的),铁具有电导性同时具有磁导性,可以作为最外层的磁屏蔽屏障。总共3层屏蔽壳,每个屏蔽壳之间留些间隙用于衰减磁场。更详细的屏蔽材料信息请参阅 附录1-磁屏蔽材料

美味的Cookie Box.

屏蔽盒的结构详解。

请注意上述屏蔽盒的结构图左右两端BNC的连接处说明:

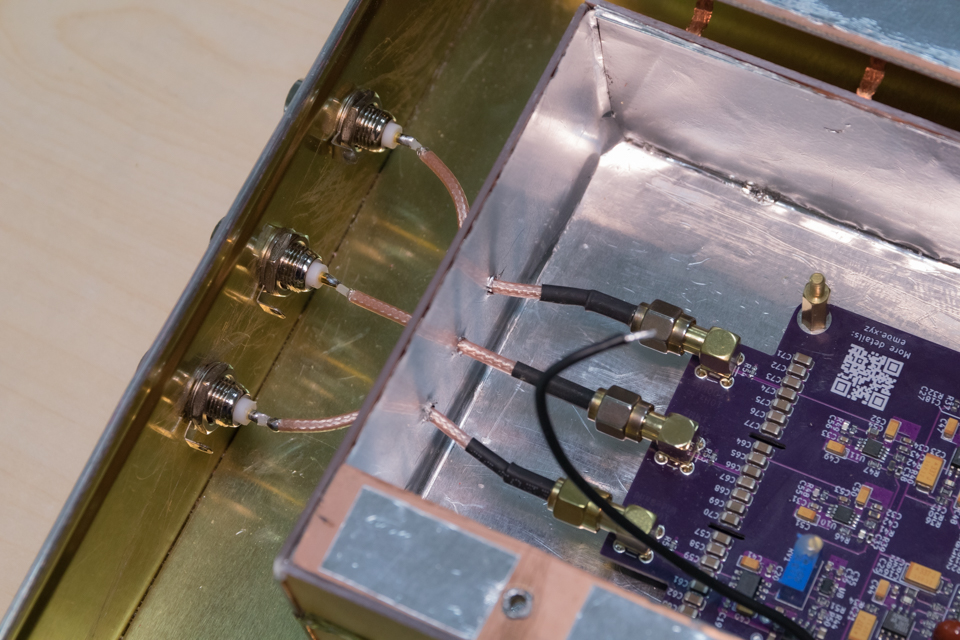

- 将输入同轴线的屏蔽层连接到BNC的外壳,并连接到金属屏蔽外壳上。

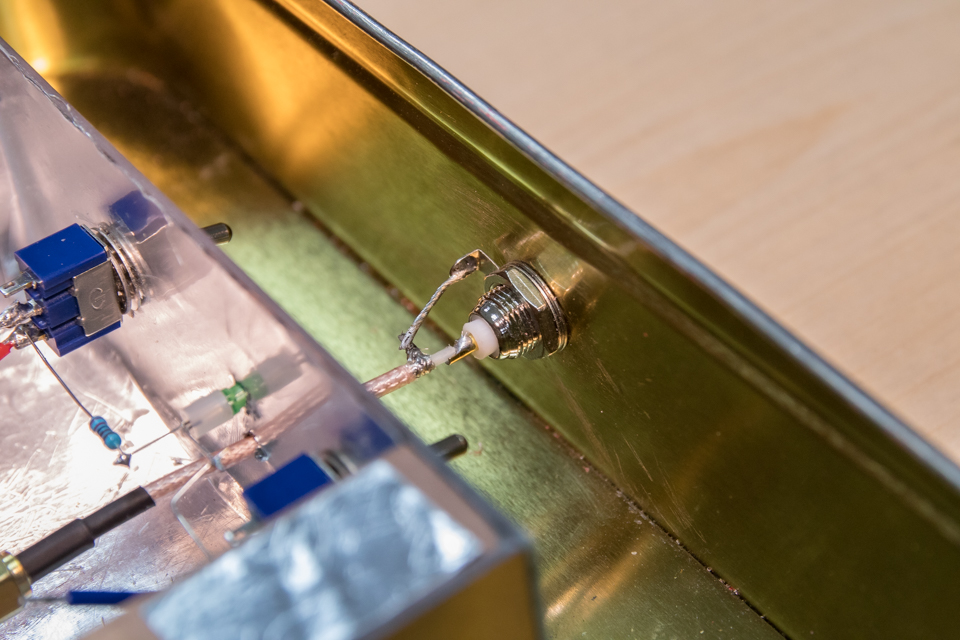

- 不要将输出同轴线的屏蔽层 连接到BNC的外壳。

6.3.1-为什么要这样连接?

为了理解其中的原因,我们需要理解容性耦合噪声的产生机理。

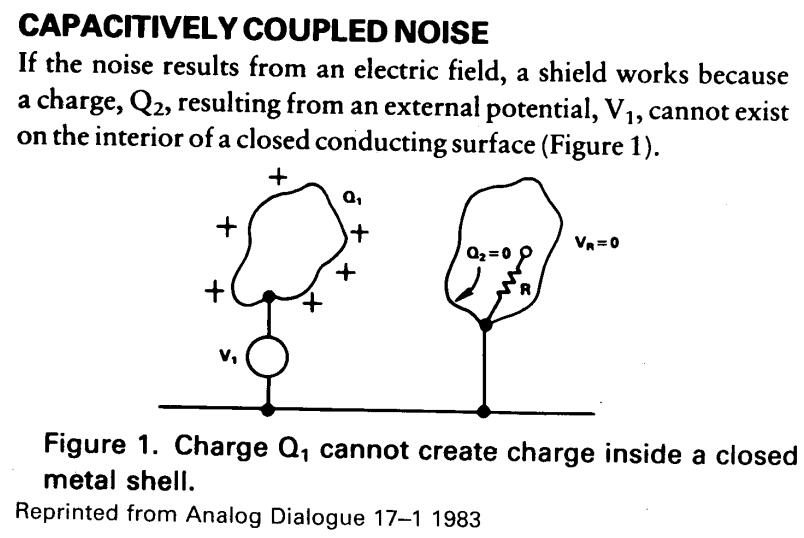

AN-347: Grounding and Shielding

如果噪声由电场产生,那么一个封闭导体可以屏蔽外界的任何电荷产生的电场,外部电势无法影响封闭导体表面包裹起来的空间。

一个有效的电场屏蔽罩需要连接到由屏蔽罩包裹起来的电路的电势参考点,不过这个电势参考点不是任何时候都是电路中的 GND。如果被保护起来的信号的参考点是 GND,那么屏蔽罩也要连接到GND。但如果信号不是以地为电势参考点的,而屏蔽罩连到了GND,那么屏蔽罩是无效的。

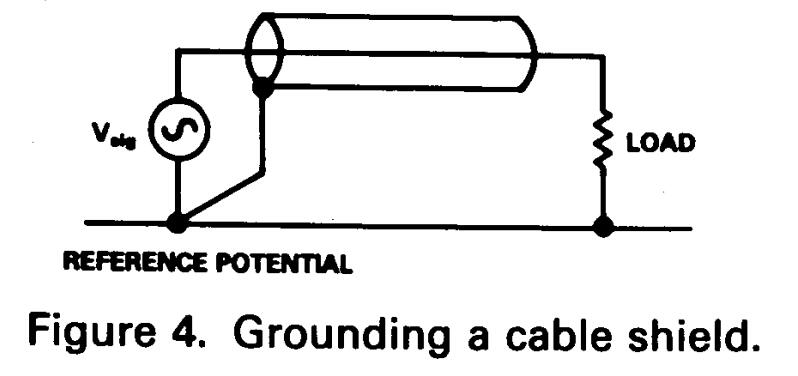

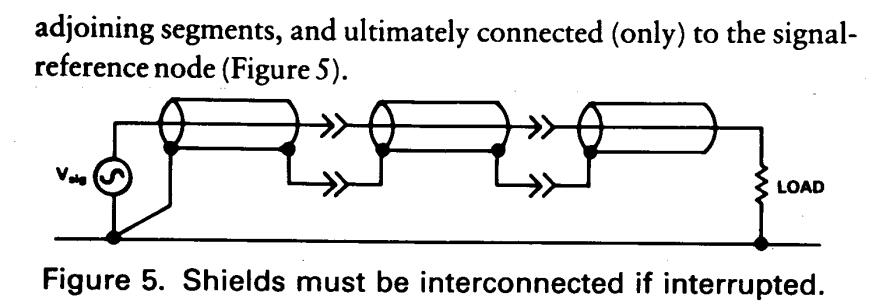

信号线的屏蔽层应该连接到该信号的参考电势点。如果系统中有多段屏蔽,那么屏蔽层需要逐级连接起来。如下图所示:

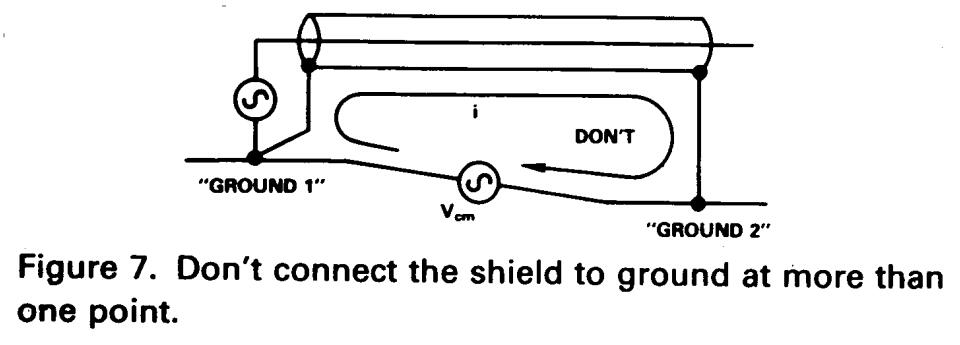

但是绝对不能将屏蔽层的两端分别接到不同的地上。即使在电气结构上这两个地是导通的,但地上2点之间的电阻并不为0,地上的电流会在2个不同的接地点产生电势差,从而导致屏蔽层的两端有电势差,形成屏蔽层内的电流,称为 "Shield Current"。这个电流将通过磁耦合效应在被保护的线缆上产生噪声。

所以,噪声放大器的输入同轴线屏蔽层需要连接到屏蔽结构的外壳上,而输出屏蔽层绝不能连接到外壳上。除开可能的噪声外,如果将输出屏蔽层连接至外壳上,极有可能产生我们不希望的地环路,甚至会引起高倍增益放大电路的自激振荡。

6.3.2-额外的注意事项

吃完美味的Cookie之后,我们要把它拿来作为屏蔽壳,但是别忘了将饼干盒的边缘上的绝缘漆层刮掉,并拿砂纸好好地打磨一下。这样可以保证盒子的盒身与顶盖有良好的电气接触,保证屏蔽的效果。同时在盒子上开孔的时候,记得将BNC外壳与盒身接触的地方的漆刮掉,保证BNC接头的外壳与饼干盒的金属部分有良好的接触。

即使我们做了如此完备周全的屏蔽结构设计,测量时还是不能掉以轻心。如果输入线过长(超过10cm),不完善的屏蔽层极有可能导致输入噪声变大,从而造成巨大的误差。推荐的连接是在待测电路板上使用SMA或者BNC连接器,通过转接头直接接入噪声放大器的输入,杜绝任何未经屏蔽的连接线。同时我们如果需要做最精密的测量时,我们需要一个几乎没有电磁干扰源的实验场地。但一般的测量在普通环境是可以实现的,除非你作死抱着这东西跑到发电站或是通信基站旁边去测(应该没人这么憨…)

七.Build Our Own NoiseAmplifier

有了以上3篇应用手册的铺垫,做一个噪声放大器似乎并没有想象中的那么困难了。但是考虑到国情与市场情况,以及前几篇手册的年代,我们若想1:1地复刻AN-159的电路还是有些困难的。

首先,前放中的核心器件——THAT300匹配晶体管,在国内不好买到。

其次,几款运算放大器买新的也挺贵的。有的型号甚至缺货、停产。

看来我们得对这个电路进行一些 "本土化、现代化" 改造了。

REV1.0

在淘宝某拆机店,我们买到了ADI现在还在生产的匹配晶体管阵列,MAT04,用于取代THAT300。但THAT300的输入噪声为0.8nV/√Hz,而MAT04的典型值是2.5nV/√Hz。看来得牺牲一(很)些(多)性能了。

运放的话,我选了拆机店里能买到的AD8056作为前放和中间的滤波级,后级的高倍放大改用了轨到轨输出的ADA4895-1。输出级2个滤波器用了2片ADA4851-2,具有高增益带宽积同时具备轨到轨输出能力。

总的电路图长这样,架构上与AN-159完全一致。

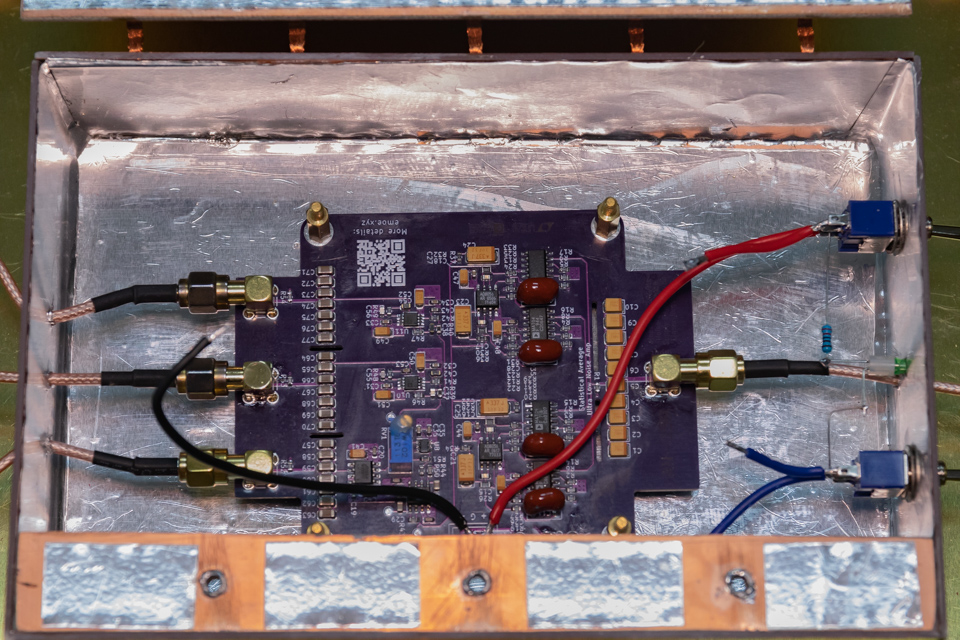

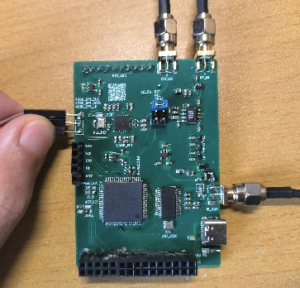

最后做出来是这个效果:

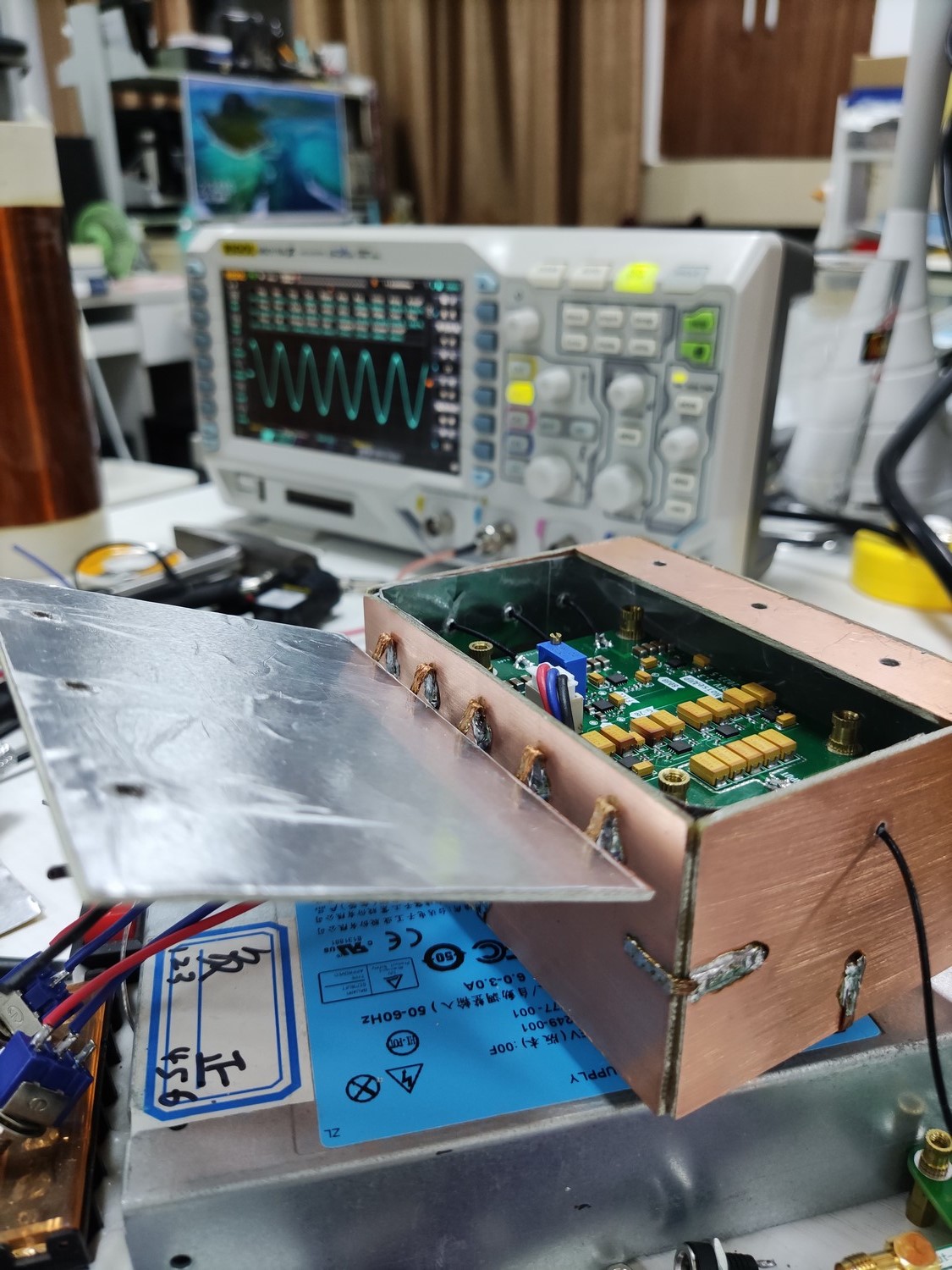

装在覆铜板屏蔽壳中的PCB,覆铜板外壳内侧贴附了 1J85坡莫合金 贴膜。

输出端的同轴线线芯与BNC母座芯连接,屏蔽层与外壳不连接。

输入端的同轴线线芯与BNC母座芯连接,屏蔽层与BNC外壳(整个屏蔽结构)连接。

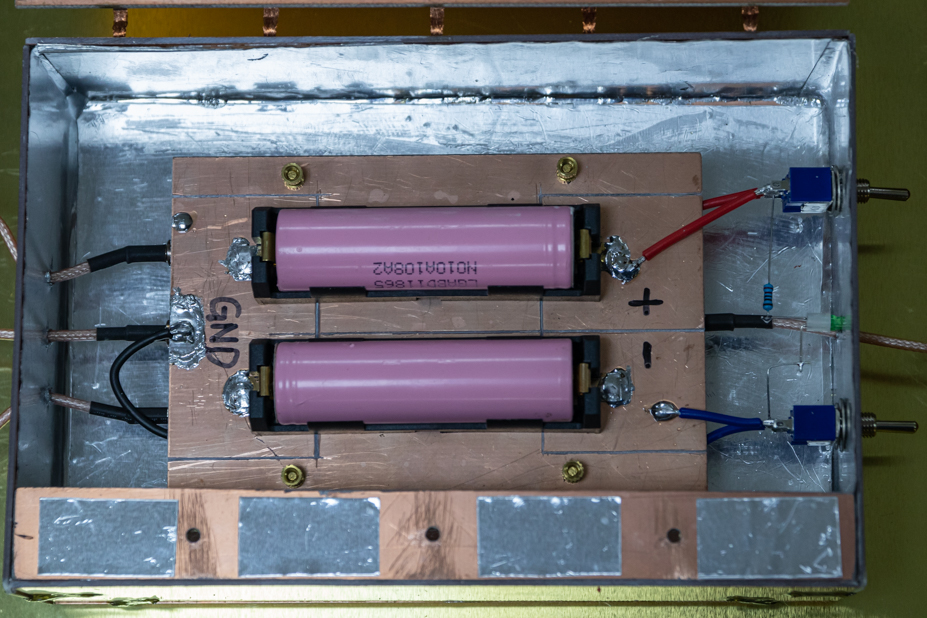

安装好电路板后,扣上18650电池仓。通过覆铜板外壳上的钮子开关控制电源。

全部组装完成,将覆铜板盖上,拧上螺丝以保证封闭壳体与良好电气接触。

最外层饼干盒上开3个BNC座的孔,刮掉孔周围的漆,保证良好电气接触。3个孔作为输出,连接到示波器用于观侧输出波形。同样的,饼干盒与盖子接触的部分也需要刮掉漆。

但是很遗憾,第一版的设计没什么严重的原则性问题,只是我买到的拆机芯片坏了(最后的输出滤波器级),导致最后无法进行测量。。

REV2.0

做完第一版之后,我仍然不满足。

第一点是,为了保险起见我没敢更改AN-159奠定的架构,即利用低噪声的晶体管作为输入级驱动运算放大器输入。然而人家用的晶体管噪声水平比我低好多倍…所以导致我的这一版本底噪很大。

第二点是,一层层的屏蔽结构导致整个放大器的体积庞大,而且想要给18650充电还得把盖子掀了,取出螺丝,再把电池抠出来充电…我有将整个仪器小型化的想法,同时增加充电功能。

为此,我开始筹划第二版的计划。

首先我们需要注意的一点是, 2022年,已经有能够满足我们需求的运算放大器面世了,虽然其噪声水平仍然高于某些晶体管与场效应管,但通过统计平均这一手段,我们有可能在一定的范围内挑战极限。

Critical Stage-前端低噪放大器选择

在任何模拟放大信号链中,对于输入级(第一级)的要求都是颇为严苛的,对于NAP(NoiseAMP)更是如此。因为第一级的放大器的噪声水平直接决定了整个仪器的底噪。第一版的设计使用了低噪声匹配晶体管作为输入级,在最小化输入噪声的同时保持了电路的高带宽特性。如果要使用运算放大器器件去代替这一输入级,对于运算放大器就提出了近乎是挑剔的要求:在保持高增益带宽积的同时具有极低的输入电压噪声和电流噪声,同时能够在低电压工作,输入输出尽量轨到轨。

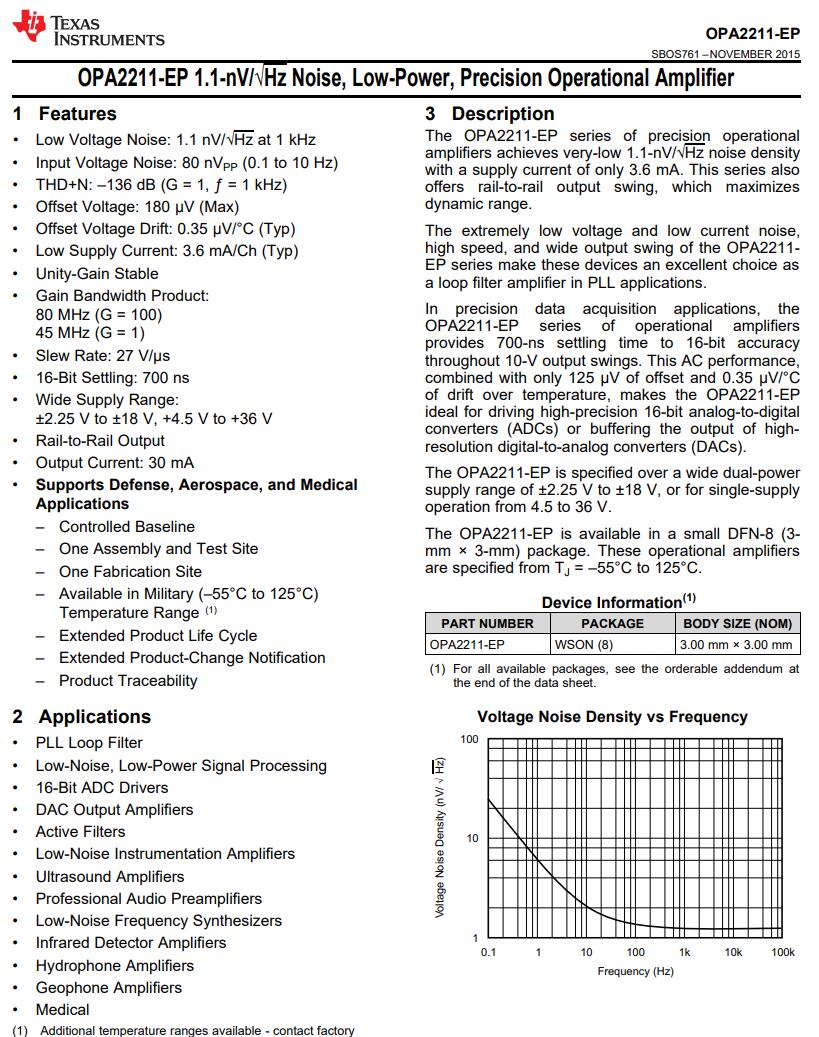

有没有这样的运放呢?2022年的今天,有的。Ti的 OPA2211-EP/OPA1612 就具有如此恐怖的性能。我想了一下,它用在这里的唯一缺点可能就是贵了。。。

当然,除了TI的OPA2211-EP外,ADI的专用仪表放大器 AD8428 同样也是绝佳的选择,但是它过于昂贵了,且买不到拆机片,遂无奈放弃。

最后,我将运算放大器和前端输入级的运放全部更换成了OPA2211-EP,以此来设计新一版的NAMP。

运算放大器噪声分析

在OPA2211的数据手册中,我们可以在Section-8.2找到典型应用-噪声分析。作为一款极低噪声运放,数据手册中给出了噪声分析的例子,非常合理。基本的放大器结构有同相和反相两种,它们分别对应的输出噪声表达式有所不同。我们可以看看它们的数学形式:

简单来说,输出电压中包含的噪声由几个部分分别贡献,并应用叠加原理将他们代数和相加。

- 运算放大器自身的输入电压噪声乘以增益G

- 2个反馈电阻R1和R2的热噪声(约翰逊-奈奎斯特噪声)

- 输入电流噪声作用到反馈电阻R2上产生的电压噪声

- 输入信号源内阻Rs的热噪声

这是2个表达式所包含的公共部分,而同相放大器结构中还要算上输入电流噪声在输入信号源阻抗上产生的电压噪声,并且该电压噪声会被放大,还得乘以增益G。

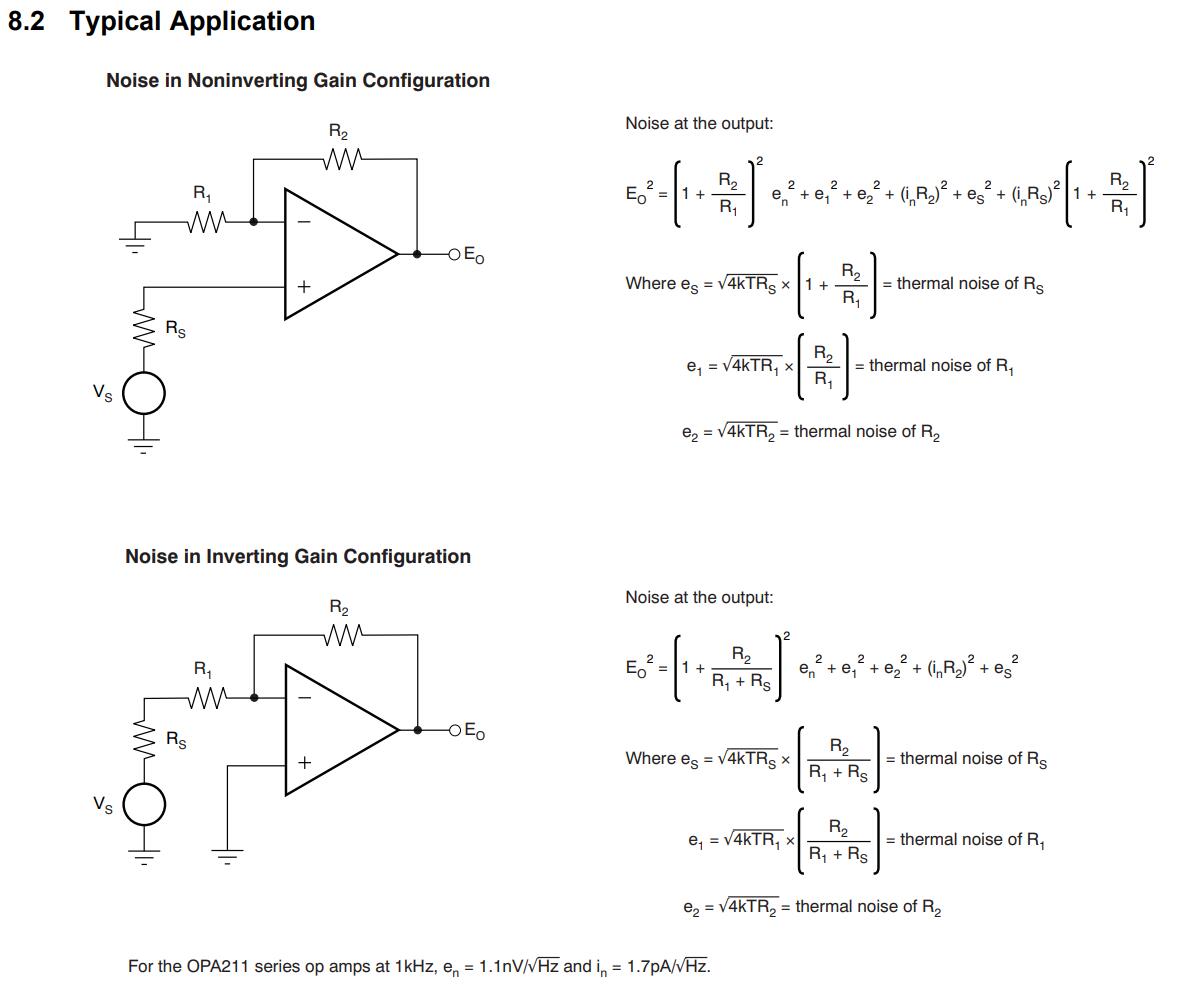

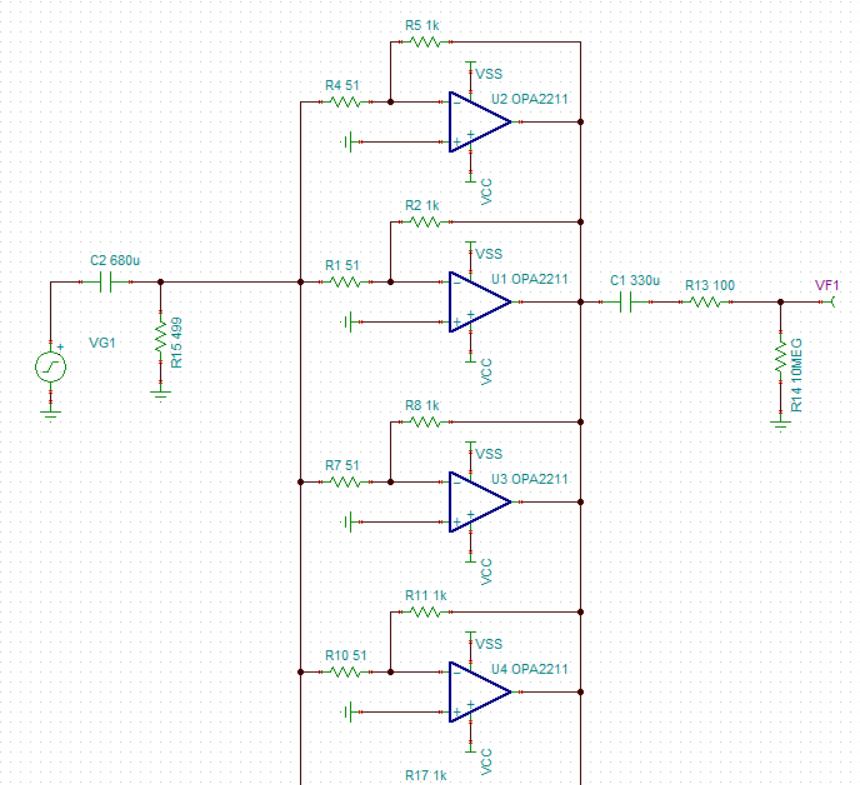

看起来,反相放大器结构更适合作为噪声放大器的输入级~因为它不存在输入电流噪声在输入信号源阻抗上产生的电压噪声。我们可以使用Ti自家的仿真软件TINA来跑一跑仿真,看看它们各自的表现。

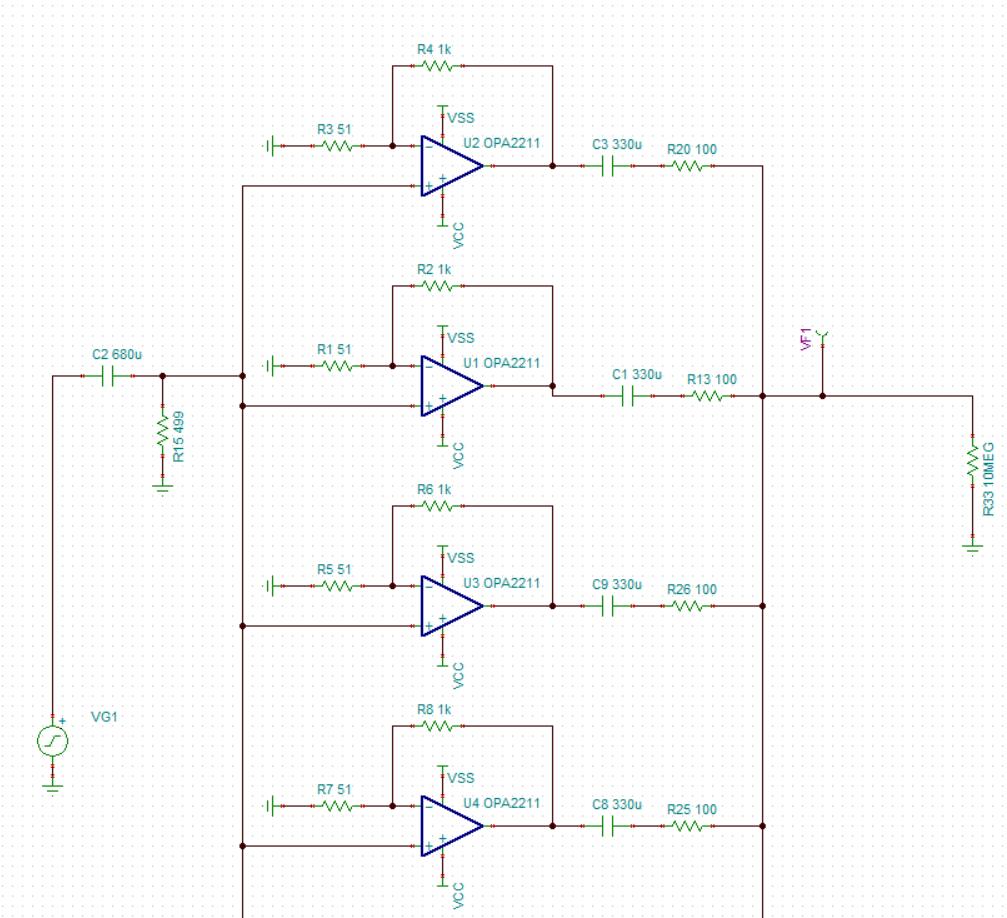

首先在Ti官网下载OPA2211的Tina Spice模型,然后导入Tina,搭建8单元并联反相放大器电路图如下(太高了,没有全部截下来),注意设置信号源阻抗为50欧。

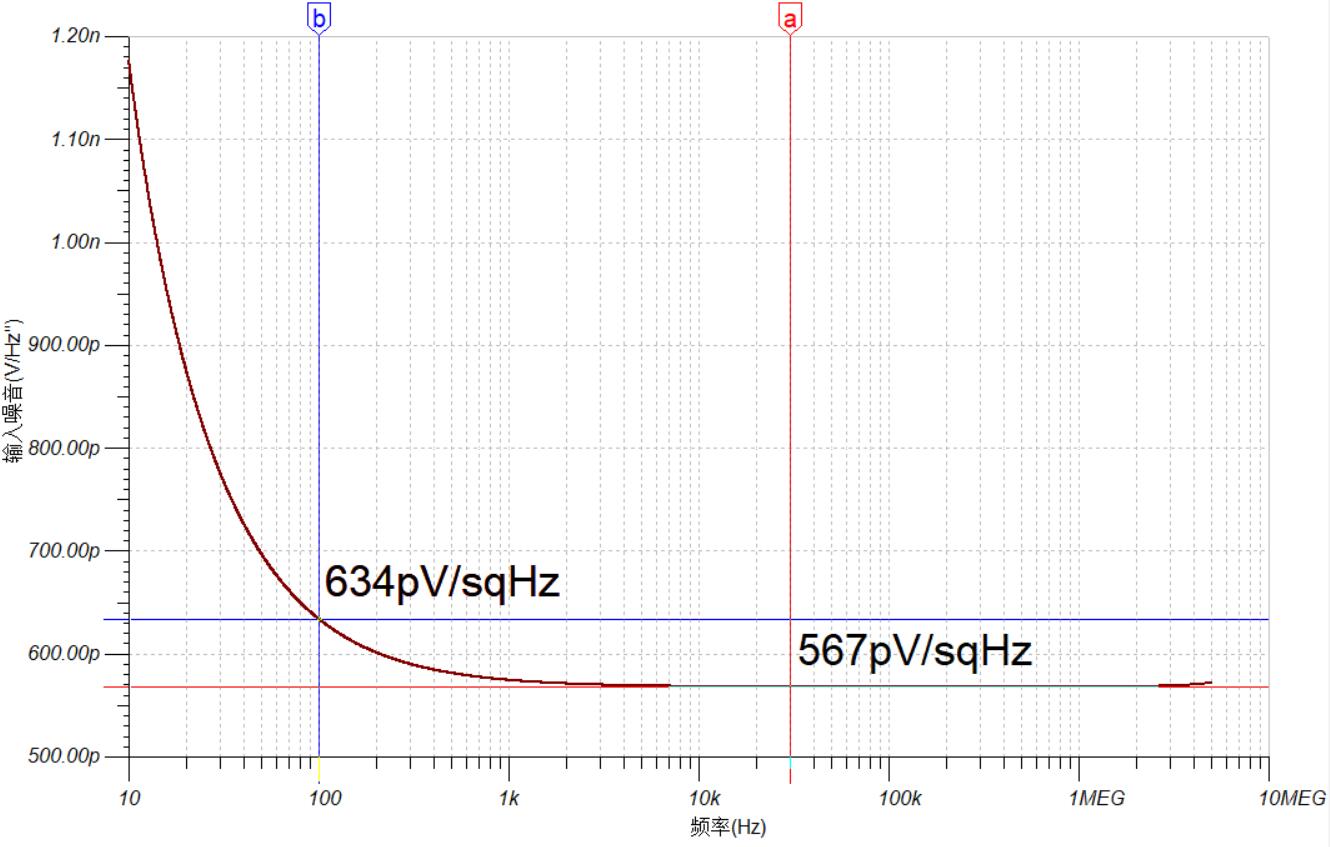

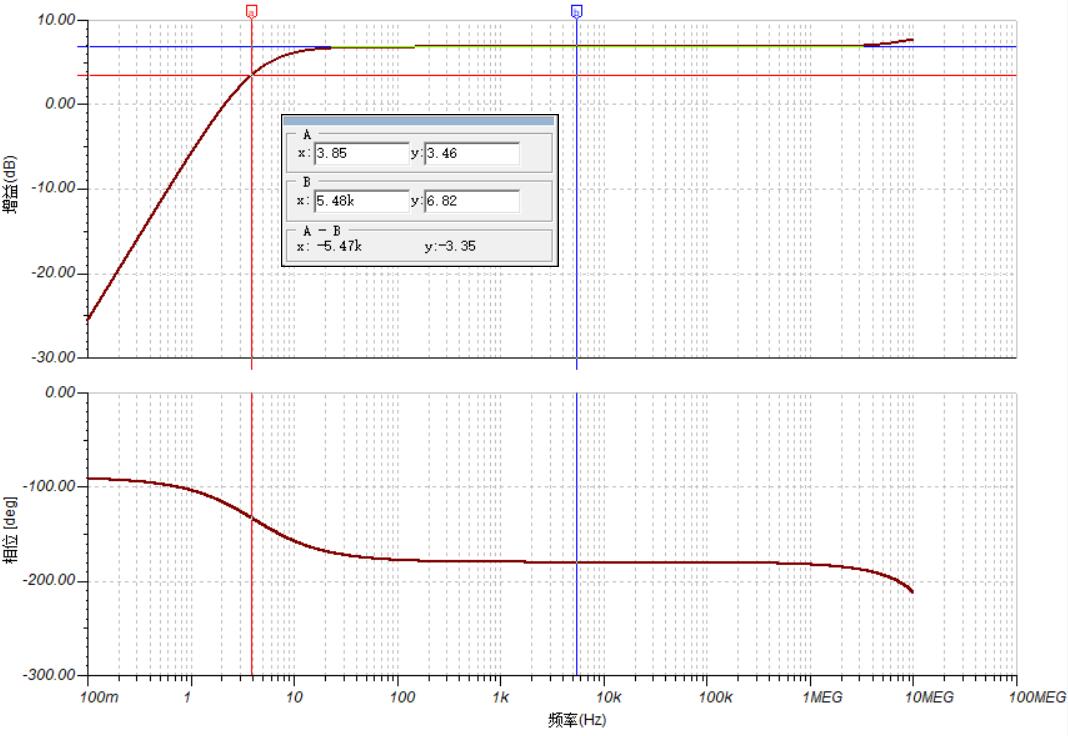

然后在分析选项中选择噪声分析,设定起始频率1Hz,终止频率5MHz,采样数5000,S/N信号振幅1,图表处都勾上,然后润,得到结果如下:

继续搭建8单元同相放大器,然后再运行噪声分析,电路图和结果如下:

通过仿真结果,我们作对比表如下:

| 放大器结构 | 低频噪声(1Hz处) | 宽带噪声 | 1/f转折频率 |

|---|---|---|---|

| 同相 | 9.19nV/√Hz | 699pV/√Hz | 约70Hz左右 |

| 反相 | 1.18nV/√Hz | 567pV/√Hz | 约100Hz左右 |

显然,反相放大器结构的表现更优。但是反相放大器有个问题就是,它的输入阻抗就是输入电阻51欧。不过我们要测量的噪声源一般都是低阻抗输出源,所以问题不是很大。

不过为了保险起见,我还是仿真了一下交流传输特性。当输入源阻抗设置为0欧时,得到的输入高通滤波器(那一级RC)的截止频率漂到了约35Hz处,本应该在10Hz的。。这倒不是什么大问题,增益不drop就行了。但是当把源阻抗设置成50欧时,预料之中的现象出现了:

该电路的增益直接drop到了6.82dB,原先本应该是25.88dB(约19倍多电压增益)左右的。因为该单元反相放大器输入阻抗为51欧,又是8通道并联,导致总输入阻抗进一步降低,结果可想而知。

因为我们要测量的噪声源不一定都具有低输出阻抗,所以我还是决定放弃使用噪声性能更优异的反相放大器结构。。。(忍痛割爱了属于是。)相比之下,使用匹配三极管对作为输入级好像不存在这个问题orz

更详细的运算放大器噪声分析可以看这篇文章—— 运算放大器噪声分析。

New Design-船新设计

其实并没什么新意。只不过是把输入级换成纯运放,并把后级所有运算放大器都换成了OPA2211-EP。电路图很简单,就不放啦。

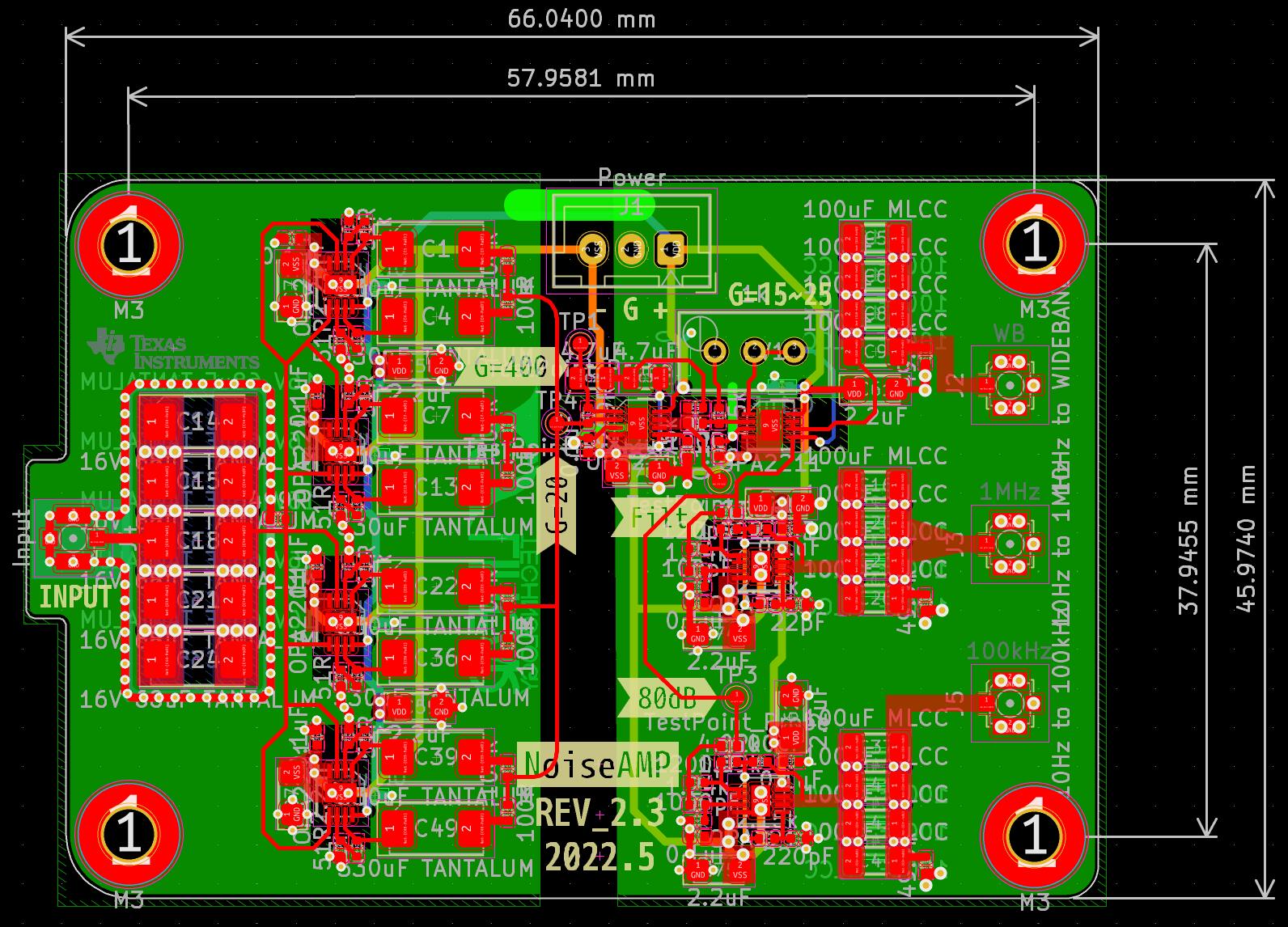

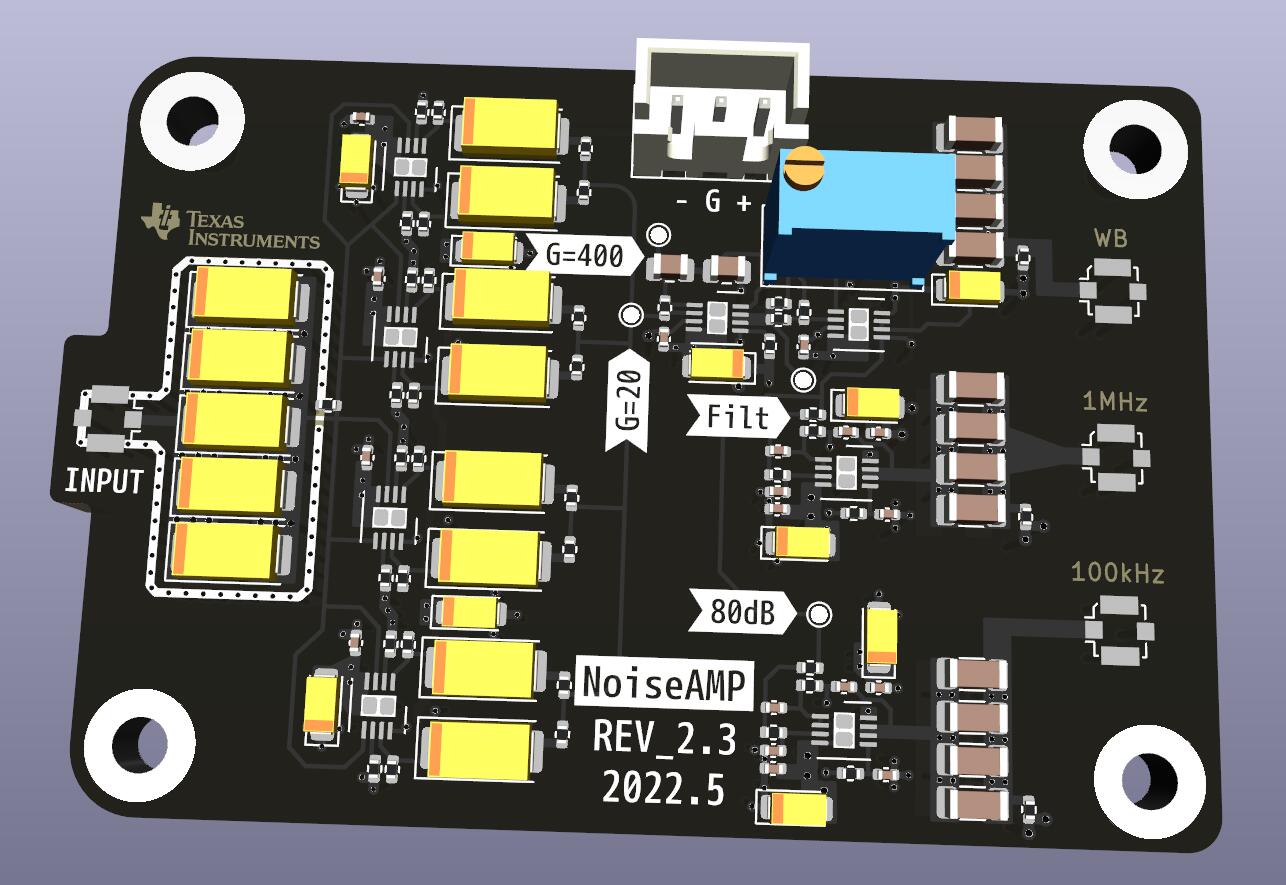

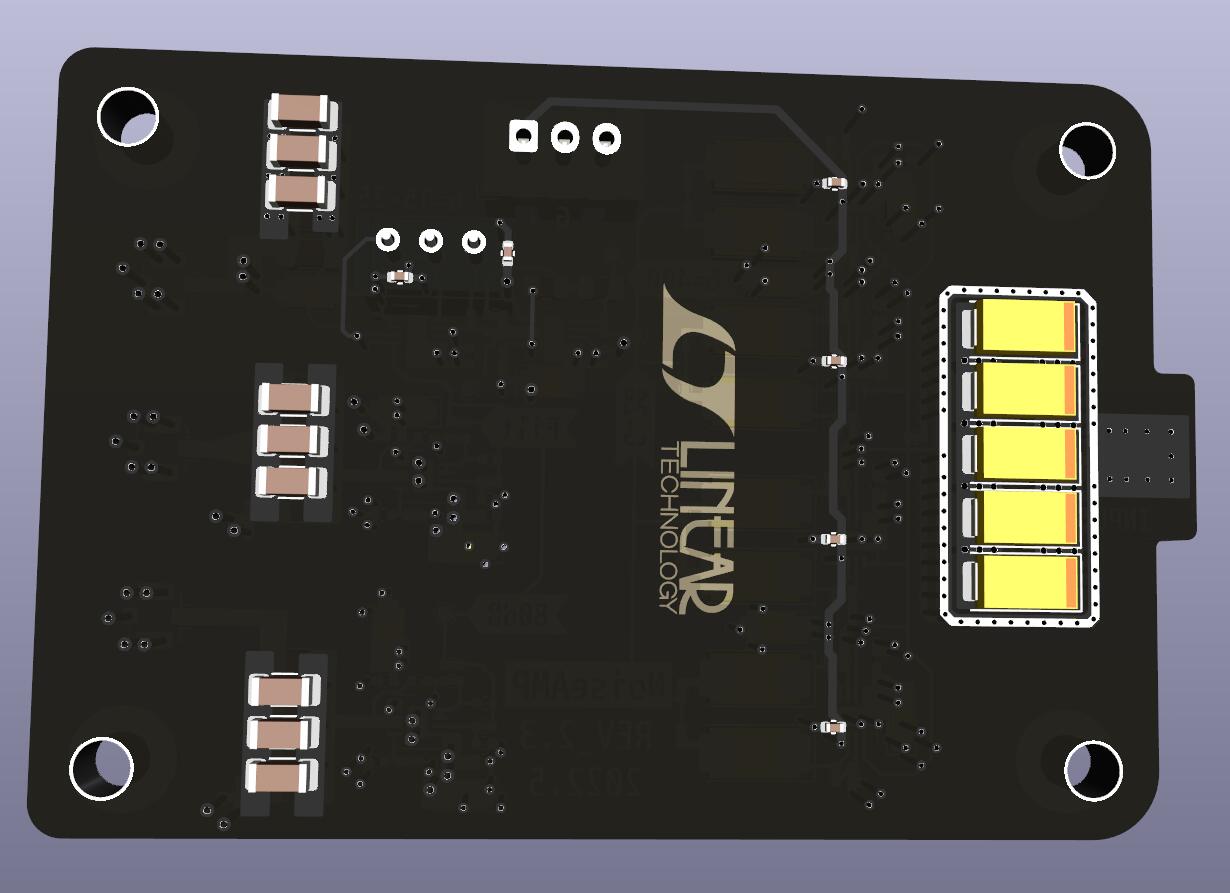

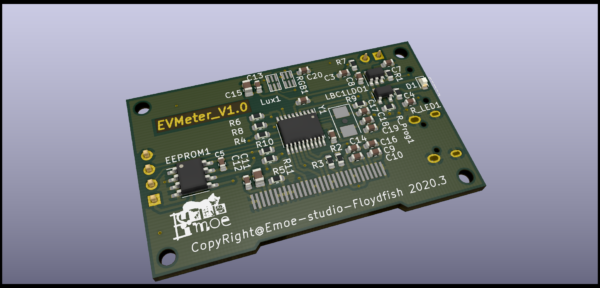

PCB画出来长这样,左边输入,右边3个输出,全部使用ipex天线座子,当然最后组装的时候是直接焊了线头上去。输入端的电容处放了Guarding Ring,用以收集可能存在的PCB上的漏电流。

然后我还做了个电池板,用来为NoiseAMP供电,板上安装了2块14500锂电池(满电电压4.2v),用IP2325作为2s充电控制器(5V输入,升压至8.4V充电),由于充电回路和放电回路的参考地不同,所以设计了2个单刀双掷开关用来切换电池的工作模式。

最后把电路组装好,扔进新的屏蔽盒里,然后在外壳上开孔、贴上标识标签、固定好机械元件。船新的噪声放大器就出炉了~

初步的增益调整与测试

装进屏蔽盒中,理线。上面的尼龙活动夹真好用,可以把配套的测试线和转接器一起放进内部固定住

在word里简单设计了几个贴纸,打出来然后拿剪刀剪,感觉像回到了小学美术课剪纸…

校准、验证、测量

组装完毕后,我们还不能进行测量。首先,我们得进行校准工作。

校准-Calibration

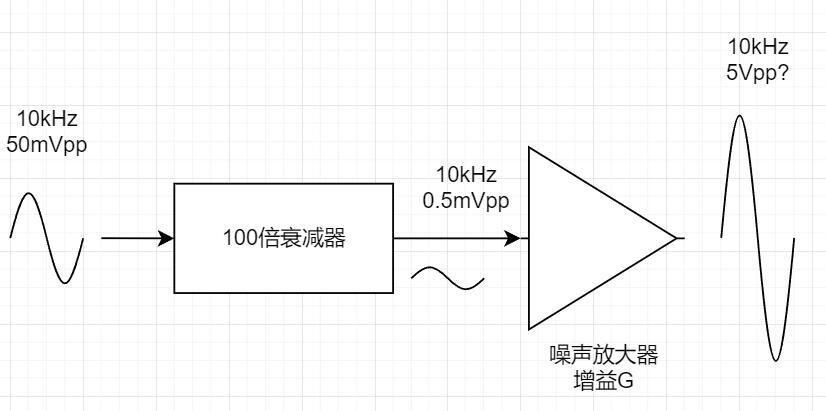

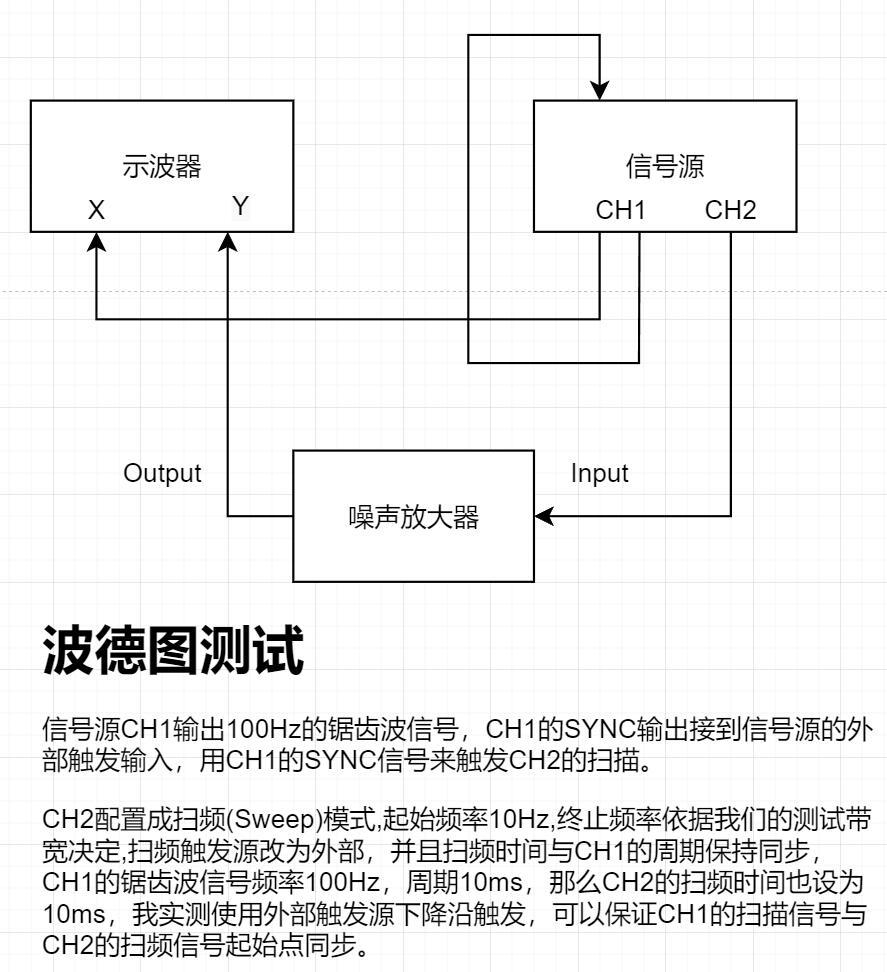

校准工作主要是校准噪声放大器的放大倍数。我们根据电路的参数,搭建测试框图如下:

由于一般的信号源无法输出uV级别的信号,所以我们需要通过外部衰减器来得到我们的输入测试信号。

设置信号源输出阻抗50欧姆,输出10kHz、50mVpp的正弦信号,经过一个100倍电压衰减的衰减器(我拿了一个1M电阻和10k电阻分压器,直接搭棚焊在2个SMA座子上,非常好用),得到一个10kHz、0.5mVpp的正弦信号。将衰减后的信号送入噪声放大器,在10Hz~100kHz输出档位观测其输出信号的峰峰值,如果输出信号峰峰值不为5Vpp,则增益就需要调整。最初我测量到的增益约为3600左右,离我们的设计目标10000倍相去甚远(好吧按dB来看的话也差不太多…),于是我将输入级后的反相放大器反馈电阻微调至360欧,后调节后级可变增益级的电位器,将整个放大器增益调至了10000倍。

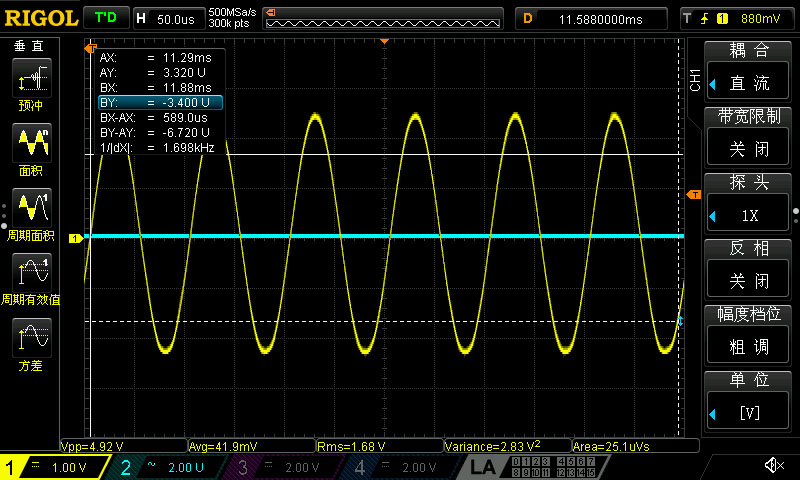

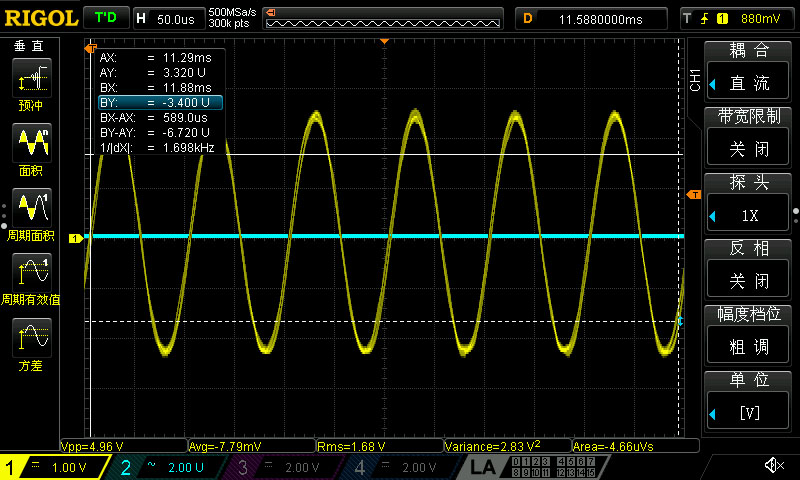

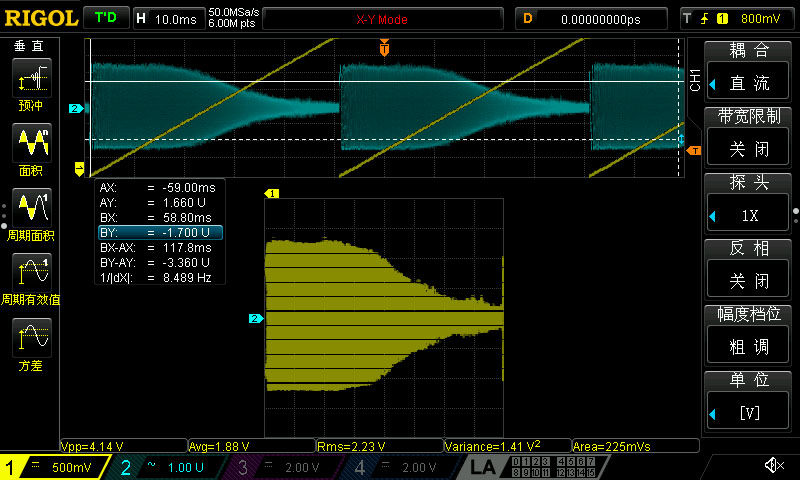

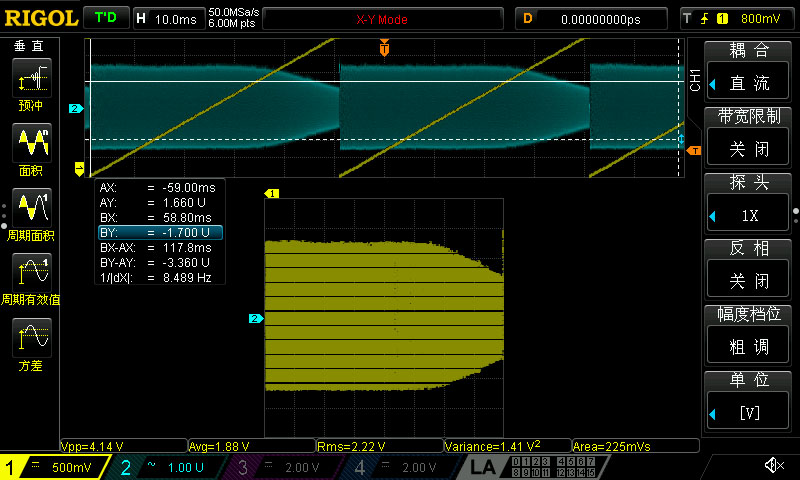

同时我们还可以验证一个有趣的现象,下图中图1是将屏蔽盒(饼干盒)的盖子紧密地盖上去时测得的输出,而图2是将屏蔽盒的盖子取下来测得的输出,可以明显看到信号中夹杂着某种低频干扰,尽管干扰十分微弱,但经过10000倍放大后,对输出信号造成的影响还是非常可观的。

验证-Verification

校准了增益之后,我们来验证3个输出档位的频域响应是否符合我们的预期。由于我没有网络分析仪,不能直接得出噪声放大器的幅频特性响应曲线,所以我用了一点小技巧,使用信号源和示波器来间接完成了这项工作。

丐版幅频特性测试

其中,调整示波器的时基模式为X-Y模式,X输入为行扫描信号,由信号源CH1的锯齿波输出提供,Y输入接到噪声放大器的输出,而噪声放大器的输入接到信号源CH2的扫频输出,CH1锯齿波的同步信号用于触发扫频,实现起始点同步。这样就可以构建出一个丐版波德图测试仪。。。

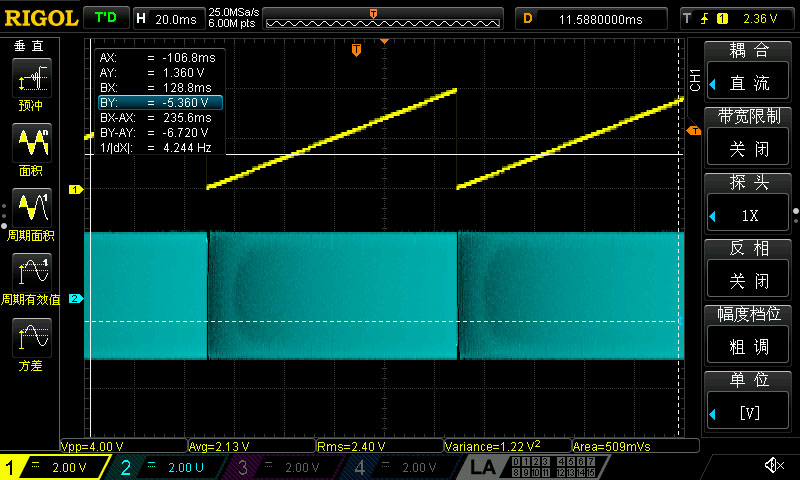

锯齿波与扫频信号的起始点同步

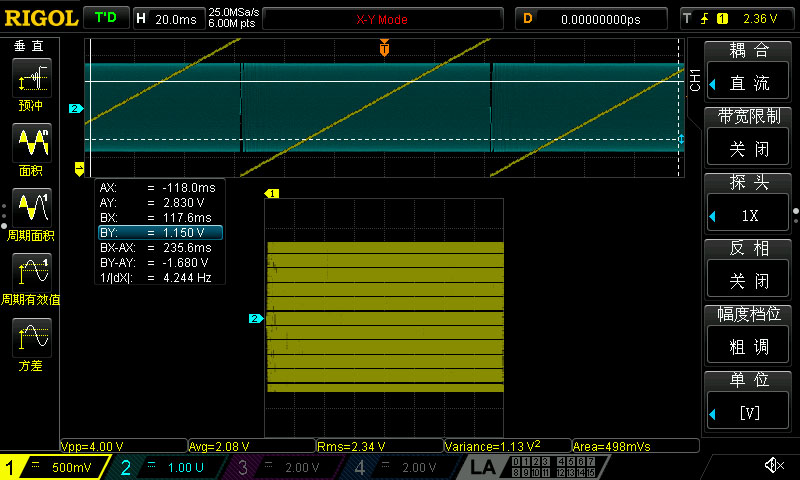

开启X-Y时基模式,可得到简陋的波德图

带宽测试

首先测试10Hz-100kHz档的幅频响应是否符合预期。设置扫频信号起始频率10Hz,终止频率100kHz,观察示波器XY绘图如下:

可以看出,在接近100k时,增益有所下降,虽然我们很难读出其精确值,但判断-3dB点还是没问题的。不过保险起见,我们还是要稍微提高一些频率,看看其带外衰减如何。将扫频终止频率提高到200kHz,观测到XY绘图如下:

到这里我们就可以放下悬着的心了——,这个100k截止频率的低通滤波器看起来工作得很不错。

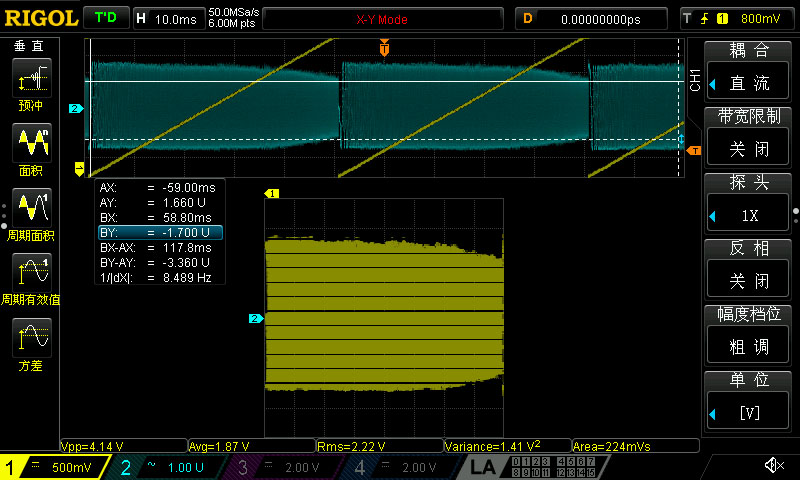

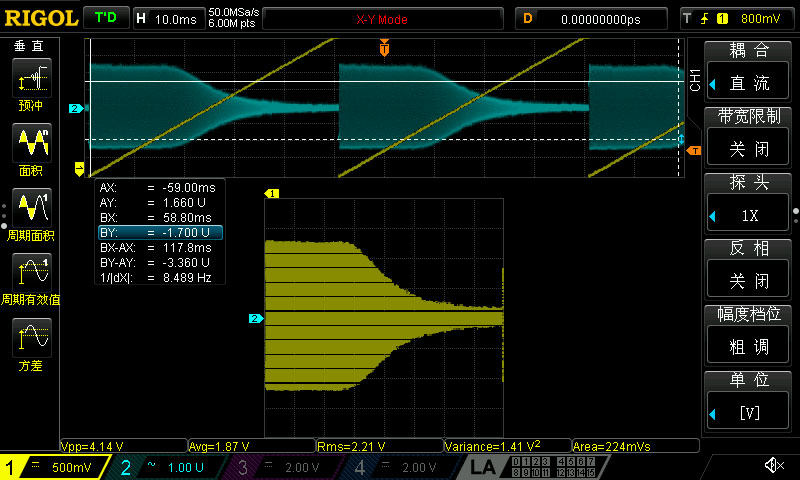

然后我们测试1MHz档的幅频响应。设置扫频到1MHz,观察示波器输出XY绘图如下:

嗯,波形变化更为平滑了,不错。提升扫频频率到2MHz,XY图长这样:

安心洗爹。

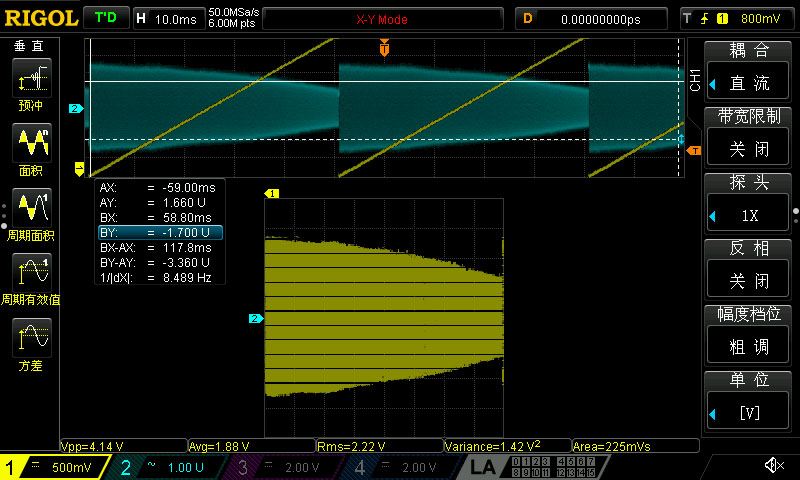

然后测试宽带输出,直接将扫频频率提升到3MHz,观察XY绘图如下:

可以大致读出,带宽约为…2.几MHz吧,到3MHz以上的信号,受限于运算放大器的增益带宽积(G=100,GBW=80MHz),我估算了一下有效带宽勉强能到5MHz,总之是非常不戳的。

底噪验证与探索

在校准完增益、验证完带宽后,我们还需要测试噪声放大器的底噪。某种意义上来说,这是最为重要的参数了^_^。我们进行以下测试,一是为了验证我们的噪声放大器的底噪水平,二是探索在测量中会有哪些误差源。

- 关机,加上屏蔽盒盖子输出端噪声

- 关机,去掉屏蔽盒盖子输出端噪声

- 输入短接-100kHz带限噪声

- 输入短接-1MHz带限噪声

- 输入短接-宽带带限噪声

- 输入50欧SMA负载帽-100kHz带限噪声

- 输入50欧SMA负载帽-1MHz带限噪声

- 输入50欧SMA负载帽-宽带噪声

- 输入接一截线浮空,输出端噪声

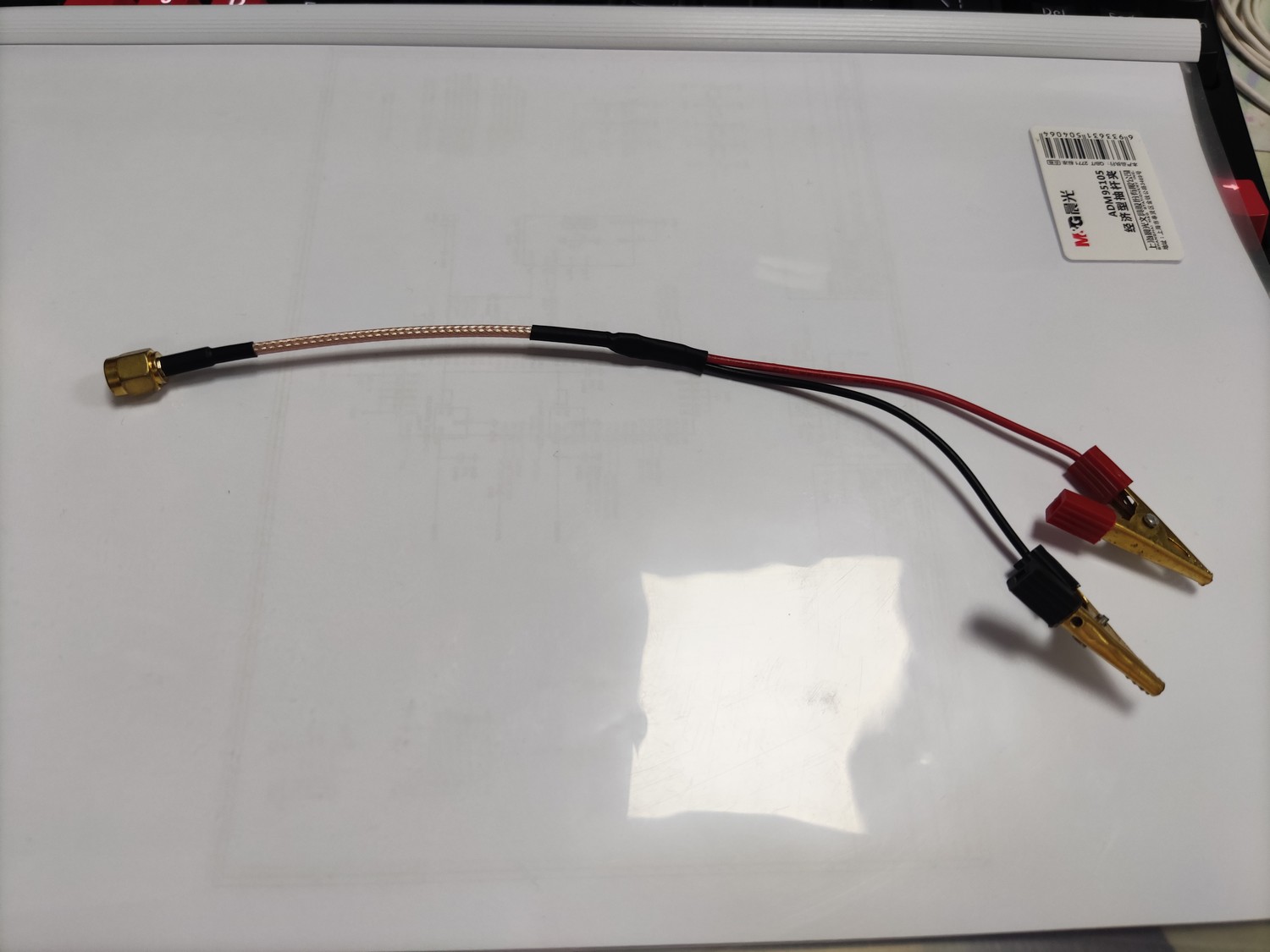

- 输入接一截SMA转鳄鱼夹线,手靠近同轴线,输出端噪声

- 输入接一截SMA转鳄鱼夹线,手靠未屏蔽的部分线,输出端噪声

哈吉马路由——

关机状态下输出端噪声

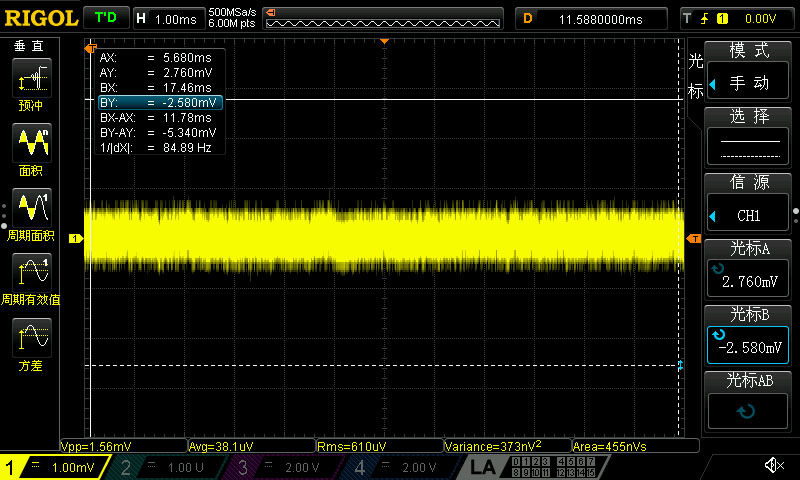

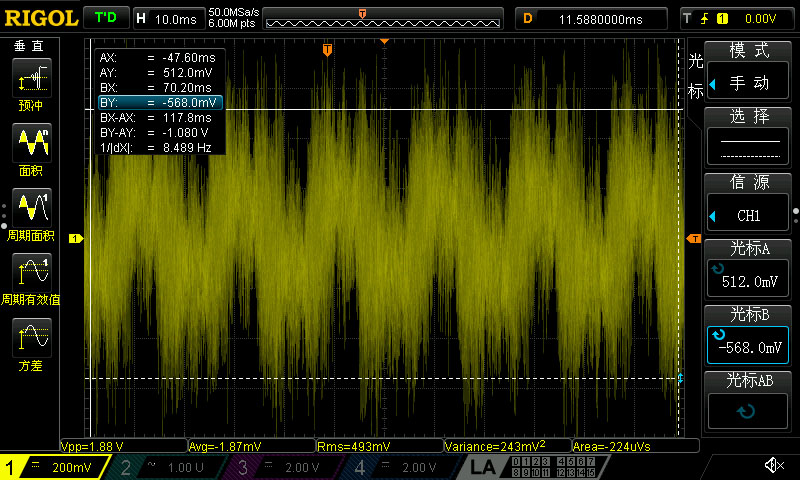

将电源短开,输出接到示波器上,观察输出端噪声。虽然电路是没有通电的,但这并不意味着电路中不会耦合进噪声信号。First of all,将屏蔽盖好好地盖上,看看输出噪声(时基1ms/div):

然后将屏蔽盖取下来,再看看输出噪声:

嗯,影响显而易见了。加上屏蔽盒盖,输出端的噪声水平大致就是示波器的底噪水平多一些(示波器底噪约500uVrms)。而取下屏蔽盒盖,输出端的噪声水平直接飙升至约2mVrms,数值上翻了4倍,并且可以看到明显的50Hz工频干扰(突起来的那一坨刺)。我手头没有频谱,很难详细分析这些噪声的频域特性。但反观盖上盖子的情况,似乎也有一些些50Hz的特征。。我藉此猜想,可能是因为我的坡莫合金屏蔽层不连续。AN-159中使用的是实心坡莫合金板材,加工成了一个完全密封的盒子,而我是使用了1J85坡莫合金贴纸,贴附在覆铜板屏蔽盒的内侧,存在很多小缝隙并不能有效屏蔽。

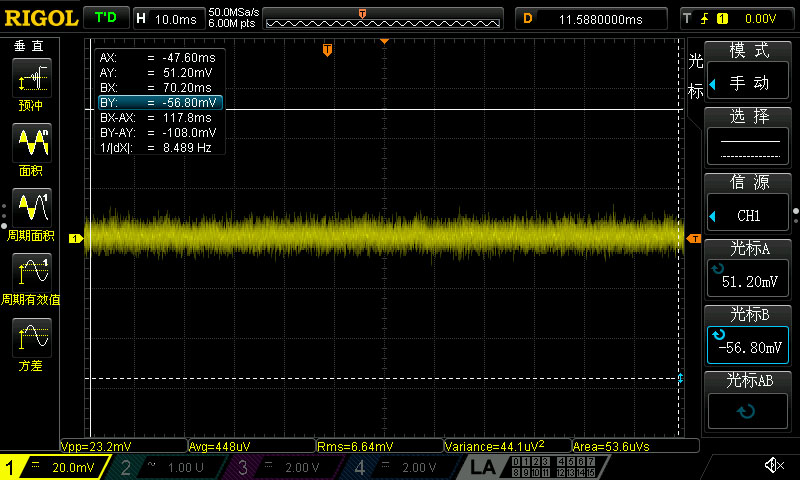

输入短接底噪测试

测试完关机状态下的噪声,我们似乎对耦合进我们的噪声放大器的噪声水平有了点ACD数(并没有)。那么我们来测测输入短接的底噪吧——

在测试前,我们先放一张AN-159中得到的测试结果图,不过请注意,这张图的纵坐标(电压坐标)是转换过的,将它乘以10000倍就是在示波器上得到的波形了,200nV乘以10000是2mV/div。

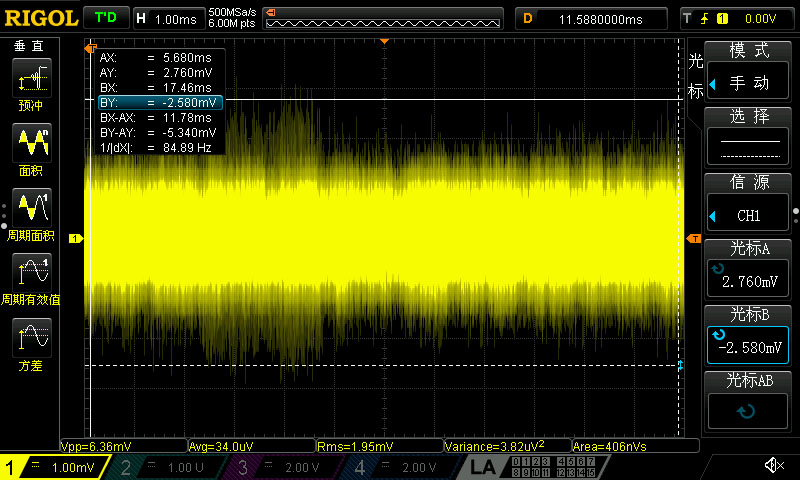

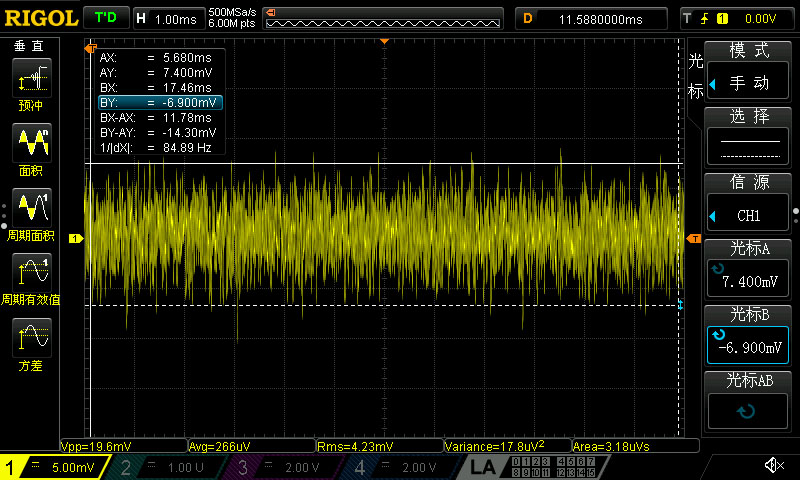

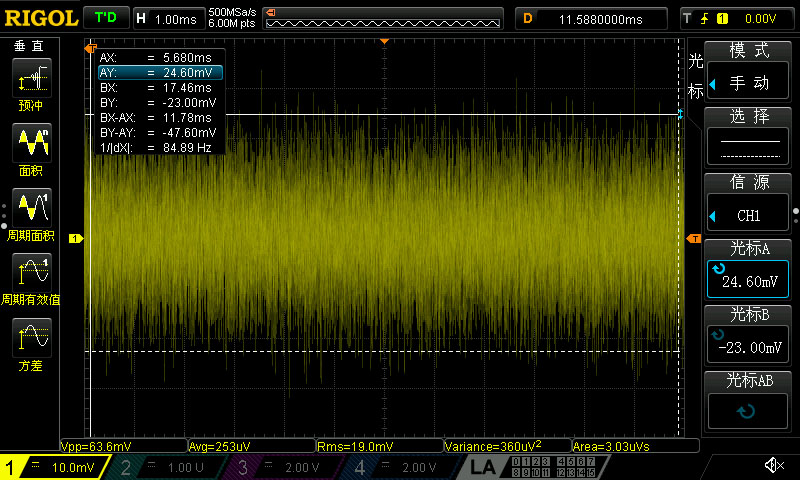

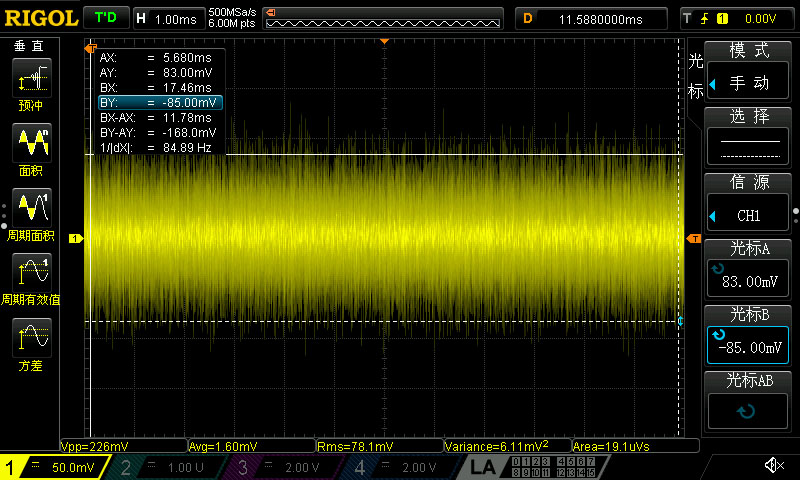

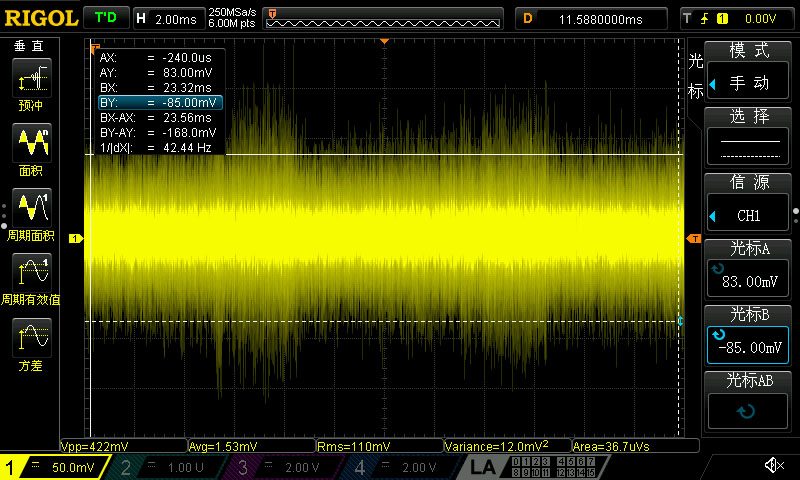

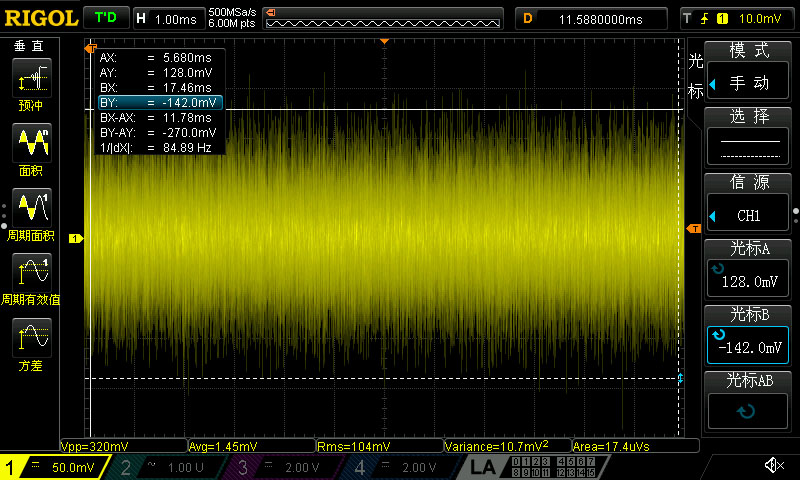

输入短接,在100kHz、1MHz、WideBand 三个输出端分别观测到噪声水平如下:

然后,如果用爪爪摸一摸输入端的SMA芯子(对地短路了的),即使输入对地短路了,还是会有工频干扰(没错,就是我身上的!)耦合进信号链中。

然后作一个总结表如下:

| 测试条件 | 噪声峰峰值(Vpp) | 噪声真有效值(RMS) | 折合到输入端的噪声真有效值(RMS) |

|---|---|---|---|

| AN-159的100kHz带限噪声 | 估计为10mVpp | 估计为2.15mVrms | 估计为215 nVrms |

| 我的100kHz带限噪声 | 19.6mVpp | 4.23mVrms | 423 nVrms |

| 我的1MHz带限噪声 | 63.6mVpp | 19.0mVrms | 1.9 uVrms |

| 我的宽带噪声 | 226mVpp | 78.1mVrms | 7.81 uVrms |

| 爪子摸输入的宽带噪声 | 422mVpp | 110mVrms | 11.0 uVrms |

不过,示波器的测量结果不一定可靠。因为其rms算法并不能测量到真实的rms值,只能计算出采样样本波形的rms(并且可能对于这种波形,误差还不小)。更要命的是,我这个示波器直流offset有点大,按照Vpp读数除以6.6得到的rms值和测量的RMS值不匹配,误差贼大。如果要精准测量rms值,需要使用专用的RMS表(基于热-能量转换的rms电路)。不过很遗憾呐,我手里又没有。

但是还是可以从峰峰值看出差异,并且做一个大致的估算:即我的噪声放大器的底噪大约是AN-159中的2倍大小左右。

输入接50欧SMA负载帽

测试了底噪之后,我们便可以做些好玩的东西了——

我们可以来验证一下 约翰逊-奈奎斯特噪声,也就是热噪声。

对于给定带宽,热噪声电压可表示为:

V_n = {\sqrt {V_n^2} \sqrt {\Delta f}} = \sqrt{4K_BTR\Delta f}对于50欧电阻,在100kHz、1MHz、5MHz的带宽内,热噪声值大致如下:

V_{n1} = 290.7nV_{rms} \cdots 100kHz \\

V_{n2} = 919.24nV_{rms} \cdots 1MHz \\

V_{n3} = 2.055uV_{rms} \cdots 5MHz然后我们在输入端接上50欧阻抗的SMA假负载(堵头),测量这个假负载上产生的噪声。

100kHz带宽

1MHz带宽

宽带

嗯,很遗憾,我们测到的结果似乎并不符合我们的预期。比如对于100kHz带宽,50欧电阻产生的热噪声理论中就取300nVrms吧,与噪声放大器的底噪423nVrms叠加,平方和开根号得到的输入噪声理论值约为500nVrms,而我们测量结果显示其输入噪声约为800nVrms!

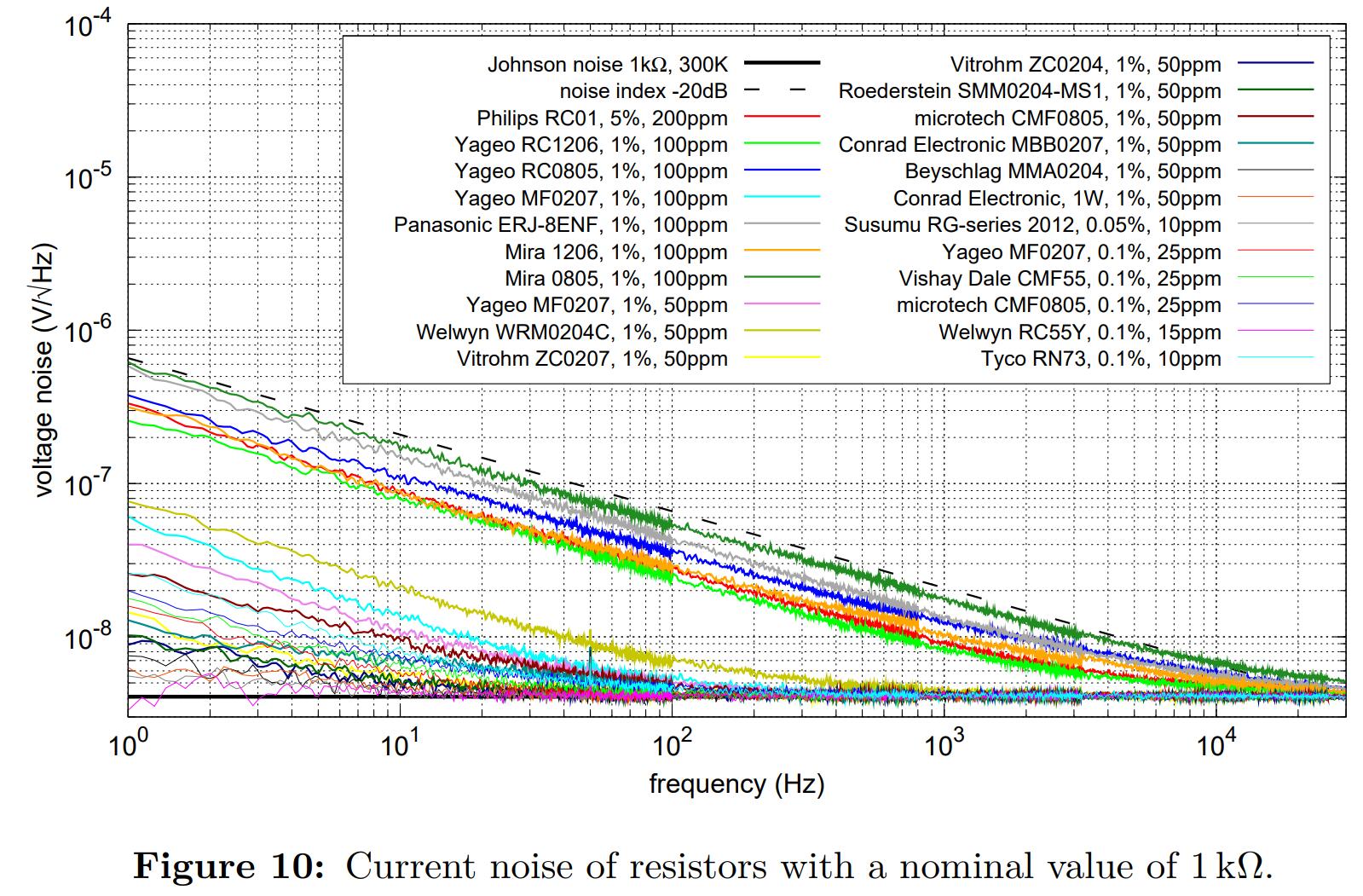

其实这并不意外。因为约翰逊-奈奎斯特噪声计算公式计算出的结果只是材料中的热噪声,而器件的总噪声不仅仅只有热噪声独自贡献,还有别的因素同样会为该器件贡献一定量的噪声。而这些噪声的量大小是取决于电阻器的阻值、材料、制作工艺等等因素的。比如这是LIGO对不同品牌的同阻值电阻器的 电流噪声 做的测试,最底下黑色实心线是该阻值下的电阻器的热噪声。结果表明,不同材料和制造工艺的电阻器的噪声水平有时候甚至能差出2个数量级。

不过,在这里纯粹是示波器的误差太大了…我换了个示波器测量就完全ok了,详情请参考本文的续集(文末链接)。

输入接一段线

增加这一组测试的目的是演示一个测试问题:如果输入线过长或未经良好屏蔽,可能会引起巨量的测试误差。如果使用未经屏蔽的线去连接待测电路,那么这一段线就会像一截 天线(Antenna) 一样,吸收环境中的电磁波,包括从极低频(工频50/60Hz)到射频频段的所有电磁波,从而将环境中的电磁信号耦合进噪声放大器的输入端。

首先,我们将一截长度约20cm(同轴线10cm,未屏蔽段10cm)的SMA转鳄鱼夹线接到输入端上,并且让2个夹子悬空,彼此不接触,在输出端测到噪声信号如下:

可以看到非常明显的工频特征(频率50Hz),并且输出信号中含有高频噪声,但工频占主导地位。

然后我们将输入2个鳄鱼夹夹上(贴贴),与最开始测试的输入短接是等效的电路,不过我们那时用的是SMA座子直接短接,这次多了一截线。同时,我们用爪子握住同轴线那一段,在输出端测到噪声信号如下:

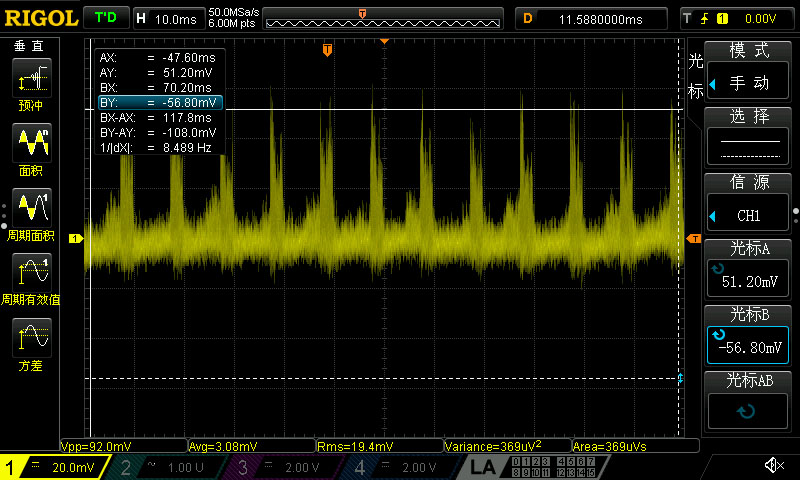

可以看到,相较于用SMA连接器直接短接的测试结果,噪声似乎大了一点点(4.2mVrms vs 6.64mVrms),但是看不出很明显的被干扰的情况。那么我们现在 用爪子握住未经屏蔽的那一段,在输出端测到的噪声信号如下:

ohh,that’s bad.我们可以看到输出信号中含有非常明显的工频尖峰,并且明显混入了工频的各次谐波…导致底噪水平直接飙升至原来的5倍左右!

通过这组对照实验,我想我们对输入连接方式的重要性有了深刻的认知…最好的连接方法是在待测电路上使用同轴连接器,直接接入到噪声放大器的输出,这样整条信号链路都是经过良好屏蔽的,这样可以将外界干扰对测量的影响降至最低。

测量-Measurements

请参考本文续集—— 噪声放大器进阶指南

附录1-磁屏蔽材料

附录2-参考资料

- AN-83:Performance Verification of Low Noise,Low Dropout Regulators

- AN-124:775 Nanovolt Noise Measurement for A Low Noise Voltage Reference

- AN-159:Measuring 2nV/√Hz Noise and 120dB Supply Rejection on Linear Regulators

- AN-347:Shielding and Guarding

- LIGO:Resistor Current Noise Measurements

- AN-6206(MAXIM, 现在也变成ADI的了…):SIMPLE, EFFECTIVE METHOD AND CIRCUIT TO MEASURE VERY-LOW 1/F VOLTAGE REFERENCE NOISE (< 1mVP-P, 0.1HZ TO 10HZ)

- [魔法电路]-电路中的噪声

- MT-048:Op Amp Noise Relationships: 1/f Noise, RMS Noise, and Equivalent Noise Bandwidth

- Mu-Metal Brochure

- K&J Magnetics: Shielding Materials

- Analog Dialogue:无烦恼,高增益:构建具有纳伏级灵敏度的低噪声仪表放大器

- Analog Dialogue:该噪声会让您夜不能眠

- Analog Dialogue:对电阻使用的经验法则说不

- 无烦恼,高增益:构建具有纳伏级灵敏度的低噪声仪表放大器

![Read more about the article [综合项目]01-波形发生器设计](https://www.emoe.xyz/wp-content/uploads/2020/09/launchpad_t-300x178.jpg)

![仪表博物馆[04]—HP 3312A模拟信号发生器](https://www.emoe.xyz/wp-content/uploads/2023/06/IMG_5451-2-600x400.jpg)

多个运放并联,如何保证各个运放输出的电压相同,不会出现灌电流的情况

根据失调和增益计算输出的最大直流电压差,输出串合适的电阻限流即可。当然最保险的做法是每个运放输出都使用电容交流耦合,然后再输入到后级加法器电路的输入端

看芯片数据手册十分好奇nV级别的时域噪声是什么测出来的,这篇文章帮助太大了

液态钽电容可以在贸泽找到,https://www.mouser.cn/c/passive-components/capacitors/tantalum-capacitors/tantalum-capacitors-wet/,就是价格太美丽

有个疑问,输出端只有信号输出,没有地,输出是怎么实现的?

输入的地和金属屏蔽外壳连接(整个放大器的地只在这一点和外壳连接),输出BNC端子的外壳与金属屏蔽外壳有良好电气接触,这个地实际上是绕了一个大圈到输入端,实现单点连接

好的,感谢

哈哈精彩,忘了提一下Jim Williams用的带中文字的饼干铁盒

哈哈哈是的,记得像是个月饼礼盒😂