本文目录

- 低压非隔离DCDC开关稳压器设计 – Part 1 原理图设计

- 1-STEP 1: 选择拓扑结构

- 2-STEP 2: 选择IC/Module

- 3-STEP 3: 选择其他器件

- 4-STEP 4: 配置外围容阻与连线

- 5-STEP 5: 验证器件热性能

- 6-STEP 6: 验证环路稳定性

- 7-STEP 7: 是否加入额外的滤波器?

- 参考资料:

低压非隔离DCDC开关稳压器设计 – Part 1 原理图设计

1-STEP 1: 选择拓扑结构

首先我们需要明确自己的需求,是要降压,升压,升/降压还是反相?

1.1-降压

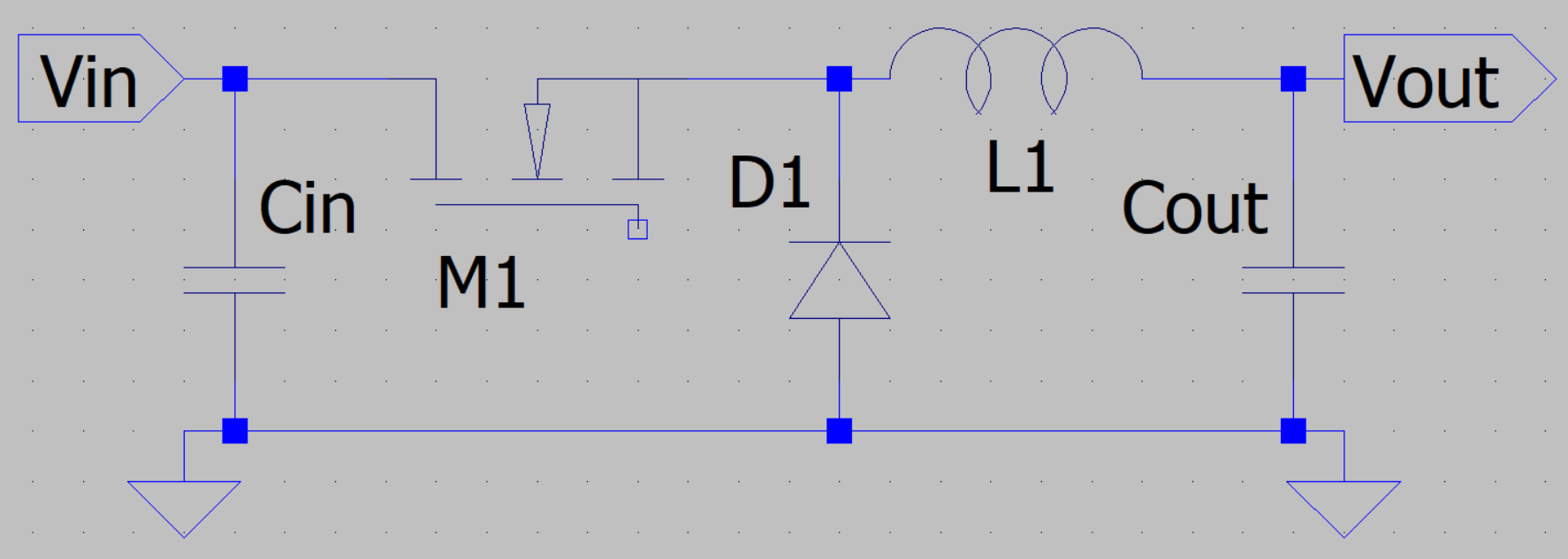

1.1.1-Buck

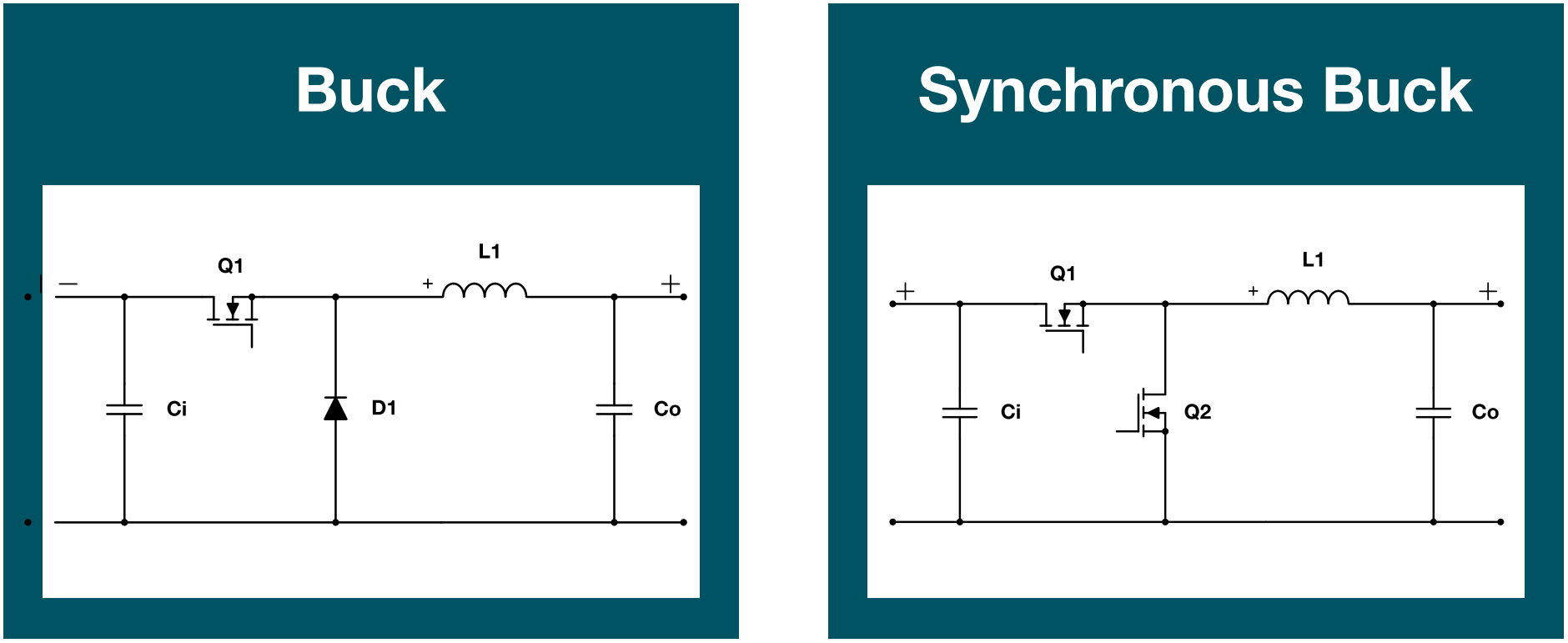

降压应当首选Buck,这种拓扑的优点是可供选择的IC极多,网上的教程,样例都很多,非常适合新手入门。Buck的输出端电压纹波较小而输入端电压纹波较大。

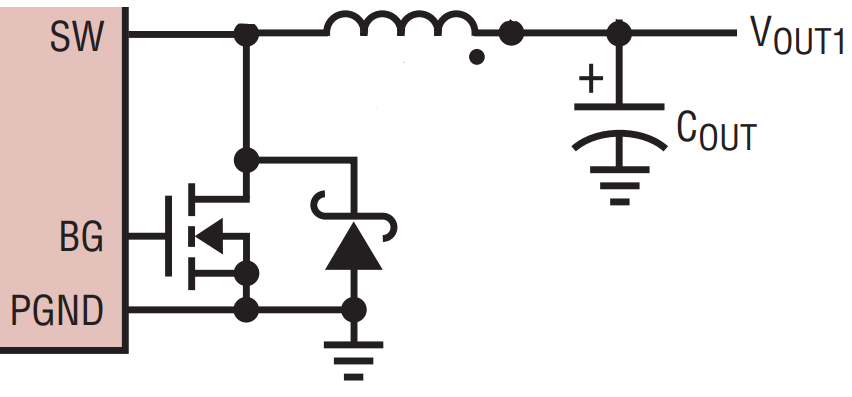

下图为其拓扑结构:

1.1.2-降压型Charge-Pump

在遇到输出电压刚好等于输入电压的\frac{1}{2}或\frac{1}{4}这种特殊情况时,例如24V转12V,可以考虑选用降压型Charge-Pump。

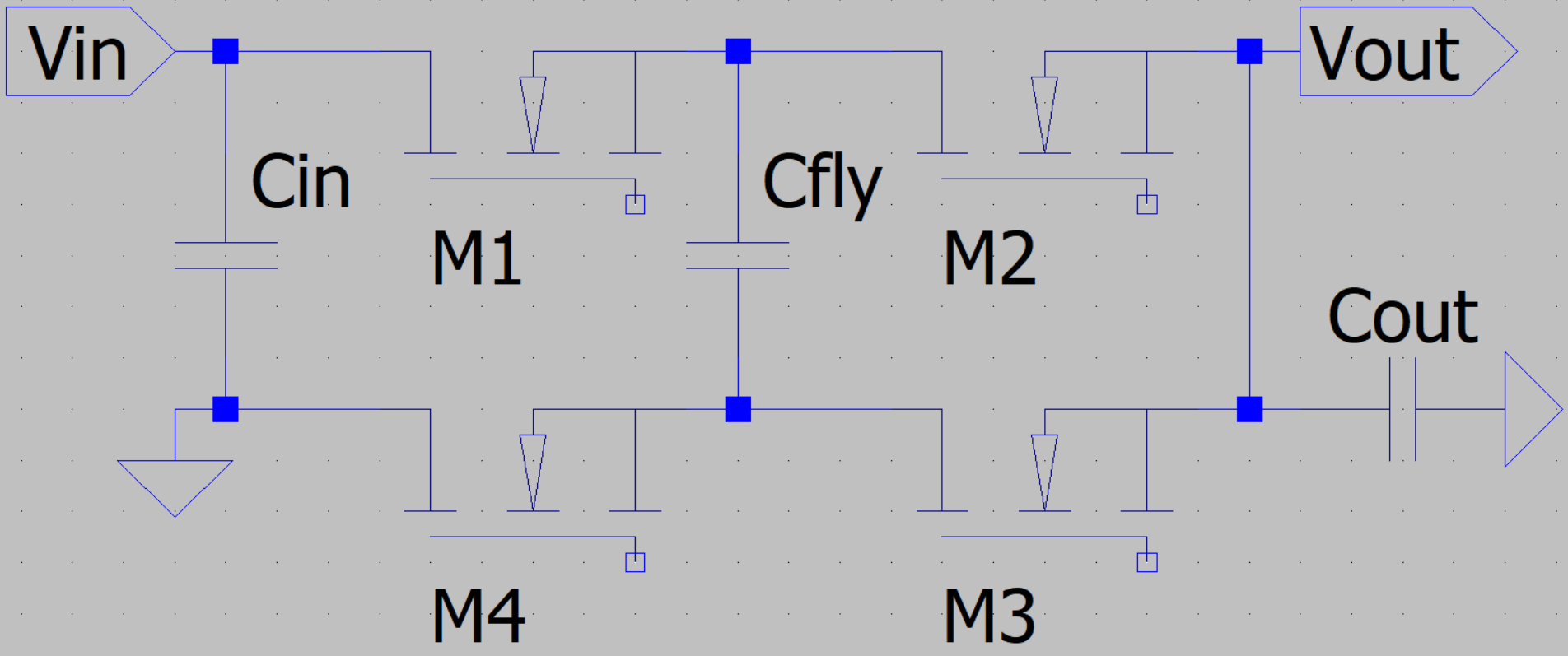

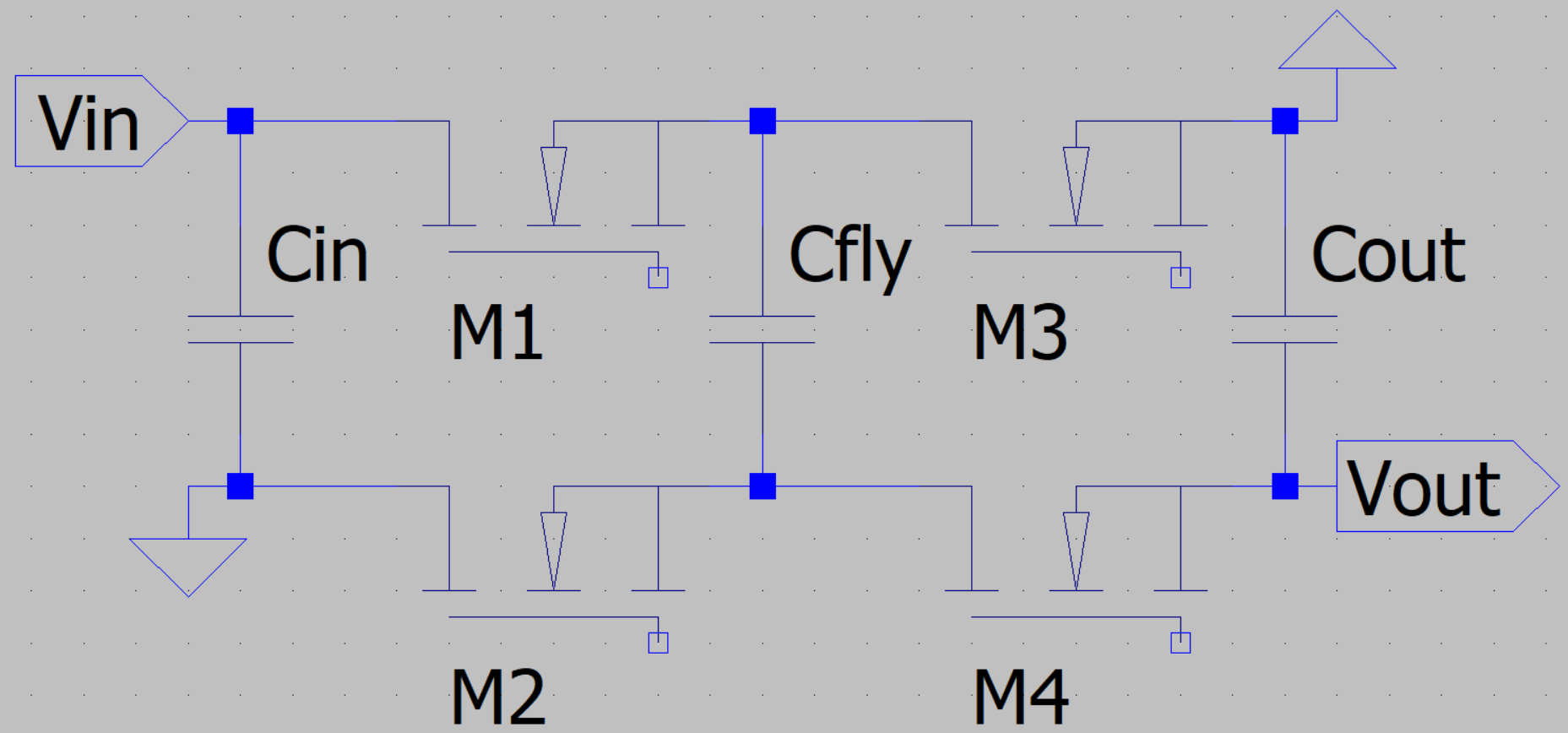

下图为其中一种\frac{1}{2}压的拓扑结构:

这种拓扑的优点是不需要使用电感,对于EMI非常友好,设计起来也比较简单,效率高。

缺点是由于是开环,负载调整率与源调整率都较差,纹波较大,并且大部分这类IC不能输出大电流,只有少数(LTC7820, RT9759, DA9313, SC8551等)可以输出大电流。

大电流降压型Charge-Pump常见于手机快充降压。

1.2-升压:

1.2.1-Boost

升压应当首选Boost。

这种拓扑的优点和Buck基本一样,但是它的输出端电压纹波较大而输入端电压纹波较小。

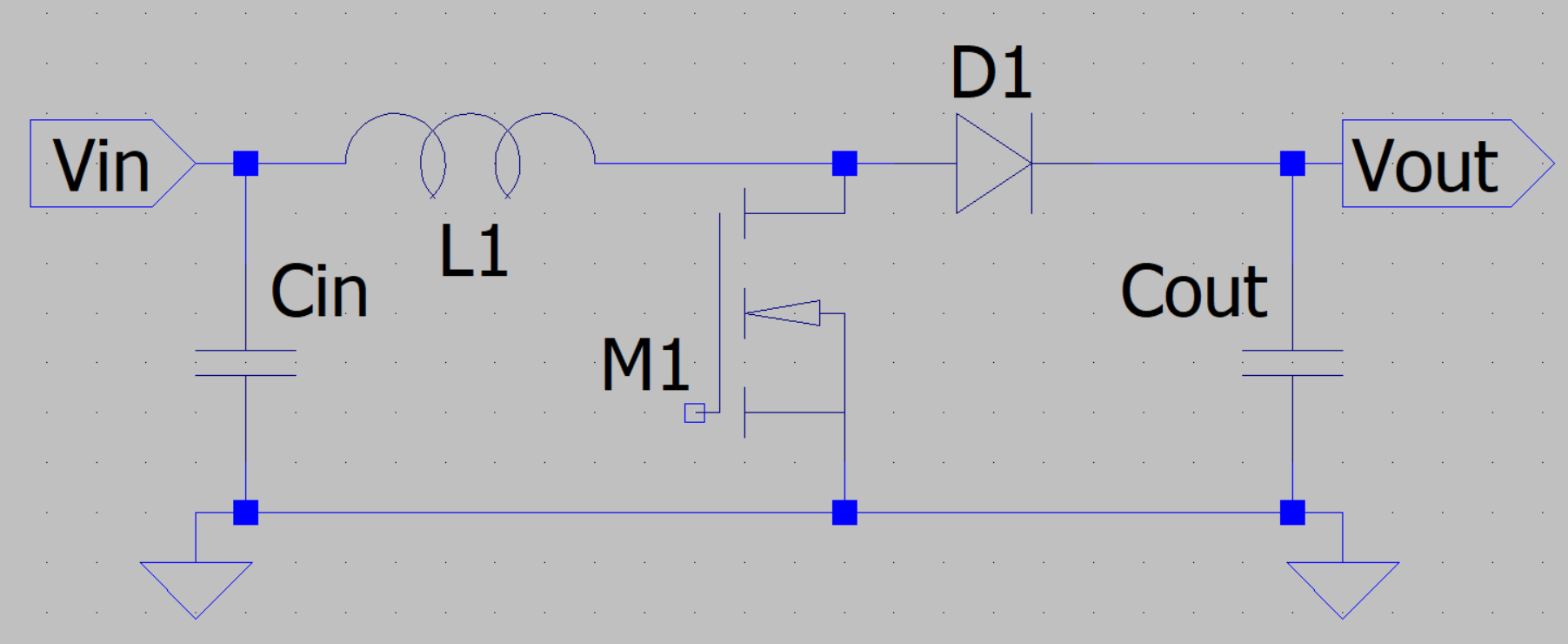

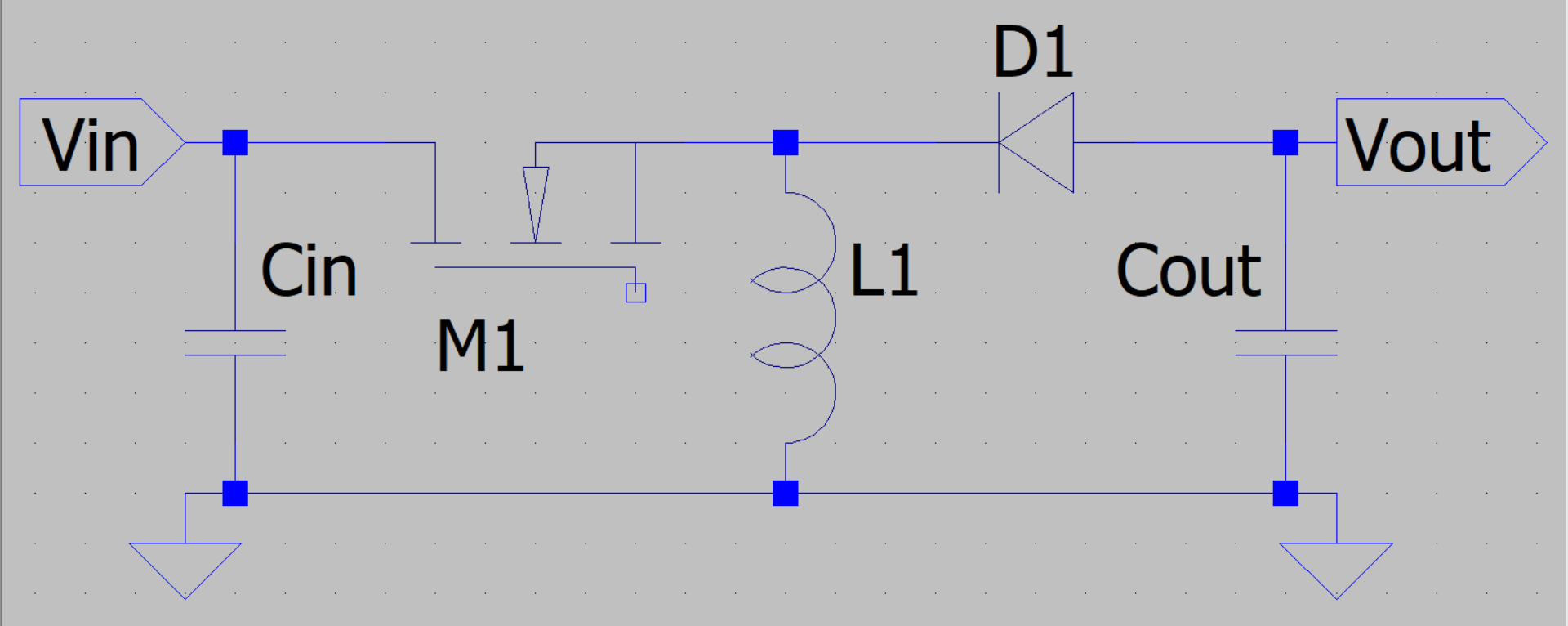

下图为其拓扑结构:

Boost还有一个问题是负载断开的问题,当IC不工作时,输入与输出不会断开,电流由输入流经电感与二极管至输出,此时V_{IN}≈V_{OUT};可以在回路上串联一个PMOS来解决这一问题(下图中M1),IC不工作时,电阻将M1的栅极上拉至与源极同电位,此时V_{GS}=0,M1关断,来实现负载断开。

1.2.2-升压型Charge-Pump(Doubler)

在遇到输出电压刚好等于输入电压的两倍或4倍这种特殊情况时,例如12V转24V,可以考虑选用升压型Charge-Pump。

它的优缺点与降压型Charge-Pump基本相同,不同的是大电流适用的IC更少,似乎只有LTC7820。

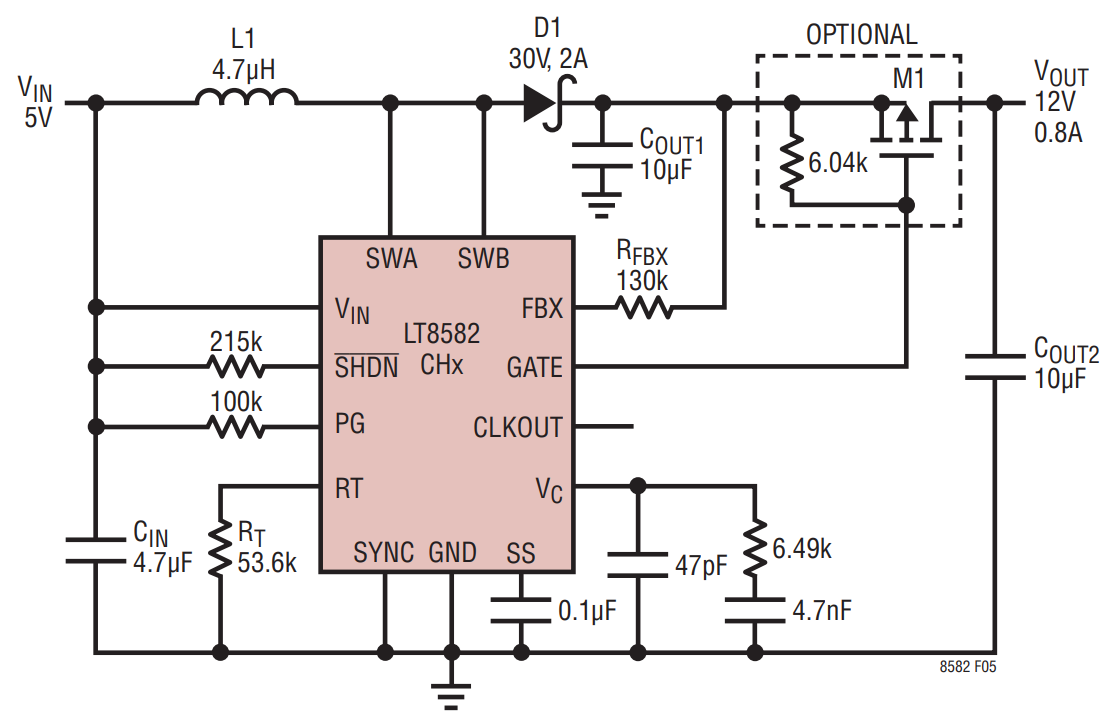

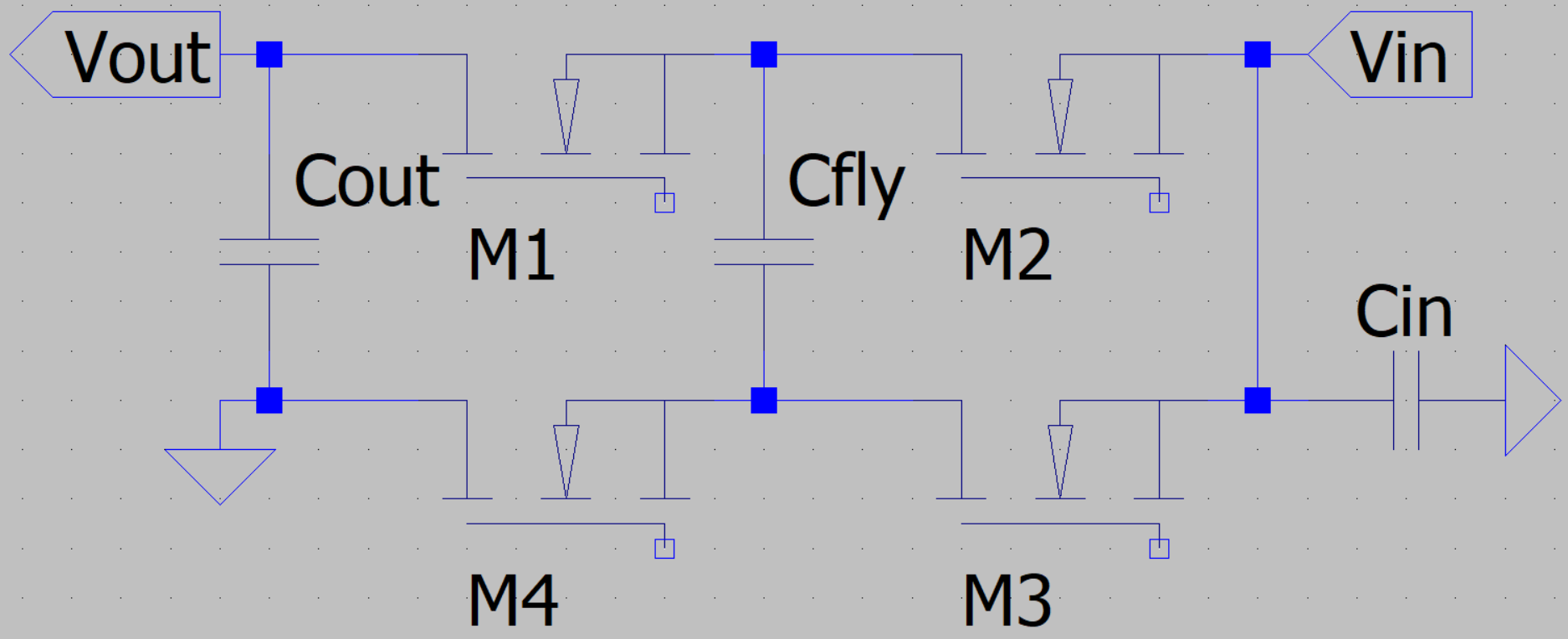

下图为其中一种倍压的拓扑结构:

1.3-升/降压

1.3.1-Buck-Boost

Buck-Boost是常用的一种升降压拓扑,通过使用4个开关,在输入电压大于输出电压时工作在Buck状态(仅M1与D1在开关),在输入电压小于输出电压时工作在Boost状态(仅M2与D2在开关),来实现升/降压。

由于其在任意一种状态下,都在大电流回路上串联了一个开关,这导致了它的效率会低一些。

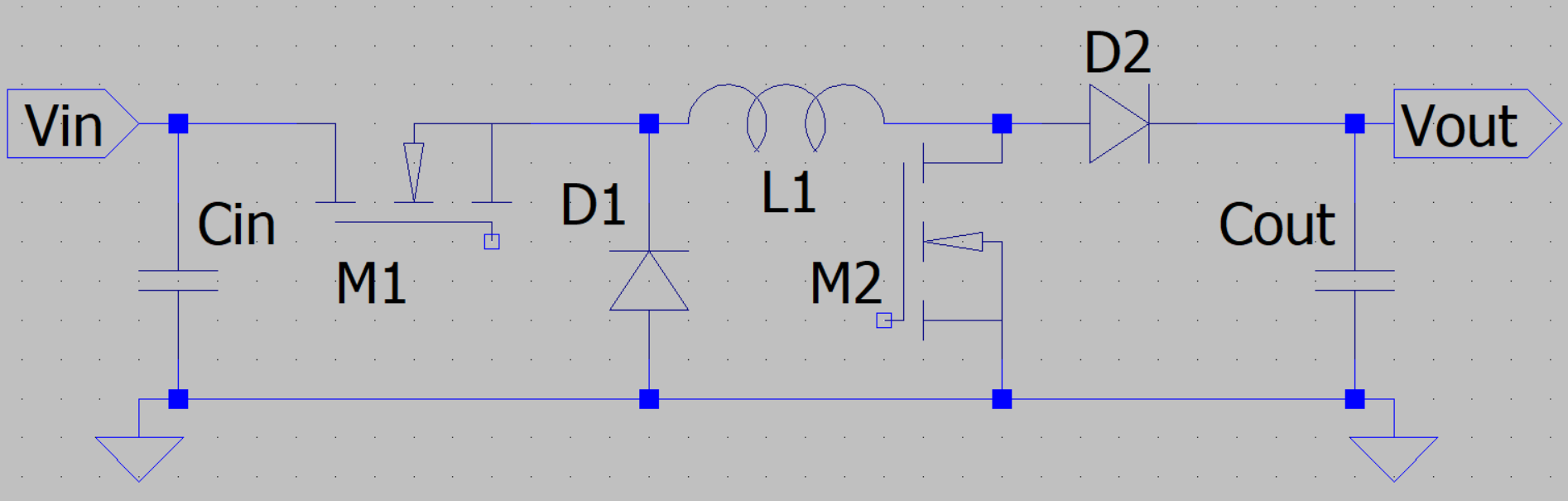

下图为其拓扑结构:

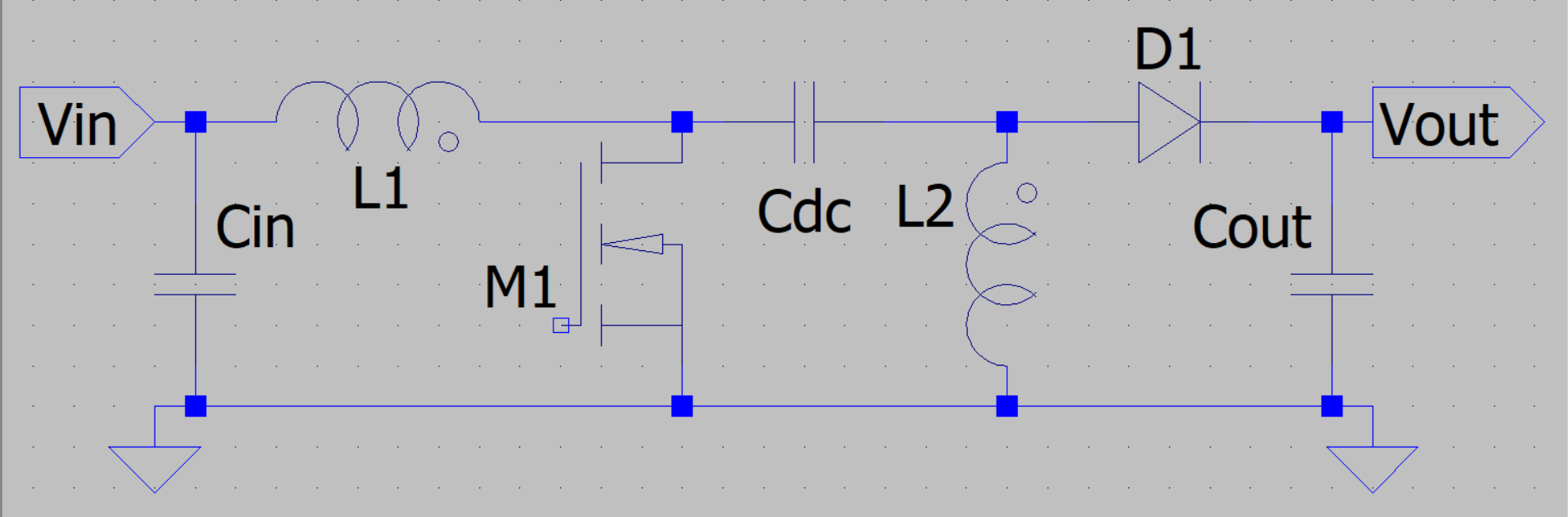

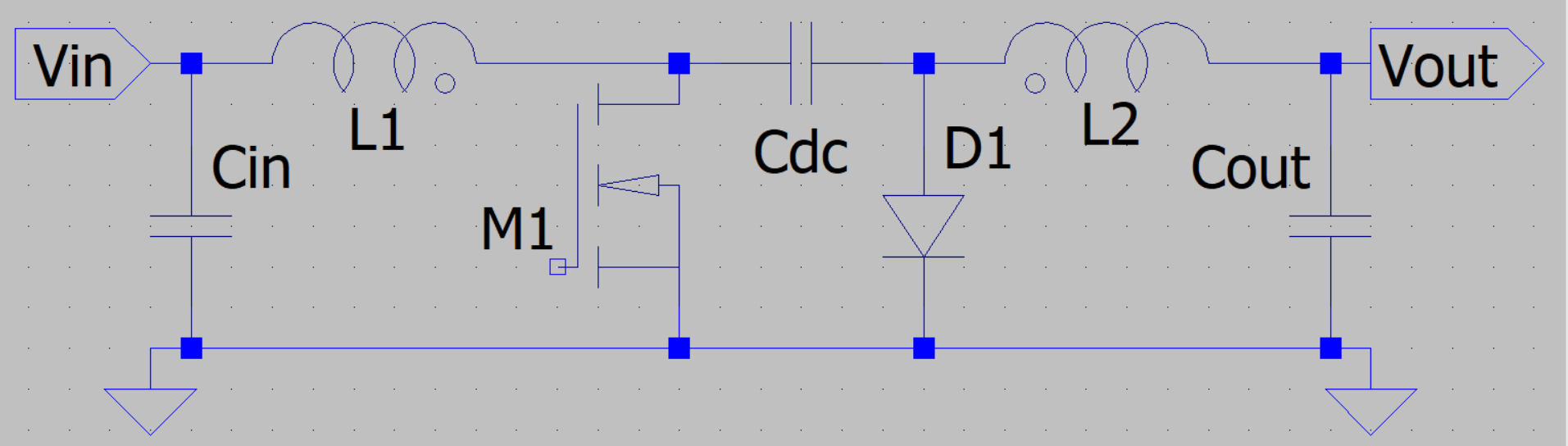

1.3.2-SEPIC

SEPIC的优势在于它可以用普通的非同步整流Boost转换器或控制器来搭建,这让它的应用范围很广。

SEPIC的缺点是它的效率通常稍低,并且对功率开关的耐压和最大电流要求略高。

SEPIC需要注意开关节点的耐压与开关限流,V_{SW_{MAX}}应当大于V_{IN}+V_{OUT},I_{SW_{MAX}}应当大于I_{IN}+I_{OUT}。

SEPIC还要注意耦合电容C_{dc}耐压应当大于V_{IN}。

下图为其拓扑结构:

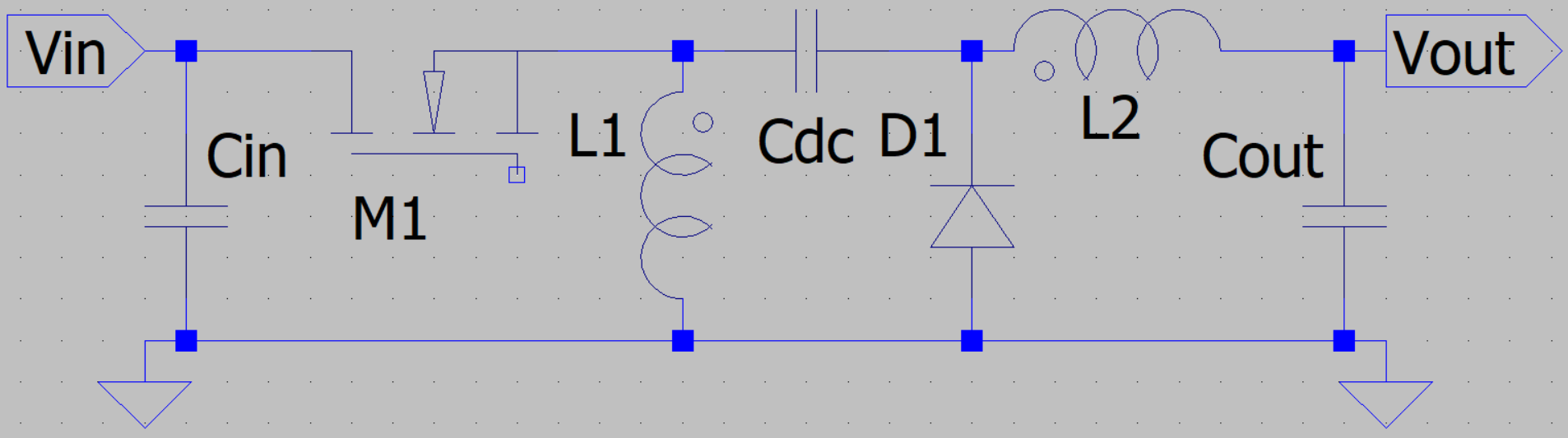

1.3.3-ZETA

较为少见的ZETA也是类似SEPIC的升降压拓扑。但注意,与SEPIC不同,ZETA不能简单的由普通的非同步Buck转换器来搭建,因为ZETA拓扑的开关节点需要承受负压,而除了Linear的个别IC,其余Buck IC的开关节点基本都不能耐受负压。

ZETA可以由专用的ZETA IC(极少),或上管为PMOS的控制器,或普通的Buck控制器来搭建。

下图为其拓扑结构:

专用的ZETA IC不多讲,这种IC很少,而且它们的数据手册里也写清楚了。

对于上管为PMOS的控制器而言,以TPS40200为例,由于不需要自举驱动,所以没有SW节点,也就不存在需要耐受负压的要求了,可以较为简单地搭建ZETA电路。缺点是由于采用的是PMOS,其RDS(ON)相比于NMOS大一些,所以效率会低一些。

对于普通的Buck控制器而言,以LM5116为例,它的上下管均采用NMOS,需要自举驱动,所以理论上SW引脚应当接到上管的漏极,但是这个节点会产生负压,而SW引脚又不能耐受负压,所以我们需要把SW引脚接到下管的源极,然后用下图所示的电路来进行电平移位,来让上管正常工作。

1.4-反相(产生负压)

1.4.1-反相型Charge-Pump

反相型Charge-Pump是一种较为简单的反相拓扑,其优缺与其他Charge-Pump基本一致,不同的是可选的IC较多,但同样,支持大电流的极少。部分反相Charge-Pump还集成了LDO,如LM27762,LTC3260等,可以实现单片完成正压到正负压的转换,并且生成的电源比较干净,是小功率模拟设备(如运放)供电较为理想的选择,不过目前(2023.1)这几种IC涨价都非常厉害。

下图为其拓扑结构:

1.4.2-Inverting-Buck-Boost

Inverting-Buck-Boost是很常用的一种拓扑,可以由普通的Buck IC来搭建,这让它的IC选择范围非常广。

Inverting-Buck-Boost的缺点是它在输入端与输出端产生的纹波都较大,并且对器件的耐压要求较高,由于其以负压作为"地",所以要求其输入耐压>|V_{IN}|+|V_{OUT}|。

下图为其拓扑结构:

1.4.3-Ćuk

Ćuk为一种与SEPIC对偶的拓扑,可以由支持负压反馈的Boost IC(常见于Linear)或专用的Ćuk IC搭建。

Ćuk的缺点与SEPIC一样,效率通常稍低,并且对功率开关的耐压和最大电流要求略高。

Ćuk的注意事项与SEPIC类似,开关节点的耐压V_{SW_{MAX}}应当大于V_{IN}+|V_{OUT}|,开关限流I_{SW_{MAX}}应当大于I_{IN}+|I_{OUT}|。

但与SEPIC不同的是,Ćuk的耦合电容C_{dc}耐压应当大于V_{IN}+|V_{OUT}|。

下图为其拓扑结构:

1.5-正负压

1.5.1-SEPIC+Ćuk

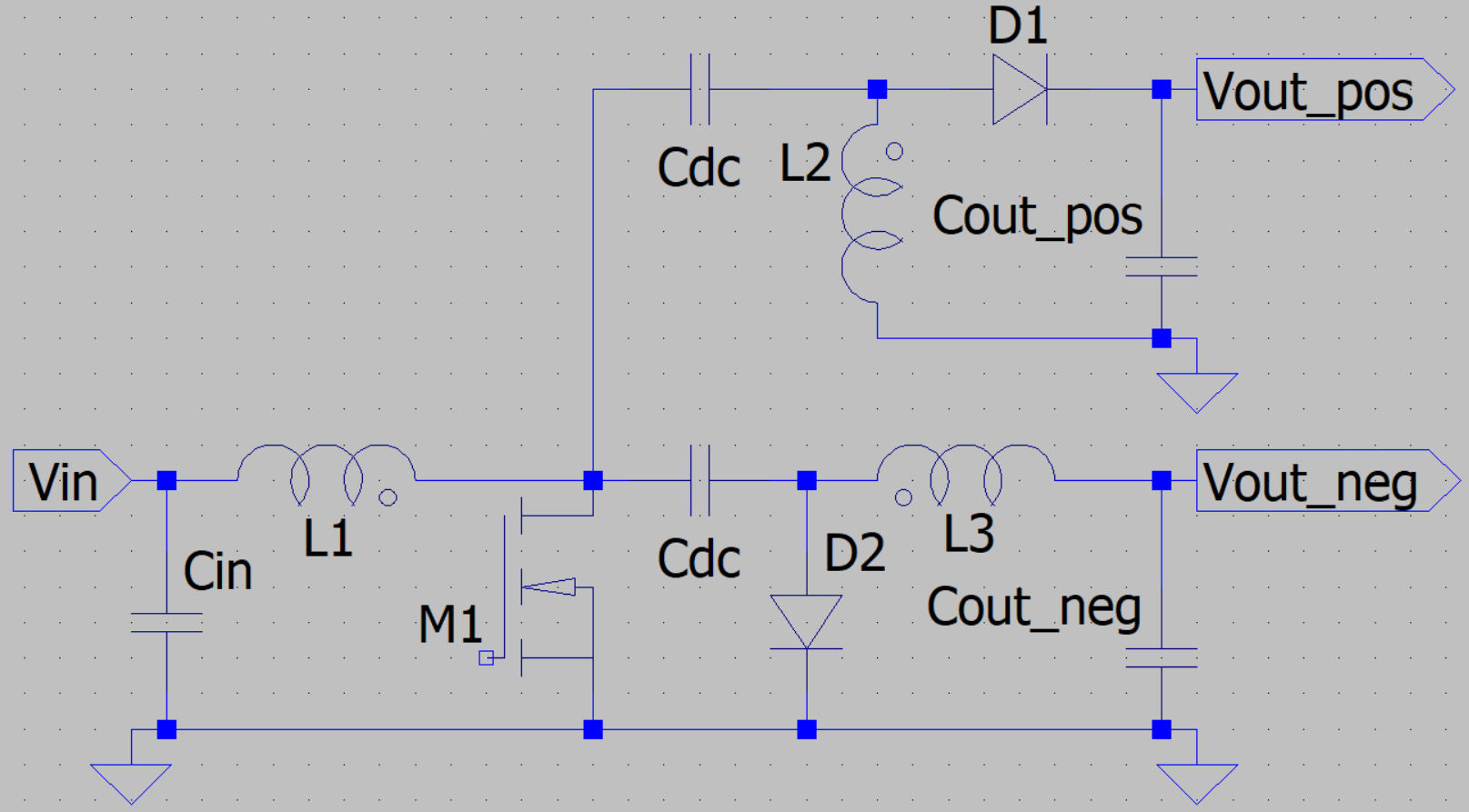

SEPIC+Ćuk是SEPIC与Ćuk拓扑的结合,可以使用普通的非同步整流Boost转换器同时实现正压与负压的升降压,非常适合用于生成运放所需的正负压。

下图为其拓扑结构:

SEPIC+Ćuk可以使用两个耦合电感,或是三个独立的电感(若使用独立电感,耦合电容之后的电感感值需要翻倍);由于正压与负压共用一个主开关管,受开关限流的影响,其电流输出能力减半。

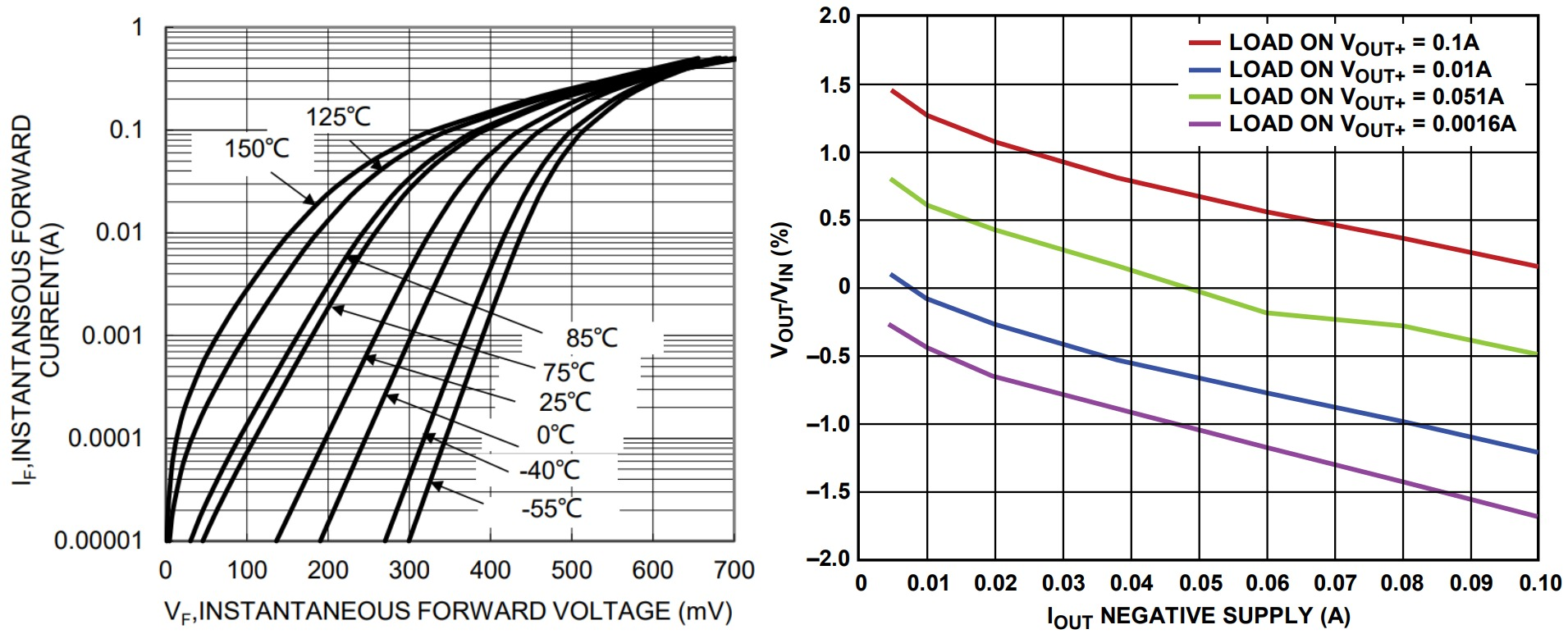

在理想情况下,|V_{OUT_{POS}}|≡|V_{OUT_{NEG}}|,因为在忽略二极管的压降与回路中器件,PCB的直流电阻影响时,|V_{OUT_{POS}}|=|V_{OUT_{NEG}}|=V_{IN}×\frac{DC}{1-DC},其中DC为开关管占空比,输出电压与输出电流无关。然而由于二极管的正向压降V_F与正向电流I_F有关(如下图左侧),并且实际器件与PCB存在直流电阻,实际使用中负压的负载调整率会略差一些(下图右侧)。

注意在输出电流极小时,正压与负压压差会较大,此时不应忽略二极管压降的影响,应当以更精确的公式|V_{OUT}|+V_F=V_{IN}×\frac{DC}{1-DC}来计算输出电压,由于在使用Boost转换器时使用正压做反馈,正压有反馈电阻R_{FB}泄流而负压无,所以此时正压存在一个较小的输出电流而负压基本没有。在这里我们以正压输出1mA,负压输出0mA,正负压均使用B340肖特基二极管,环境温度25℃计算,则|V_{OUT_{NEG}}|-|V_{OUT_{POS}}|≈V_F(@\frac{V_{OUT_{POS}}}{R_{FB}})-0=260mV。

为了解决上述问题,我们可以给负压输出加上一个与正压相同的泄流电阻到地,使空载时正负压输出电流同样均衡;或者改为同步整流,MOSFET较小的导通电阻R_{DS(on)}可以确保其两端电压V_{DS}小至可以忽略,使输出电压对称。

2-STEP 2: 选择IC/Module

2.1-同步整流与非同步整流(Nonsynchronous/Synchronous)

2.2-非同步整流(Nonsynchronous)

非同步整流是指拓扑中有一半的开关使用MOS或BJT,另一半用二极管(通常是肖特基)替代,这样的优点是IC设计简单,不需要考虑死区等问题,缺点是由于即使是很好的肖特基二极管,其正向压降V_F也一般大于MOS或BJT,导致效率偏低。

2.3-同步整流(Synchronous)

同步整流是指拓扑中所有的开关均采用MOS或BJT,这样,相比于非同步整流,效率一般较高。

大部分情况下,同步整流是更好的选择。

2.4-转换器,控制器与模块(Module/Converter/Converter)

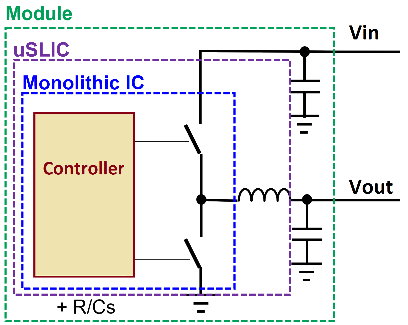

2.5-模块(Module)

模块一般为同步整流,集成了功率开关与电感,一般仅需外加输入输出电容及部分配置容阻即可工作,部分模块甚至集成了输入输出电容与部分配置容阻,可以直接当三端稳压器使用。

模块可以大幅度减小设计时间,减小占板面积,优化EMI。

但通常价格昂贵,不好买并且不适用于大功率(百瓦以上)。

2.6-转换器(Converter)

转换器是指内置功率开关,外置电感与电容的IC。

通常转换器的成本较低,输出能力中等,外围配置较简单,适用面最广,是最常见的种类。

2.7-控制器(Controller)

控制器一般分为集成了MOS驱动的控制器和PWM控制器。

2.7.1-PWM控制器

内部仅有控制逻辑部分,只能输出没有驱动能力的PWM波。

PWM控制器需要配合DrMOS(有些厂家也叫功率级PowerStage)或栅极驱动器+MOS工作。

一般用于超大电流(如100A以上),多相供电场景,比如处理器核心供电。

2.7.2-集成了MOS驱动的控制器

内部除控制逻辑外,还集成了MOS驱动,需要外部电感,电容与MOS,适用于有较大电流需求的场景。

大部分控制器都指集成了MOS驱动的控制器。

2.8-IC/模块的性能指标选择

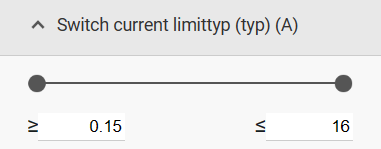

2.8.1-开关限流与最大输出电流

一般情况下,开关限流表示为 I_{SW_{MAX}},最大输出电流表示为I_{OUT_{MAX}}。

注:此处为简单起见,以内置功率管的转换器为例,未考虑电感纹波电流。

Buck变换器最为简单,最大输出电流I_{OUT_{MAX}}=开关限流I_{SW_{MAX}},通常厂家直接以最大输出电流I_{OUT_{MAX}}标注。

Charge-Pump与Buck类似,通常厂家直接以最大输出电流I_{OUT_{MAX}}标注,不过需要注意的是在输出电流达到标称最大输出电流时,由于其输出内阻(与飞跨电容C_{Fly},开关频率F_{SW}和开关管导通内阻R_{on}有关)的关系,输出电压可能已经有较为明显的下降。

Boost变换器的最大输出电流与输入输出电压有关,忽略损耗与电流纹波,I_{OUT_{MAX}}=I_{SW_{MAX}}×(\frac{V_{IN}}{V_{OUT}}),厂家通常只标注开关限流I_{SW_{MAX}},需要根据实际输入输出电压情况计算I_{OUT_{MAX}}。

SEPIC,Ćuk与ZETA变换器最大输出电流同样与输入输出电压有关,忽略损耗与电流纹波,I_{SW_{MAX}}=I_{IN}+I_{OUT}=I_{OUT}(1+\frac{V_{OUT}}{V_{IN}}),故I_{OUT_{MAX}}=I_{SW_{MAX}}×(\frac{V_{IN}}{V_{IN}+V_{OUT}}),与Boost转换器类似,需要根据实际输入输出电压情况计算I_{OUT_{MAX}}。

Inverting-Buck-Boost变换器的最大输出电流也与输入输出电压有关,忽略损耗与电流纹波, |I_{OUT(NEG)_{MAX}}|=I_{SW_{MAX}}×(\frac{V_{IN}}{V_{IN}+|V_{OUT}|}),由于Inverting-Buck-Boost通常采用普通的Buck转换器搭建,所以这里的I_{SW_{MAX}}取数据手册中的I_{OUT_{MAX}}即可,注意,由于改变了拓扑,此处负压的最大输出电流I_{OUT(NEG)_{MAX}}≠数据手册中的最大输出电流I_{OUT_{MAX}}。

SEPIC+Ćuk转换器在对称负载下,|I_{OUT_{POS_{MAX}}}|=|I_{OUT_{NEG_{MAX}}}|=\frac{1}{2}×I_{SW_{MAX}}×(\frac{V_{IN}}{V_{IN}+V_{OUT}}),与SEPIC,ZETA和Ćuk这三者类似。

2.8.2-耐压与输出电压

Buck变换器的最大输出电压V_{OUT_{MAX}}=V_{IN}(若所选IC支持100%占空比),一般不需关心IC耐压问题。

Boost变换器的最大输出电压V_{OUT_{MAX}}=V_{SW_{MAX}},需注意开关节点的耐压,并且建议留一些余量。

SEPIC,Ćuk,ZETA与SEPIC+Ćuk变换器的最大输出电压|V_{OUT_{MAX}}|=V_{SW_{MAX}}-V_{IN_{MAX}},使用时需特别注意,开关耐压V_{SW_{MAX}}应当大于最大输出电压|V_{OUT_{MAX}}|+最大输入电压V_{IN_{MAX}}。

Inverting-Buck-Boost变换器通常由Buck变换器搭建而来,将其"地"作为负压输出,由于Buck变换器的耐压通常指输入引脚与地引脚之间的耐压,所以要求最大输出电压|V_{OUT_{MAX}}|+最大输入电压V_{IN_{MAX(Actual)}}小于数据手册中标注的最大输入电压V_{IN_{MAX(Datasheet)}},注意区分两个V_{IN_{MAX}}。

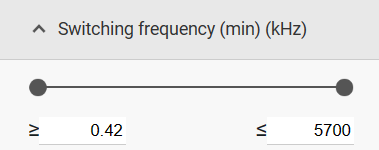

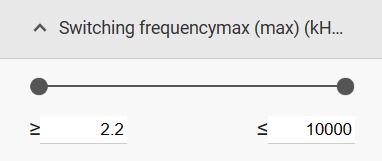

2.8.3-开关频率(Switching Frequency)

一个DCDC变换器的开关频率通常对以下四个方面有较为显著的影响:

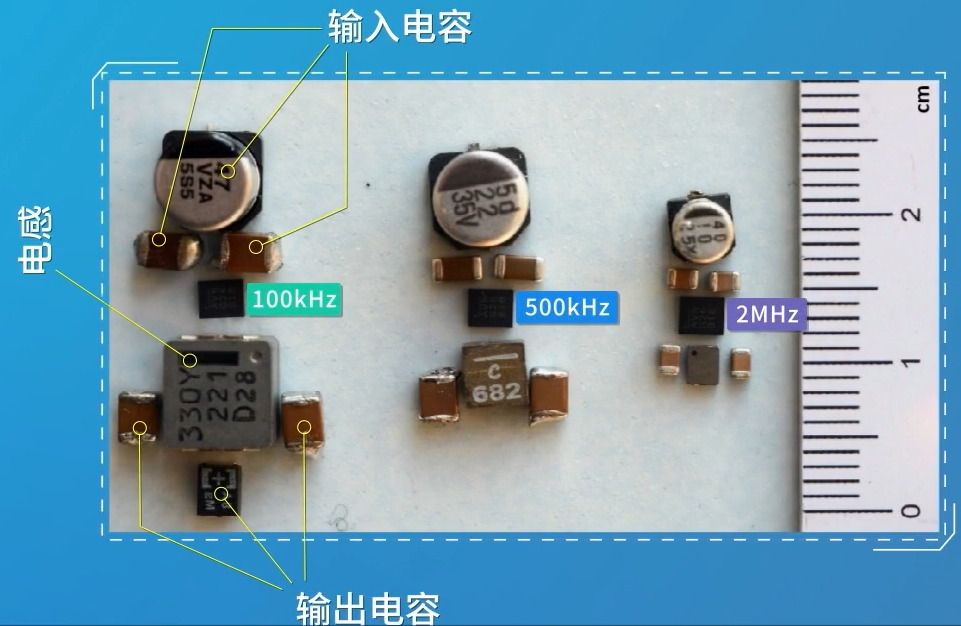

2.8.3.1-元件体积

开关变换器中储能元件为电容与电感,它们在每个开关周期中完成储能->放能的循环;开关频率越高,他们在每个循环中所需存储的能量就越少,相应的,它们的体积也会越小。

或者我们可以这样理解,一般来说,L、C的值与开关频率成反比关系(因为相当于控制其阻抗一定嘛),而L、C的值一般与他们的\sqrt{体积}成正比关系(想想电感的绕制结构和电容那两片夹板结构),所以跟体积有关。

2.8.3.2-纹波

在外围器件相同的情况下,开关频率越高,输出电压纹波越小。

以Buck为例,我们可以把输出端的电感和电容看作LC低通滤波器,频率越高,衰减越大,输出电压纹波越小,并且高频的纹波更容易被后级的滤波器滤除。

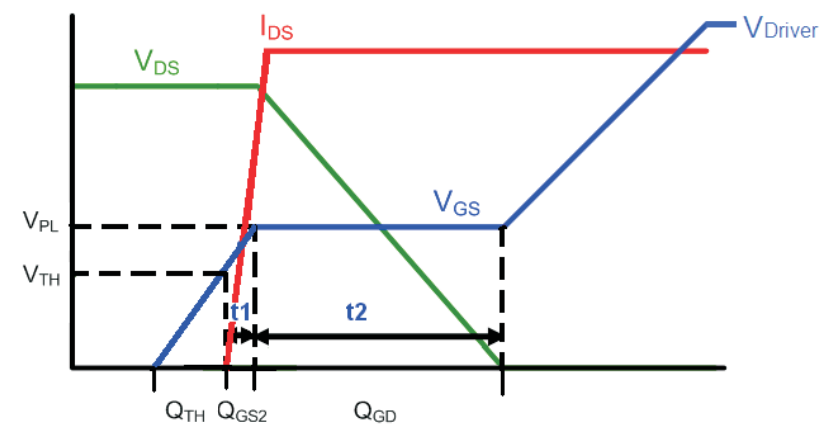

2.8.3.3效率

常见的DCDC开关管在从关断到开启过程中的电压电流波形如下图所示:

MOS管存在栅极电荷Q_g这一参数,其栅极可以看作一个电容,并且由于栅极驱动器的驱动能力有限,并且存在栅极电阻R_G,所以并不能瞬间对栅极的电容完成充电,所以MOS的开启并不是瞬间完成的。而MOS的导阻R_{DS_{(ON)}}可以认为与栅极的电压负相关,在开启过程中,你可以理解为MOS类似滑动变阻器,由一个很大的电阻变化为一个很小的电阻,这个过程中存在一个电阻不大不小的时间段,这时MOS上耗散的功率远大于导通或关断时,我们将因MOS开启或关断而损失的能量称之为开关损耗。由于MOS的Q_g固定,栅极驱动器的驱动能力也固定,所以每次开关时损耗的能量近似一样,而单位时间内开关次数越多,损耗的能量就越多,所以在更高的开关频率下,效率会降低。

我们可以按照上图中MOS的电压电流波形,来计算每次开关时产生的损耗。

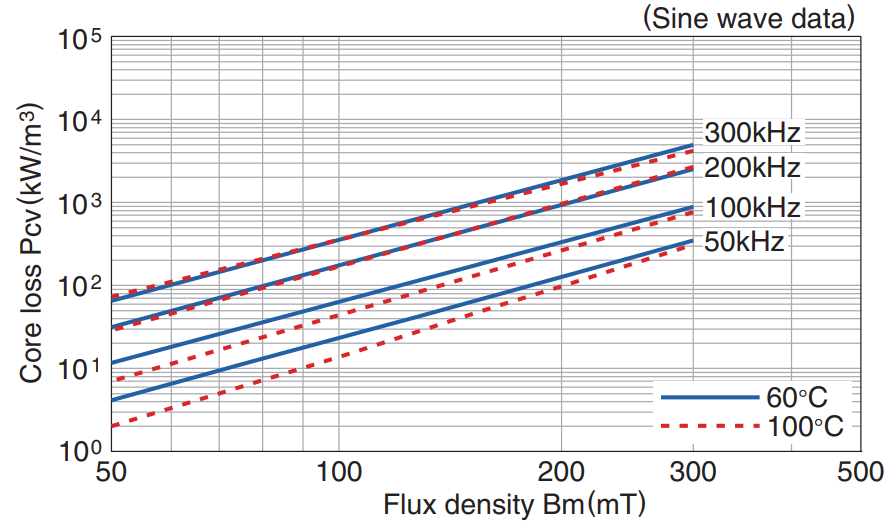

同时,电感中的磁性材料,在高频下的磁损也会变大,进一步降低效率。下图为TDK生产的PC95材质磁芯的磁损与频率的关系:

2.8.3.4-EMI

在面对EMI敏感型应用时,应当谨慎选择开关频率。

例如,在汽车电子中,DCDC常用的开关频率为300kHz以下,300kHz~530kHz或1.8MHz以上,这是为了让开关频率避开敏感的频率区间,防止干扰到其他设备的正常工作。如果你的应用中也有敏感频点,那么你应当要让DCDC的开关频率避开敏感频点。

开关频率的提升除了降低效率外,还会使开关回路中的高频能量增加,而高频能量更容易变为电磁波发射出去,这会使DCDC变换器对外辐射的能量变大,可能会加重EMI的问题。

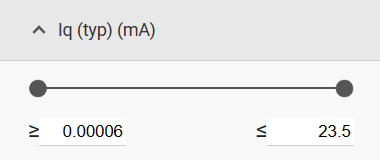

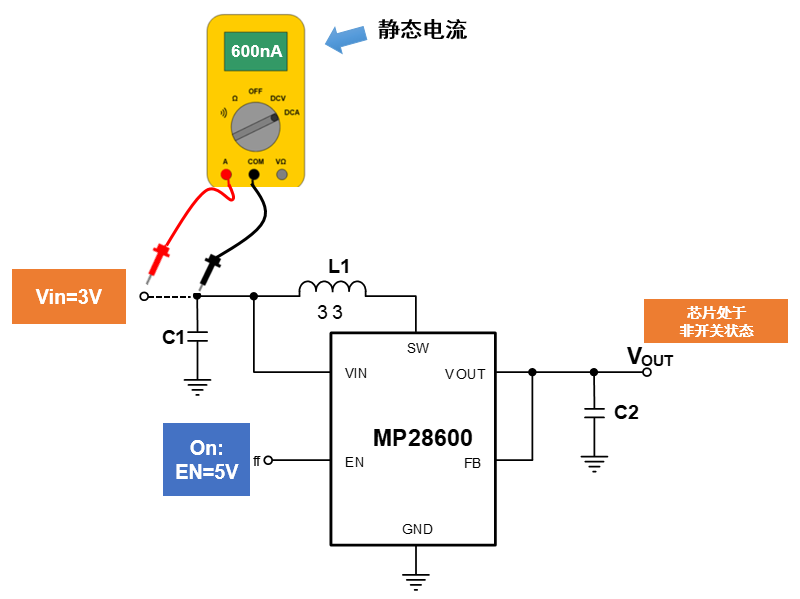

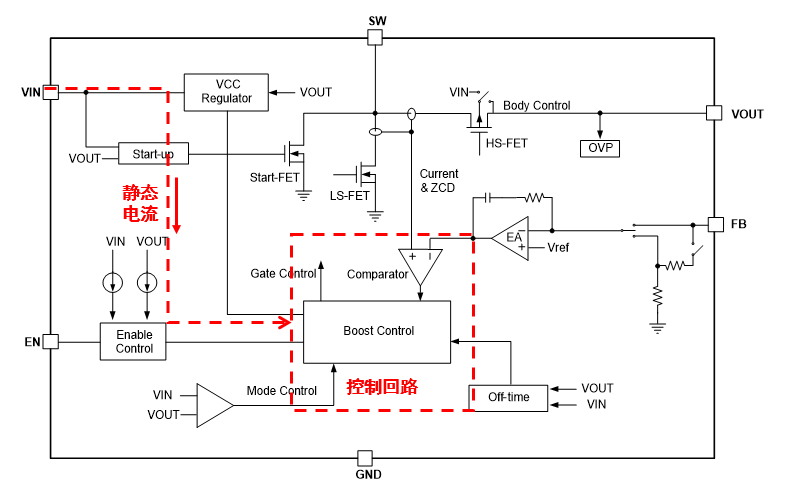

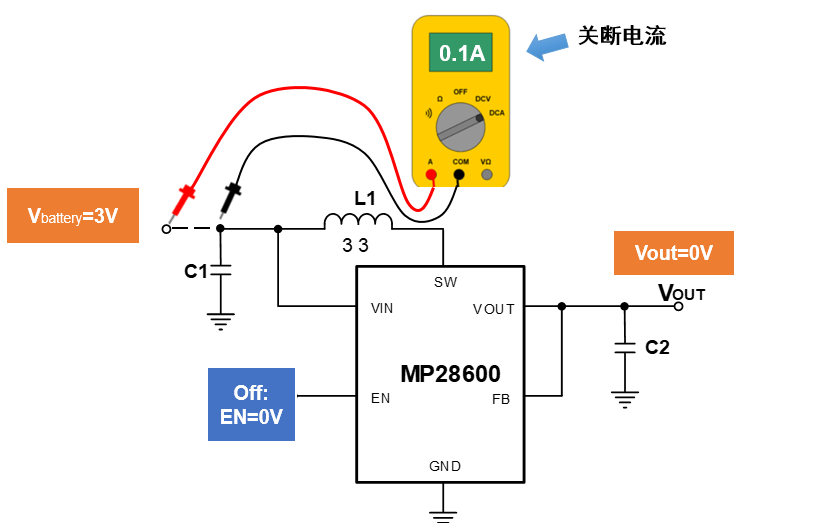

2.8.4-静态电流

静态电流 (I_Q/I_{supply}/Quiescent Current) 是指,在芯片使能但没有进入开关状态或者空载的情况下,所消耗的电流。静态电流主要由IC内部的控制电路所消耗。

静态电流主要由IC内部的控制电路所消耗。

在需要待机且功耗敏感的场合,如由干电池供电的移动设备中,静态电流是较为关键的指标,更小的静态电流意味着更长的续航。

注意区分关断时的关断电流与空载时的静态电流,关断电流是指当芯片处于关断状态但仍然与电源连接时,所消耗的电流。

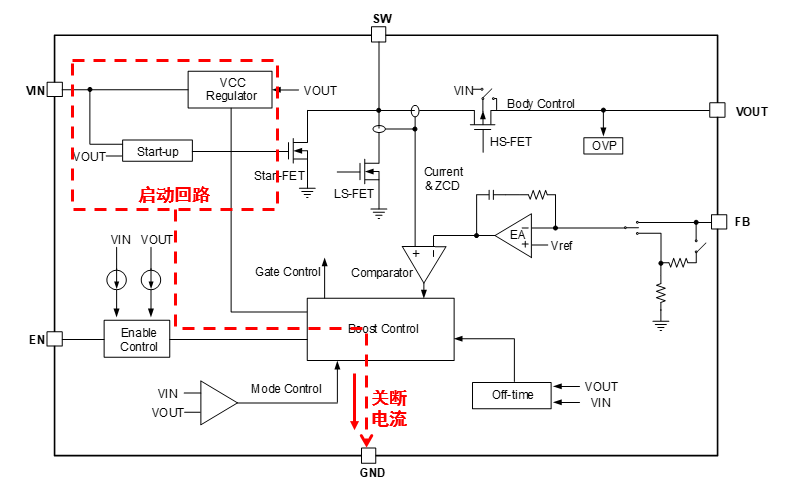

关断电流主要由IC内部的启动电路消耗。

不同厂家不同IC的特性宣传中标注的不一样,具体请参考手册。

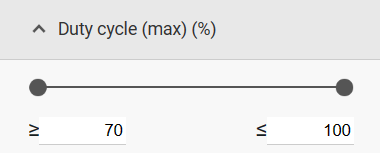

2.8.5-最大占空比(Max Duty Cycle)

转换器的最大升压比/降压比与最大占空比有关,具体可分拓扑计算。

注意此处标注的最大占空比仅在较低的开关频率下可以达到,当开关频率较高时,受限于最小导通时间/最小关断时间,占空比范围会缩小。

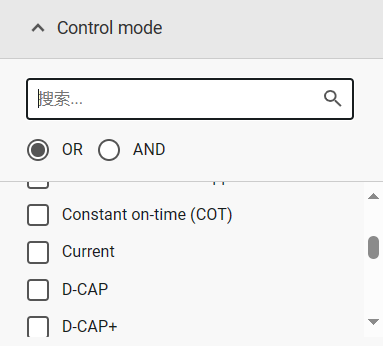

2.8.5-控制模式(Control Mode)

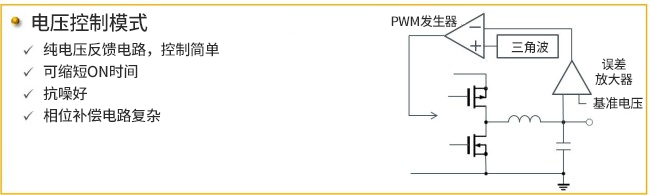

2.8.5.1-电压型(Voltage Mode)

电压模式控制是最基本的方式,反馈环路只反馈输出电压。误差放大器将输出电压和基准电压相减后,送入比较器与三角波做比较,来确定PWM波的占空比,进而来控制输出电压。此方式的优点在于纯电压的反馈环路可进行较简单的控制、可缩短ON时间、抗噪好。其缺点是,由于双极点的存在,补偿网络设计可能比较麻烦;并且瞬态响应较慢。

通常采用电压控制模式的IC都为较老的型号,但也有新型的采用带前馈的电压控制模式的IC。

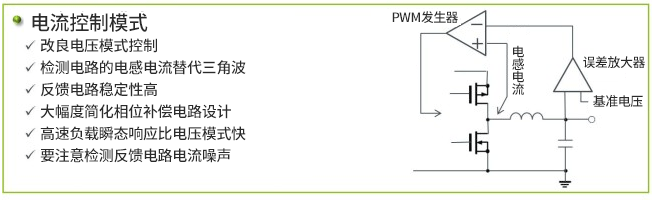

2.8.5.2-电流型(Current Mode/Peak Current Mode)

电流模式控制是对电压模式控制的改良。是通过DCR或检流电阻,检测电感电流或功率管电流的方式,取代电压模式中的三角波。反馈环路分为电压外环与电流内环,控制虽变得比较复杂,不过因为这是单极点系统,补偿网络设计比较简单。其他优点还有反馈环路的稳定性高,负载瞬态响应比电压模式快速。其缺点是,因电流检测敏感故所以抗噪性能弱;不过大部分转换器都内置了检流电路,故此问题的影响不大。

大部分较新的DC-DC IC都为电流模式。

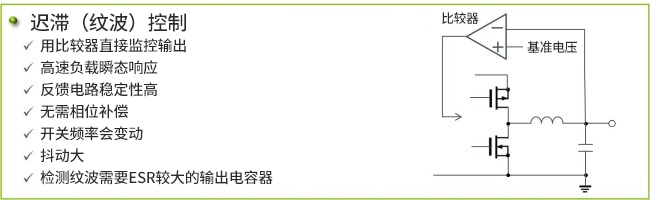

2.8.5.3-迟滞控制(Hysteretic/COT/ACOT/D-CAP/DCS)

迟滞控制不通过误差放大器而通过比较器直接监控输出电压,借助纹波,当检测到输出电压的电压低于/高于的设定的阈值后,由比较器直接控制功率管上管的ON/OFF。迟滞控制的方法有两种,采用比较多的方法是当输出电压低于设定阈值后,开关管固定导通一段时间Constant On Time);采用比较少的方法是当输出电压高于设定阈值后,开关管固定截止一段时间(Constant Off Time)。

迟滞控制的优点是拥有最快的瞬态响应,并且无环路补偿的问题;但缺点是需要依赖输出电容ESR或纹波注入电路来保持稳定。

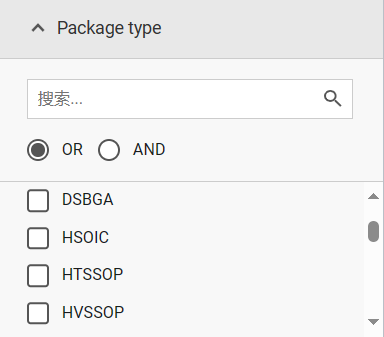

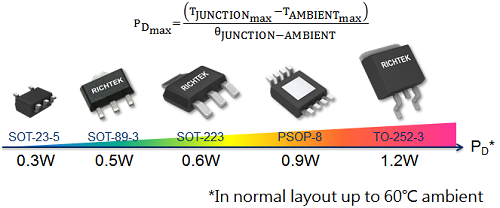

2.8.6-封装(Package Type)

对于转换器与模块这类内部集成了功率器件的IC来说,除非输出电流很小,否则强烈建议选择热性能较好的封装,如带有散热焊盘的DFN,QFN,SO PowerPAD,TO-XXX等。这些封装的核心到封装散热焊盘热阻θ_{JC(bottom)}通常很小,可以利用PCB或额外的散热片来进行散热,这使得这些IC在长时间进行大功率输出时,内部积累的热量能有效地散发到环境中,不至于因热量积累而触发过热保护。

无散热焊盘的小封装如SOT23等,一般更适用于小功率场景(如持续输出电流小于1A)。

对于如控制器这类内部没有集成功率器件的IC来说,因其上没有很大的功率耗散,有无散热焊盘不重要。哪个封装好买,体积小用哪个。

3-STEP 3: 选择其他器件

3.1-电感

3.1.1-直流电阻(DCR)

电感一般采用铜线绕制而成,这导致了它的等效模型并非理想电感,而是一个电感串联了一个小电阻,这个小电阻通常为毫欧量级。

由于直流电阻的存在,使得电感上会有$P=I^2×R$的热耗散,此功率耗散会导致电感的发热与系统效率的降低,通常我们希望电感的直流电阻DCR越小越好,但这需要用更粗的铜线去绕制,导致电感体积变大。实际设计中需要综合考虑体积的因素。

3.1.2-饱和电流

当流经电感的电流达到特定数值之后,由于磁芯的饱和,电流的增大会引起较为明显的电感感值下降,我们将此特定数值的电流称为电感饱和电流 (I_{SAT})。通常厂家将使电感感值下降30%的电流标注为电感饱和电流I_{SAT}(不同厂家不一样,具体以手册为准)。

实际设计中,应当确保电感峰值电流I_{PEAK}小于电感饱和电流I_{SAT},通常I_{PEAK}=1.2×I_{AVG},其中I_{AVG}为电感平均电流,电感纹波电流以I_{AVG}×40\%计。

3.1.3-温升电流

温升电流 (I_{RMS})通常指使电感温度相对环境温度(通常为25℃)上升特定数值(通常为40℃)的电流大小,以均方根计。

实际设计时,一般要确保电感平均电流I_{AVG}小于电感温升电流I_{RMS},因为40℃的温升已经很高了,并且PCB上还有其他元件发热。

3.1.4-磁屏蔽

根据磁屏蔽等级,大致可将电感分为三大类:非屏蔽电感,屏蔽电感与一体成型电感。

- 非屏蔽电感(Unshielded):线圈外露,绕制在磁芯上。通常漏磁较为严重,对EMC不友好,但成本低。

- 屏蔽电感(Shielded):线圈绕制在磁芯上之后,在外部封上磁胶或套上导磁材料,形成闭合的磁路,漏磁小,对EMC较为友好。

- 一体成型电感(Molded):先将线圈预成型,再用铁粉或其他合金粉末一次压合成型,漏磁非常小,对EMC很友好,但存在耐压问题,同时成本稍高。

其中,使用磁胶做屏蔽的电感通常称为半屏蔽电感,使用铁氧体外壳做屏蔽的通常称为全屏蔽电感。全屏蔽电感的漏磁相对更小。

通常不建议选用非屏蔽电感。

3.1.5-耐压

一体成型电感由于是由铁粉压合而成,而其两引脚与外壳之间的绝缘层通常较薄,所以存在耐压问题,当电感两端电压超过其耐压时,有可能击穿绝缘层而使电流大部分流过铁粉而不是线圈,表现为感值大幅下降。

一般若电感厂家无特殊标注,一体成型电感的耐压按30V计,小型(5mm×5mm以下)以20V计,数据手册中明确标明的以数据手册为准。

除一体成型电感之外的其他类型的电感一般无耐压问题。

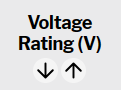

下图为CoilCraft不同类型电感的耐压。

3.1.6-自谐振频率SRF

自谐振频率,Self Resonant Frequency, 简写为SRF。

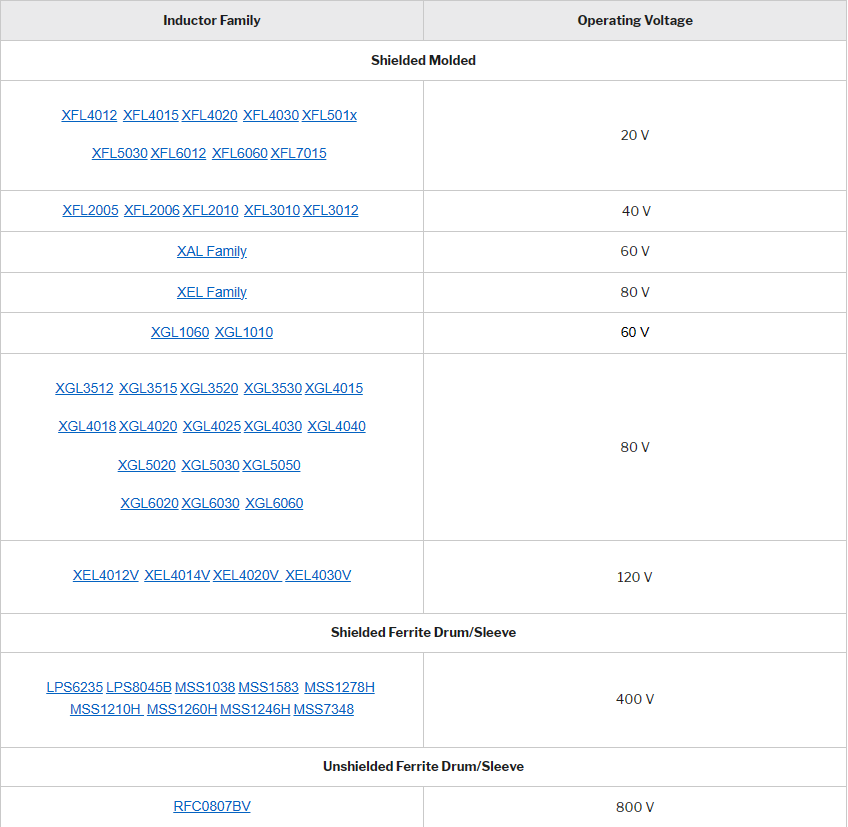

由于实际元件的非理想特性,在实际电感中,电感线圈的两端会存在一个与之并联的电容,这个电容在某一特定频率下会与电感发生并联谐振。下图为实际电感的模型:

实际上,一般电感的SRF基本都在10MHz以上,而因为要考虑效率,加上最短导通/关断时间的限制,开关频率不可能很高,因此一般在DCDC电路中,SRF都远大于开关频率,单纯从效率角度来讲,不太需要关注此参数。

但是,需要知道的是,SRF一般越大越好。更大的SRF代表着电感更理想,其并联的电容越小,由并联的电容馈通到输出端的开关噪声会越小。

3.2-输入/输出电容

常用于DCDC变换器的电容主要分为两类,陶瓷电容与电解电容。

可单独使用两种电容,也可搭配使用。

一般要求陶瓷电容的额定电压要是实际电压的1.5倍以上,电解电容则需要2倍以上。

电容容量则在确定拓扑,输入输出条件和开关频率之后,根据所期望的输出纹波与瞬态响应来计算,这一步推荐使用仿真软件或辅助设计软件来完成(参考STEP 6中,电流型/电压型 中 仿真 一节推荐的仿真软件和辅助设计软件)。

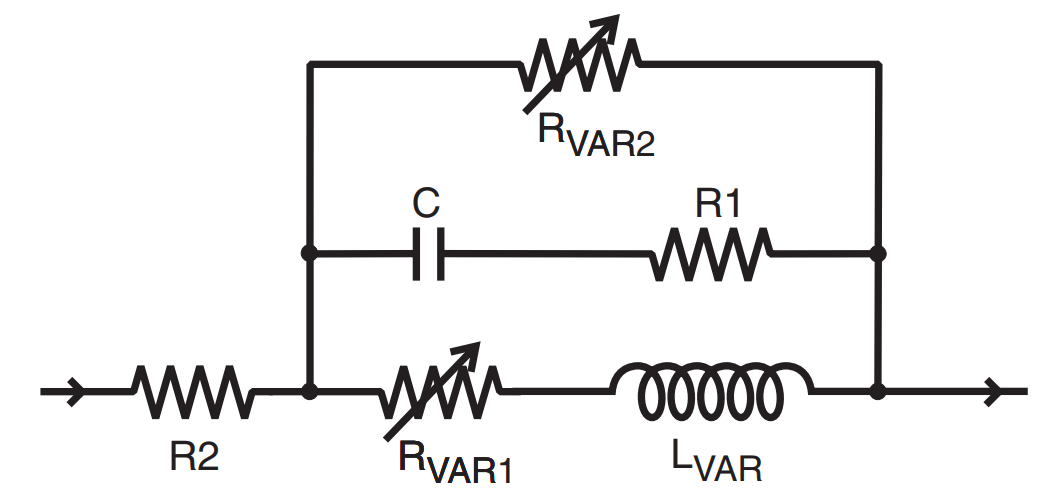

3.2.1-陶瓷电容

陶瓷电容通常具有较低的ESR与ESL,在高频段有很好的表现,但在使用时需要注意以下几个问题。

3.2.1.1-有效容值

MLCC的标称容量一般指静电容量,在设计时,需要根据实际情况计算其有效容值。

以村田的GRM188R6YA106MA73#为例,这是一款0603,10uF,35V,X5R的MLCC,我们假设将其用在DCDC的12V输出端进行滤波,计算其有效容值。

3.2.1.1.1-直流偏置

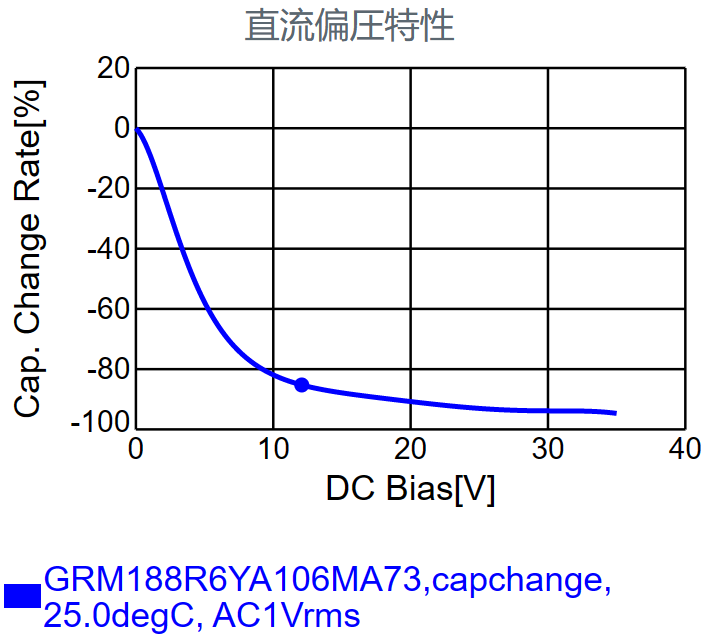

这种情况下的直流偏置约为12V,查阅容量与直流偏置关系的曲线可知,此时需要降容约85%。

3.2.1.1.2-交流电压

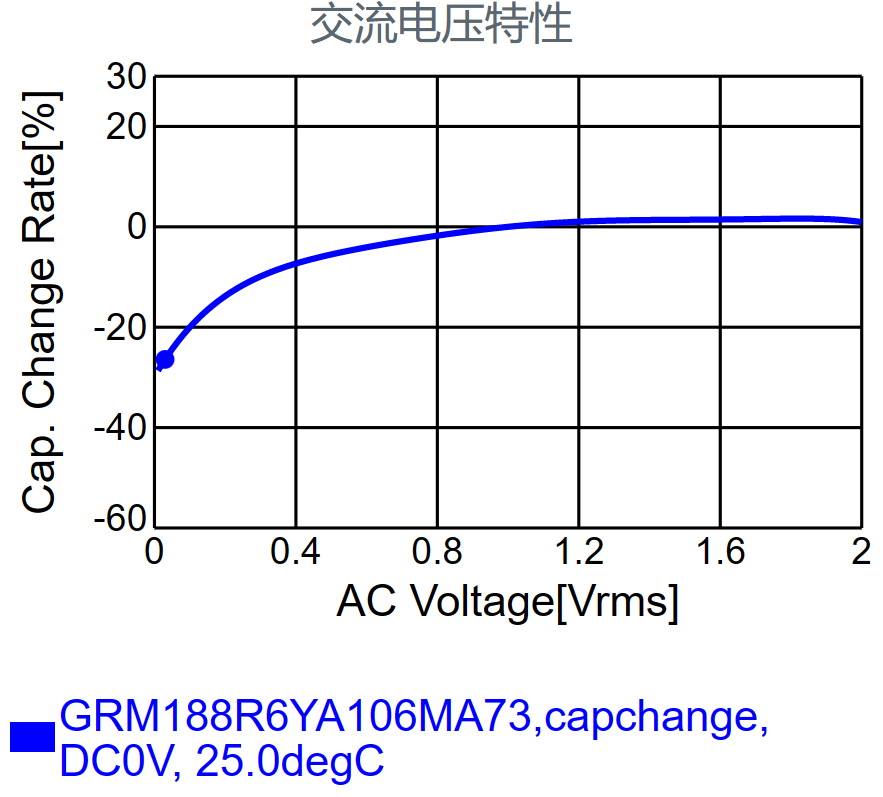

DCDC的输出纹波一般不会很大,我们取0.03V_{RMS},查阅容量与交流电压关系的曲线可知,此时需要降容约26%。

3.2.1.1.3-温度

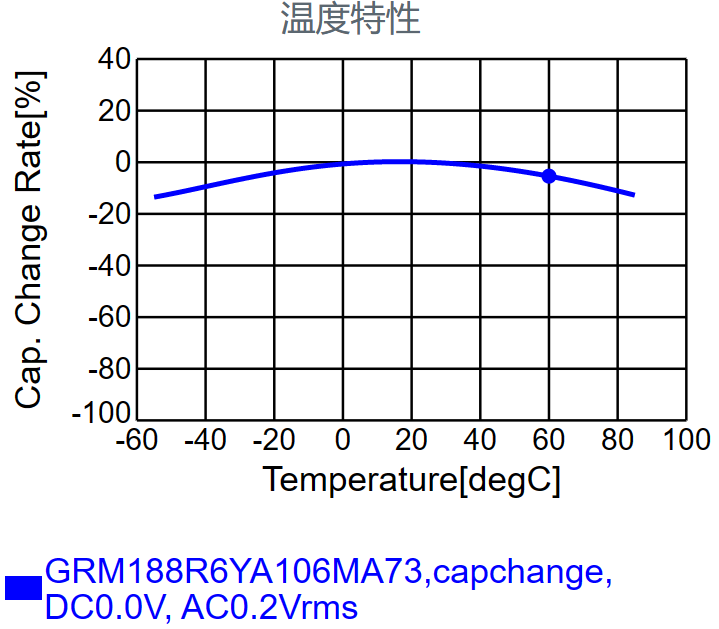

我们取其工作温度为60℃,查阅容量与温度关系的曲线可知,此时需要降容约5%。

3.2.1.1.4-老化

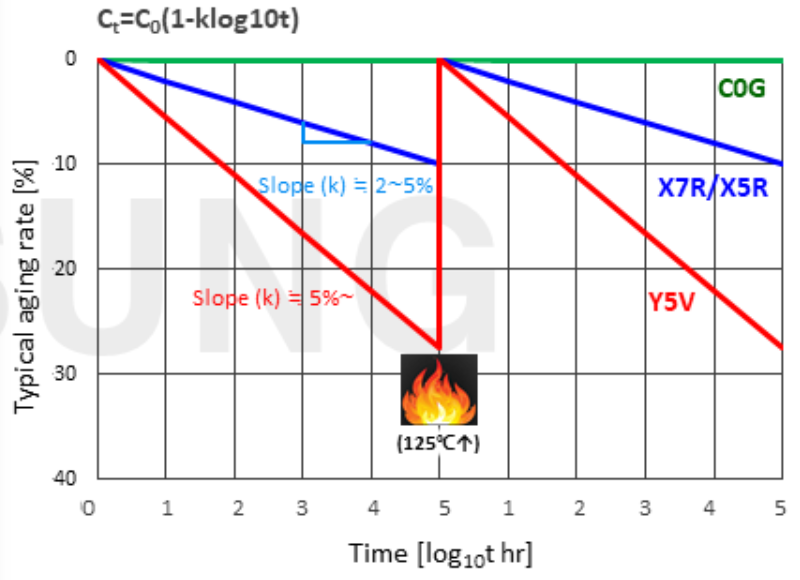

我们假设其工作了1000个小时,查阅容量与老化时间关系的曲线可知,此时需要降容约6%。

不过在购买MLCC时,不太需要关注MLCC的生产日期,因为在焊接过程中,MLCC的温度会上升到它的居里温度以上,即125℃以上,冷却后其容量即恢复。

3.2.1.1.5-有效容量计算结果

在以上的条件下,我们可以计算出,此静电容量为10uF的MLCC,其有效容量为:

10μF×(1-85\%)×(1-26\%)×(1-5\%)×(1-6\%)≈1μF

仅为实际的\frac{1}{10}。

若其直流偏置变为24V,则有效容量变为约500nF;我们预设的使用条件都在规定的范围内,甚至留了充足的裕量,容量却变成了标称的\frac{1}{20},很恐怖。

3.2.1.2-温度特性

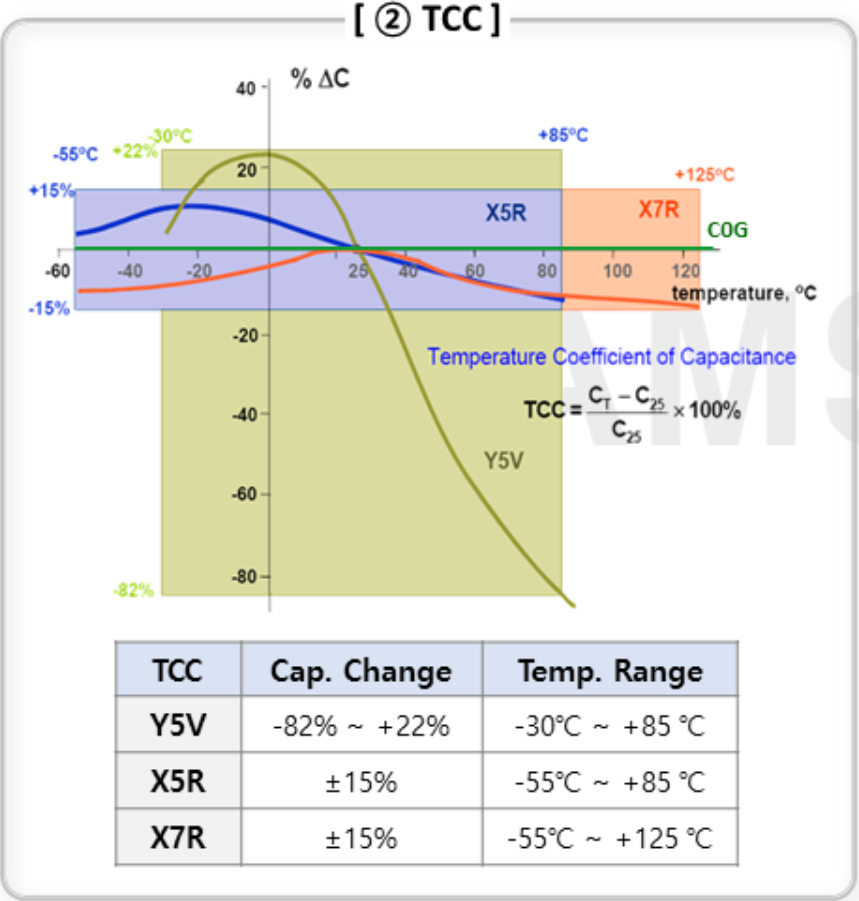

不同温度特性除了对有效容值有影响外,对适用温度范围也有影响,如下图所示。

如需在高温环境使用,建议换用钽电容。

3.2.1.3-特殊类型的MLCC

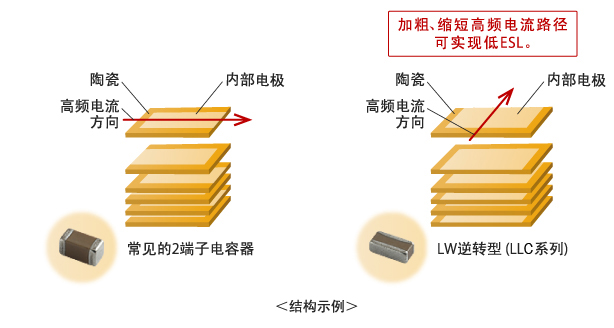

- 长宽逆转/LW逆转

长宽逆转的MLCC相较于普通MLCC拥有更小的ESL,高频表现更好。

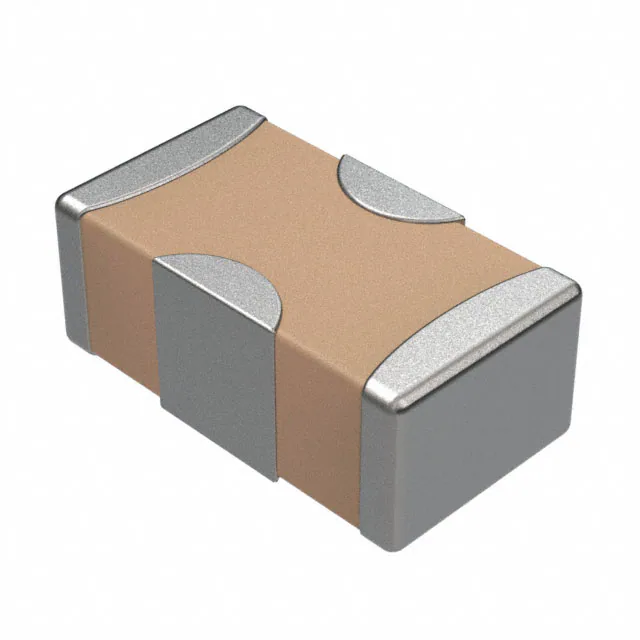

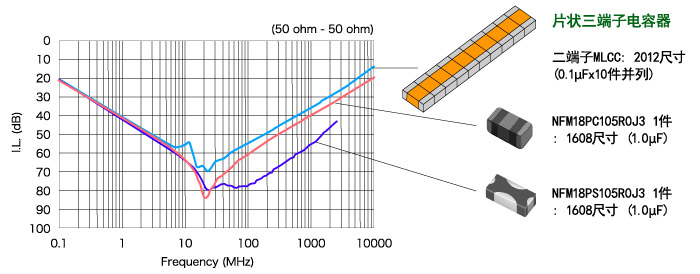

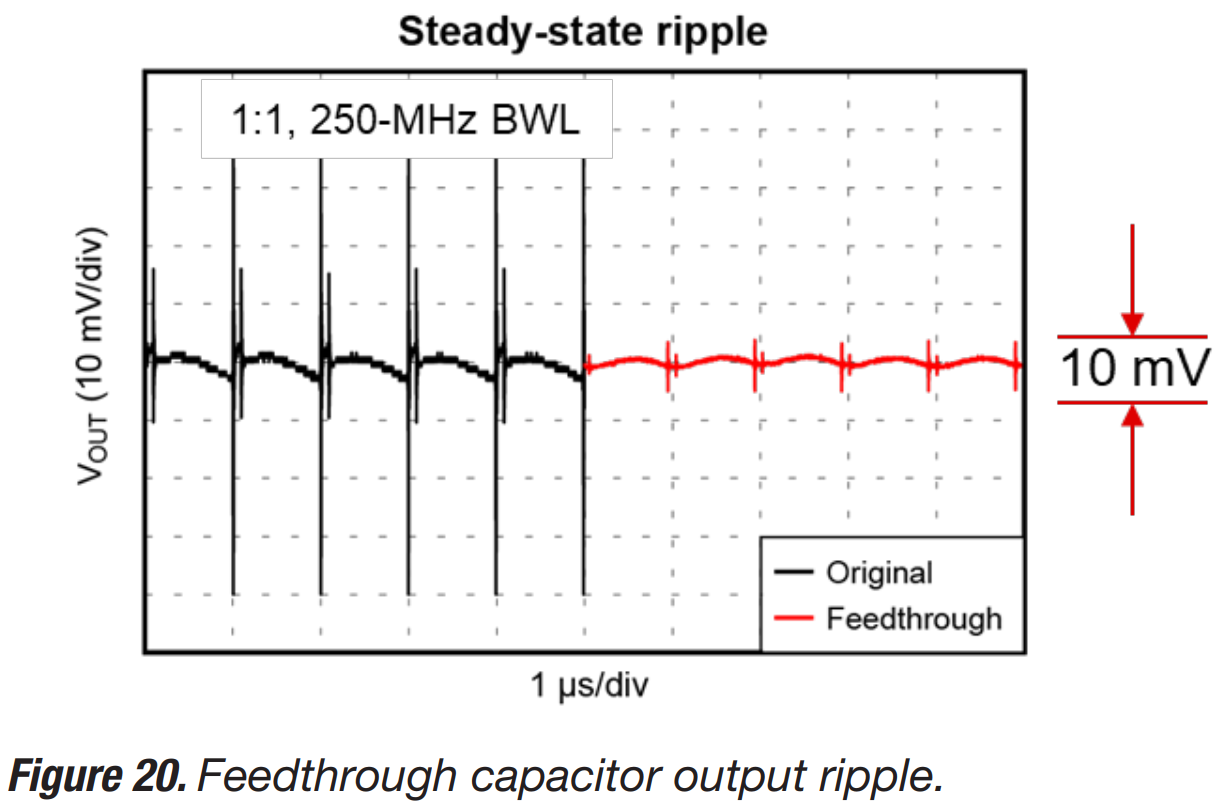

- 穿心电容/三端电容

穿心电容相比相同大小的普通MLCC的容值更小,耐压更低,但高频特性好得多(如下图),适合用于滤除高频杂波,如DCDC输出中的噪声尖峰。

穿心电容在滤除噪声尖峰时效果比普通电容好得多,如下图:

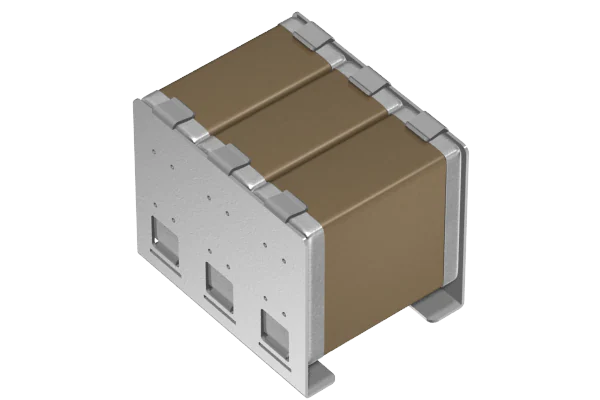

- 带引脚的MLCC

带引脚的MLCC可以在相同的板面积上提供给更大的容量,并且可以缓解机械应力,减缓啸叫。但是,成本很高。

3.2.1.4-虚标

MLCC是虚标的重灾区,强烈建议在各大代理商处(立创商城,Mouser,Digikey,华秋,云汉芯城等)购买,而非淘宝或闲鱼。

并且建议购买提供电容特性曲线数据厂家的产品,如muRata,TDK,三星等。

一般而言,虚标通常出现在额定电压,介质温度系数这两方面,静电容量虚标的反而不多。

MLCC的额定电压≠击穿电压,一般击穿电压为额定电压的2.5倍以上(曾经试过0805标称50V额定电压的MLCC加压到300V+都不会击穿),所以,如果一个商家将额定电压为25V的MLCC标称为50V额定电压,而你恰好在50V以内使用,那么这个电容大概率不会失效,但其有效容值衰减的厉害;这是你发现电路工作不正常,拆下来测这个电容没有击穿,并且容值也是对的,怎么看怎么都不像是这个电容的问题,会给调试电路带来很大的困扰。

温度系数虚标也很常见,比如Y5V或者Z5U标成X5R/X7R,X5R/X7R标成C0G/NP0。这个虚标更难测,需要测量不同温度下容值的变化。

总之,去大代理买,别去淘宝或闲鱼!!!个人基本没有辨别能力!!!出问题了都不知道问题在哪!!!

3.2.2-电解电容

电解电容的体积相对MLCC来说较大,相应的,容量与耐压通常也更大,并且没有直流偏置效应与压电效应等,对机械应力的耐受程度较高。但是其ESR,ESL相比MLCC通常更大,并且绝大多数电解电容都是有极性电容(极少无极铝电解电容会以NP标注),接反即爆炸。

按电解质来区分,可将电解电容分为铝电解电容,钽电解电容与铌电解电容,其中铌电解电容很少使用,这里不讨论,仅讨论前面两种。

3.2.2.1-铝电解电容

铝电解电容按其电解质的形态可分为液态铝电解电容(电解液)与固态铝电解电容(聚合物)两种。

3.2.2.1.1-液态铝电解电容

液态铝电解电容是最常见的电解电容,其成本低,尺寸多,容量大,耐压高,在很多场合都适用。

其缺点是高频性能不好,ESR,ESL较大;使用寿命有限,在高温下寿命尤其短,其老化表现为容量降低。

部分改善了高频性能的铝电解电容通常是绿色外皮,标注"Low ESL",性能相比普通的铝电解电容更好。

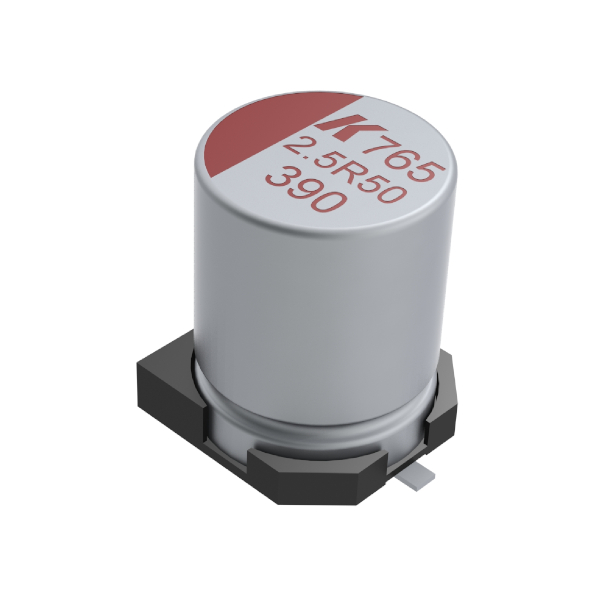

3.2.2.1.2-固态铝电解电容(聚合物电容)

相对于液态铝电解电容,固态铝电解电容通常有更低的ESR,ESL,更长的寿命,更好的高温性能,更低的耐压(通常50V以下)以及更高的价格。更好的高频特性让它在较高开关频率的DC-DC转换器输出滤波中也能有很好的表现,而不像普通铝电解电容一样更适合做AC-DC中的工频整流滤波。

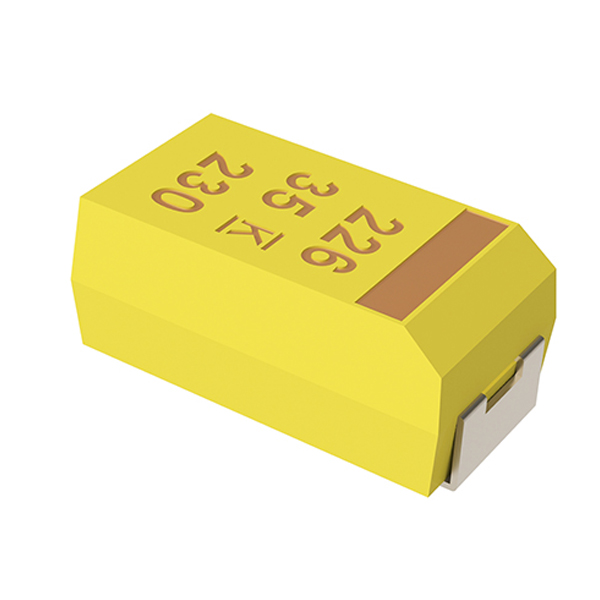

3.2.2.2-钽电解电容

钽电容相对更适合在高温环境下工作,虽然在高温环境下部分性能要降额,但相比于陶瓷电容125℃以上即失效,铝电解电容高温下寿命最多只有数千小时,钽电解电容仍然是高温环境下的首选。

钽电解电容两端的电压要严格小于其标称耐压,略微超压即冒火爆炸,使用时建议在常温下选用标称耐压为实际最大电压2倍以上,在高温下选用实际最大电压3倍以上的钽电容,来确保安全性。如用作5V电源轨滤波,考虑到板上其他器件的发热,选用一个耐压为16V的钽电容比较合适。下图为KEMET推荐的使用条件。

与常见的铝电解电容或二极管不同,钽电容通常在正极处做标识,注意不要接反。

此处仅讨论固态电解质的钽电解电容,液态钽电容常用于军工,仅少数HiFi佬用来做电子管的电源滤波,高频性能不好,价格非常昂贵且不好买,这里不讨论。

3.2.2.2.1-二氧化锰钽电容

这种类型的钽电容最为常见,一般外壳为黄色的钽电容都属于这类。

此类钽电容ESR较大,可达数欧姆,部分稳压器要求输出电容使用钽电容就是因为此ESR可帮助环路保持稳定。

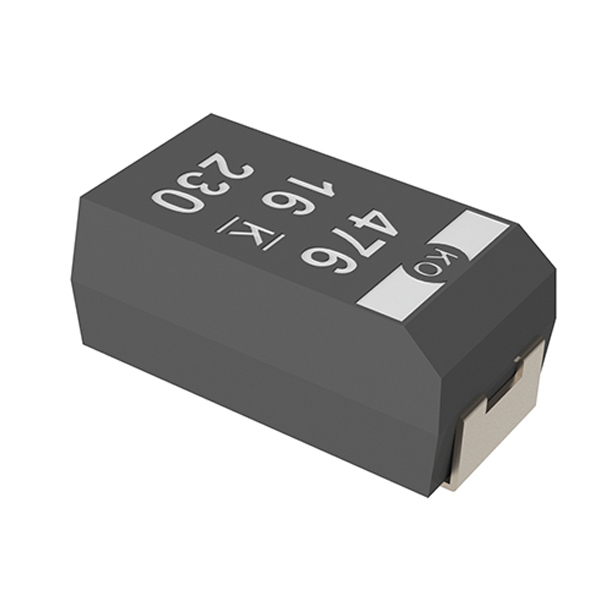

3.2.2.2.2-聚合物

聚合物钽电容一般为黑色外壳,与部分贴片固态铝电解电容很像,区别主要在正极标识上,聚合物钽电容一般以"+"标注正极。

聚合物钽电容相比于普通钽电容有着更低的ESR,ESL,这意味着更低的发热,更大的纹波电流与更好的高频性能,相应的,也会更贵一些,并且耐压一般不超过25V。

3.3-选择MOS(如有)

3.3.1-耐压

MOS的耐压一般表示为:V_{BRDSS}/V_{DS_{MAX}}/V_{DSS}/BV_{DSS}

此参数很易理解,是指MOSFET的源漏之间的最大电压(实际上,是体二极管的最大反向耐压),超过此电压可能导致MOSFET击穿。

Buck,Boost,Buck-Boost这三种拓扑中,MOSFET耐压应当大于max(V_{IN_{MAX}},V_{OUT_{MAX}});Inverting-Buck-Boost,SEPIC,Ćuk,ZETA这四种拓扑中需要大于V_{IN_{MAX}}+|V_{OUT_{MAX}}|。上下管的耐压要求相同。

如果让MOSFET长期工作在极限耐压附近,它的寿命会比较短;并且考虑到可能存在的过冲/振铃的问题,我们一般在此处会留一些余量,一般20%以上为宜。

3.3.2-导通电阻

MOS的导通电阻 (R_{DS(on)}) 对效率的影响很好理解,电流流经电阻就会发热,就会产生热耗散。MOS的导通电阻R_{DS(on)}是导通损耗的重要来源之一,越小的导通电阻R_{DS(on)}会使得导通损耗越小。但注意,由于导通电阻R_{DS(on)}与其他的参数例如栅极电荷Q_G有关,因此导通电阻R_{DS(on)}并不是越小越好,因为它可能会加大其他损耗例如开关损耗。

通常来讲,当耐压一定时,工艺相同时,导通电阻R_{DS(on)}与栅极电荷Q_G不可能同时很小,这是因为实际的MOSFET可以理解为由一个个小的MOSFET单元并联而成,而电容并联容值翻倍,电阻并联阻值减半,如果要低导通电阻R_{DS(on)},那么就需要很多个单元并联,这样就会导致栅极电容变大,栅极电荷也就变大了。在相同工艺,相同耐压下,相同导电沟道类型MOSFET的R_{DS(on)}×Q_G通常是一个常数,一般称之为品质因数FOM(注意区分与Q值品质因数的区别)。

3.3.3-栅极电荷

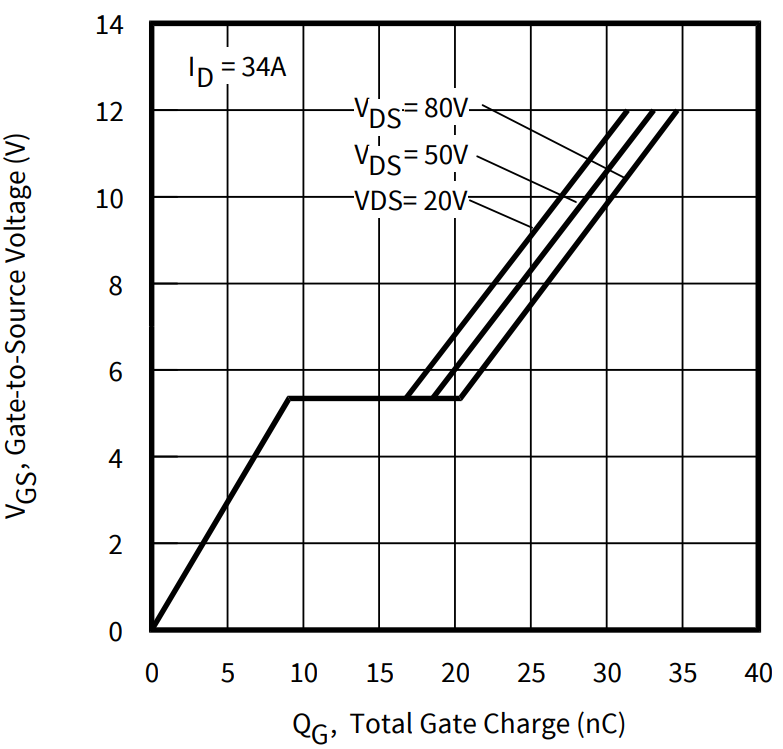

由于MOSFET的栅极类似于一个电容,而要让栅极的电压上升到足以开启MOSFET,需要给这个电容充电,为了衡量给此电容充电的难易程度,这里引入栅极电荷(Q_G)的概念。栅极电荷是指为开启MOSFET而注入到栅极的电荷量。栅极电荷越小,表明此MOSFET的栅极电容更好充电,也就是在由相同栅极驱动器驱动的条件下,这个MOSFET的开关越快,相应的,开关损耗就越小。

在输入输出条件,驱动情况和开关频率不变的情况下,Q_G越小,开关损耗越小。

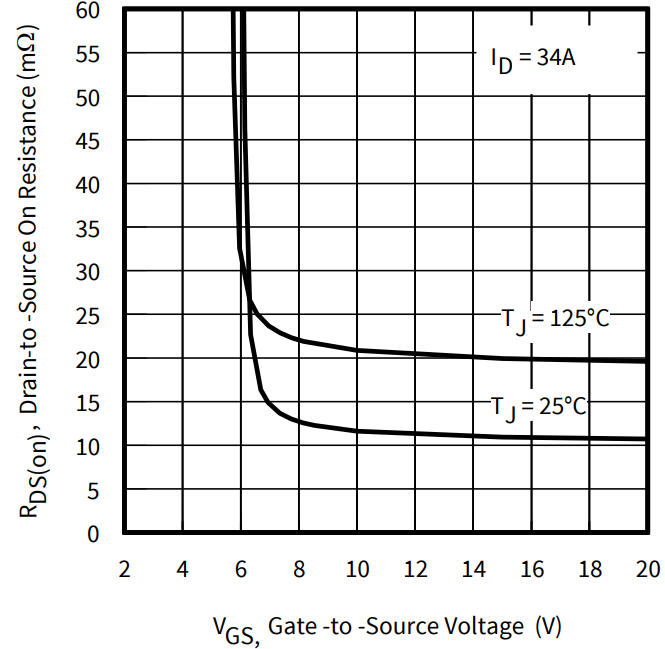

MOSFET的Q_G也与栅极电压有关,通常厂家会标注Q_G @ V_{GS}=?V,下图为Q_G与V_{GS}的关系:

实际上,用双脉冲测试来表征MOS的动态特性是更准确的,但凭Q_G也可大概估计MOS的动态性能。

3.3.4-阈值电压

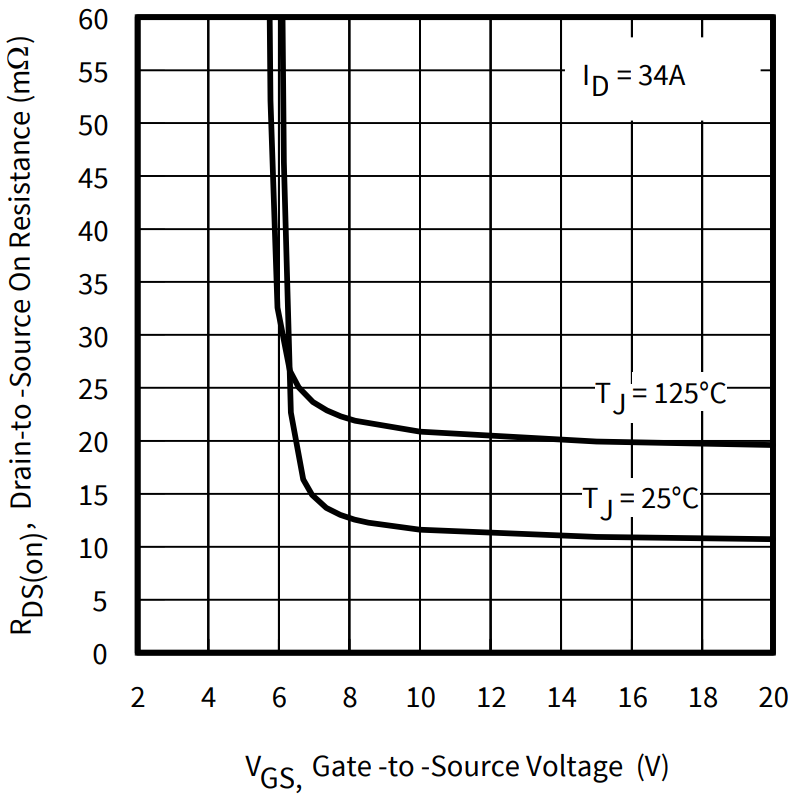

选用MOS时还要注意其阈值电压V_{TH}与栅极驱动器是否匹配,以英飞凌(IR)的IRF6644为例,其数据手册中R_{DS(on)}与V_{GS}的关系如下图。

此时如果我们用IRF6644搭配一个5V或以下的栅极驱动器使用,那么即使在导通阶段其R_{DS(on)}也会很大,基本不能走电流。

我们应当换用阈值电压V_{TH}更低的MOS,或者配合更高电压如12V的栅极驱动器使用。

3.4-选择二极管(如有)

DCDC中使用的二极管通常是肖特基二极管,因为其具有较小的正向压降V_F与较快的开关速度。

通常,出现在DCDC电路中的二极管分为续流二极管,自举二极管与减小死区损耗二极管三大类,我们分别介绍他们的选型。

3.4.1-续流二极管

在非同步整流中,通常我们需要一个肖特基二极管来充当一个续流开关,此二极管的平均整流电流I_{AVG}=I_{OUT},通常,我们所选取的肖特基二极管的最大平均整流电流应当为实际最大值的几倍,来确保其正向压降V_F在我们实际使用的电流大小上仍然是一个较低的值。这样可以使效率较高而发热较小。

在常见的拓扑中(例如Buck,Boost等),续流二极管两端的最大电压一般为开关节点的最大电压与最小电压之间的差值,也就是,续流二极管的耐压一般需要与功率MOS一致。

3.4.2-自举二极管

自举驱动的原理在下文的STEP 4中

自举二极管通常不需要走大电流,平均整流电流I_{AVG}仅相当于驱动上管所需的电流,即I_{AVG}=Q_G×F_{SW},通常最多为一两百毫安,因此,一个0402或0603大小的一般就够用了。

在常见的拓扑中(例如Buck,Boost等),自举二极管两端的最大电压一般也为开关节点的最大电压与最小电压之间的差值,也就是,自举二极管的耐压一般也需要与功率MOS一致。

3.4.3-减小死区损耗

部分设计中,会给下管并联一个肖特基二极管,并联这个肖特基二极管的目的是为了减小死区时间内的损耗,提升整体效率。

死区是指,在同步整流电路中,为了防止上下管在切换过程中同时导通形成电源到地的低阻通路,我们在上下管切换过程中会插入一段上下管同时关闭的时间,这个时间称为死区,如下图所示。

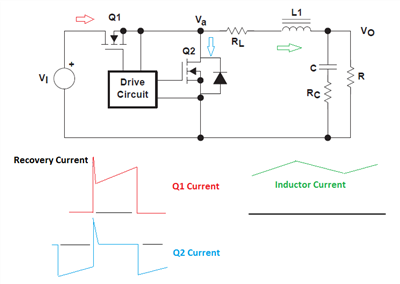

在没有给下管并联肖特基之前,在死区时间中,上管与下管均关闭,下管的体二极管先正向导通续流,待上管开启后再反向恢复。其中,损耗来源于体二极管的正向压降 V_F,与反向恢复的过程中的反向恢复电荷Q_{rr}。如下图所示。

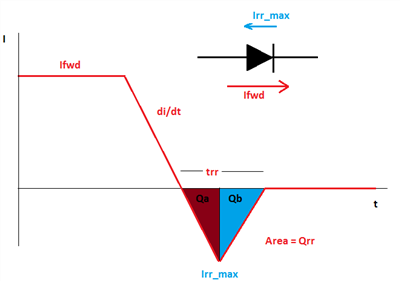

首先我们讨论反向恢复电荷Q_{rr}对死区损耗的影响。

上图为二极管在反向恢复时的时域波形,由此图,我们可以很容易得计算出反向恢复电荷Q_{rr}造成的损耗。

以TI的CSD18563Q5A为例,这是一个Q_{rr}=63nC的NMOS,假设将其用在36V输入的Buck的下管,开关频率为500kHz,那么,由Q_{rr}造成的损耗功率约为:36V×500kHz×63nC=1.134W,这是一个不小的功率。

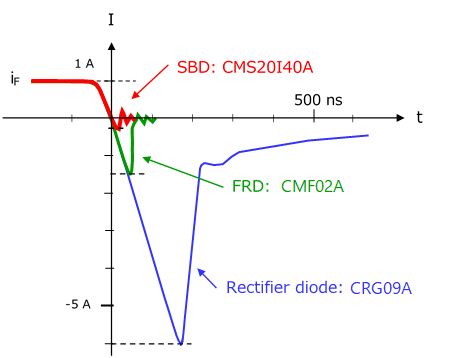

下图为SBD(肖特基二极管),FRD(快恢复二极管)与普通的整流二极管反向恢复的时域波形。

其中,只有肖特基二极管为单极性器件(金半接触),所以理论上来讲,它几乎没有反向恢复时间,这使得它相比体二极管这种普通的PN结双极性器件来讲,由Q_{rr}造成的损耗要小得多。在给MOS并联肖特基之后,MOS的体二极管可近似认为不会导通,这样,整体的Q_{rr}就会大幅度下降,效率就会提高。

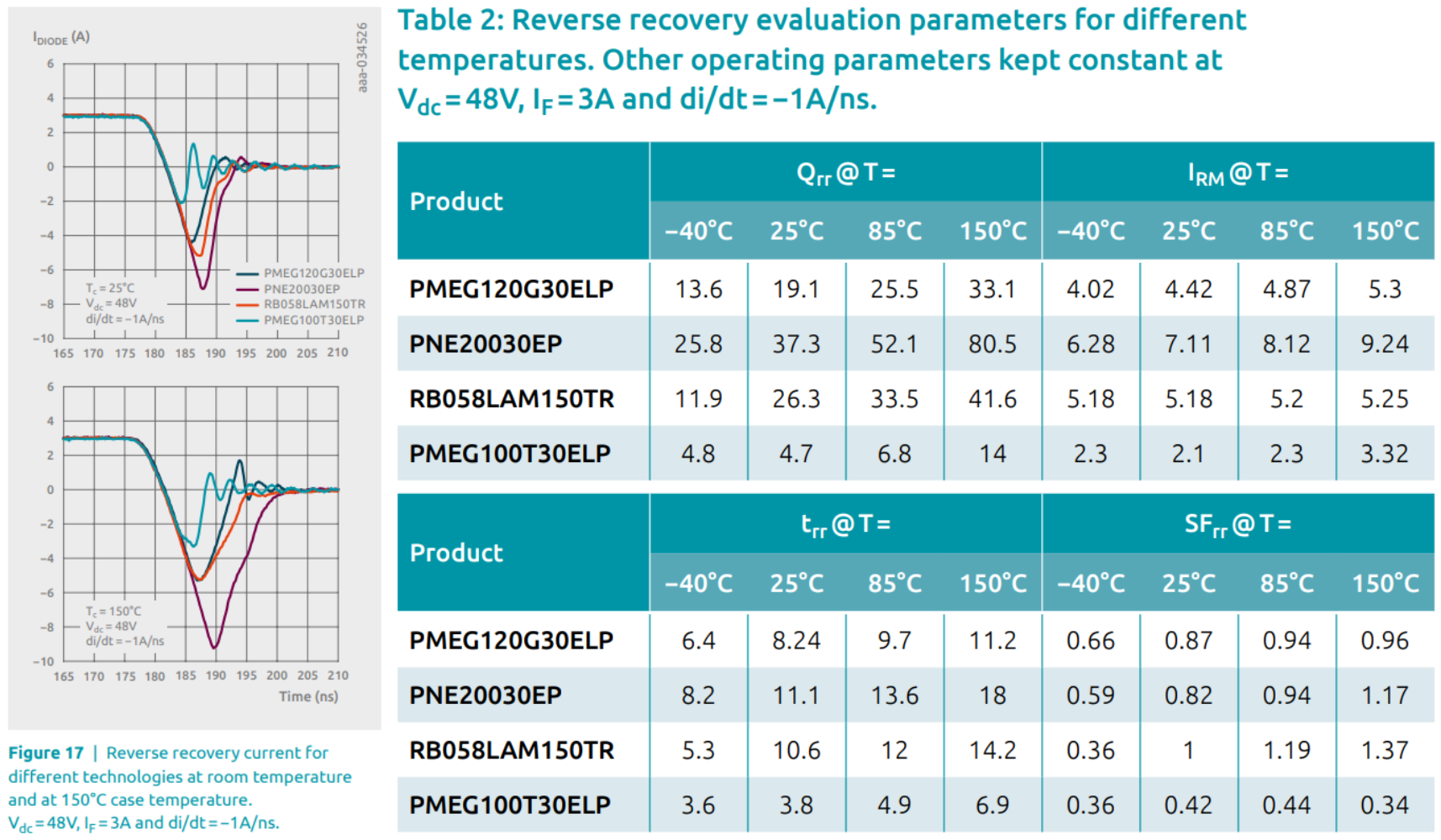

Q_{rr}的值与di/dt斜率,正向电流与温度都有关,在结温由25℃上升到150℃的过程中,Q_{rr}可能增加一倍甚至更多,进而带来更大的损耗。下图为部分二极管Q_{rr},T_{rr}与温度的关系:

其次我们讨论正向压降V_F对死区损耗的影响,这个很简单,死区时间×开关频率×电流×正向压降即可得到,普通硅管正向压降约为0.7V~0.8V,而肖特基则约为0.4V~0.5V,那么,正向压降V_F带来的损耗,在并联了肖特基之后,约会降低40%。

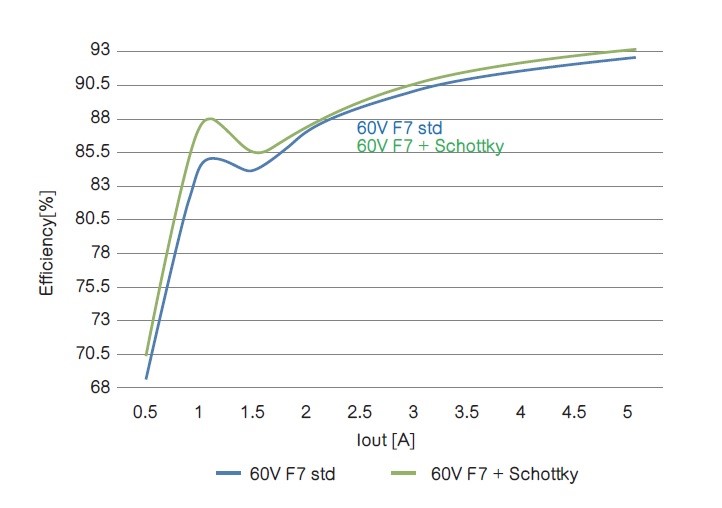

不过,并联这个二极管并不是必须的,因为添加合适的肖特基二极管后,只会提升约1%的效率,在需要小占板面积的解决方案,或是不太关心这一点点效率降低,完全可以不并联这个肖特基二极管。

上图为60W,250kHz,48V转12V同步整流降压转换器,下管并联肖特基前后的效率曲线对比。

这个二极管的耐压一般也需要与功率MOS一致。

但相比于平均正向整流电流,我们更关心这个二极管的可重复正向脉冲电流,其要大于功率管上流经的最大电流,并且最好留一些余量。

4-STEP 4: 配置外围容阻与连线

许多IC会提供各种各样的功能,这些功能一般需要外围容阻或连线进行配置;此外,我们也可以给电路加上一些额外的元件,来改善性能。

下文列举了一些常见的功能,括号内为常见引脚名,如果你选择的IC没有对应的功能可配置,跳过即可。

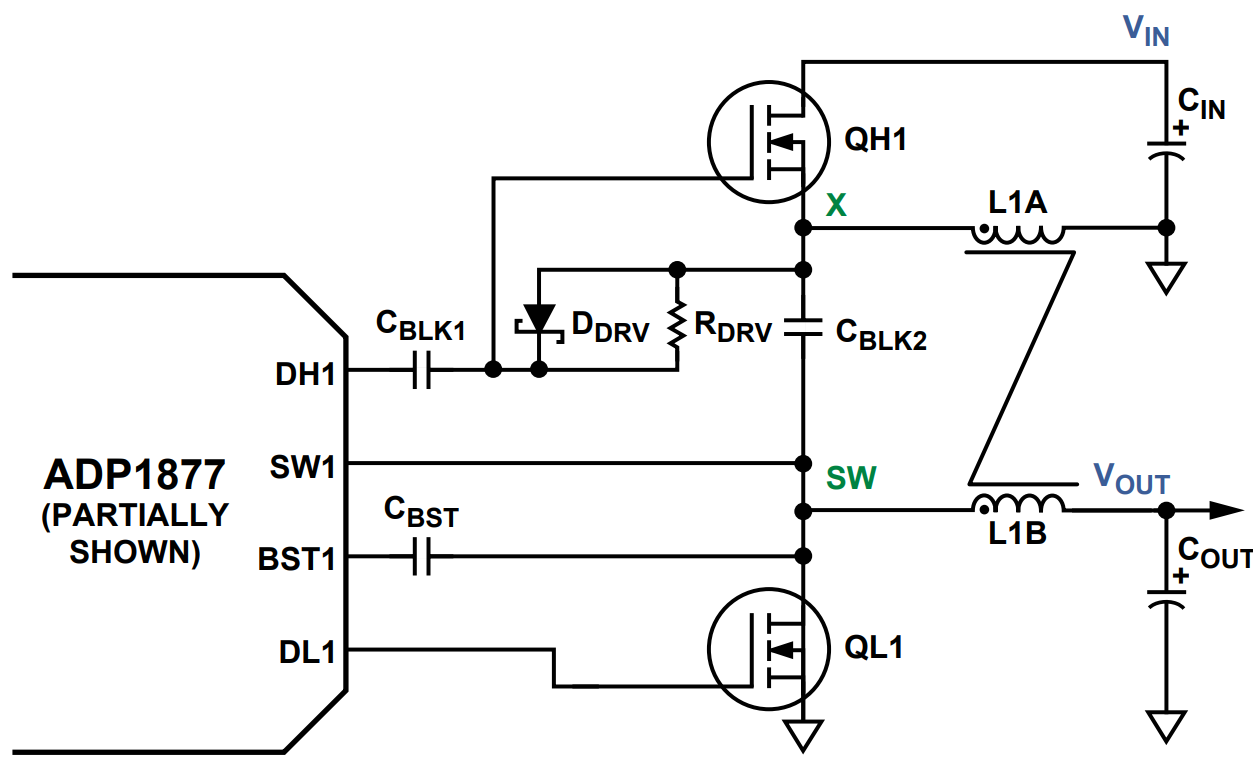

4.1-自举驱动(BOOT/BST/Bootstrap)

在常规的数字电路中,上管通常选用PFET而下管选用NFET,但在功率电路中一般不这样做,因为NFET的载流子为电子,PFET的载流子为空穴,这导致了μn>μp(一般μn约为μp的2~3倍),使得在相同工艺,相同晶片面积与相同|V_{GS}|的情况下,NFET的导通电阻RDS(ON)小于PFET,为了更高的效率以及更小的发热,在功率电路中通常上下管都采用NFET,虽然这样带来了驱动的问题,但是为了效率的提升,是值得的。

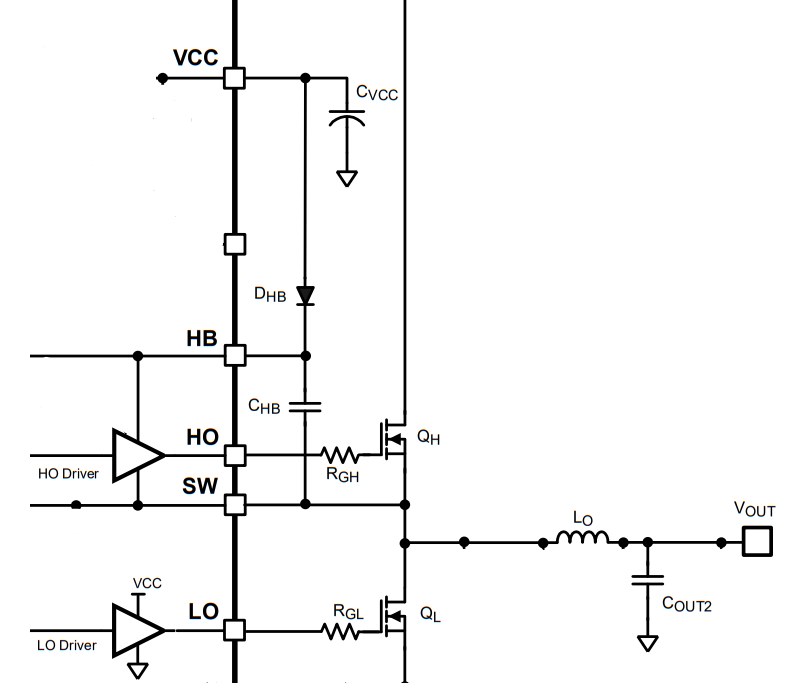

我们知道,NMOS的导通条件为VGS>VTH,而以Buck电路为例,在上管导通时,VS≈VIN,此时我们仍需要维持VGS>VTH以维持上管的导通,那么就要使VG>VIN,此处我们就需要一个二极管和电容组成的自举驱动电路来完成上管NMOS的驱动。

上管的驱动电路为"浮地",以SW节点为"地",在上管关断,下管导通时,VSW≈0V,此时内部的稳压器输出通过二极管DHB给自举电容CHB充电,VHB≈VCC;在下管关断,上管导通时,VSW≈VIN,由于电容两端电压不能突变,此时VH≈VCC+VIN,这样上管驱动器就有足够高的电压来驱动上管NMOS来使其维持导通。通常DHB采用肖特基二极管来减小正向压降VF,CHB的取值通常为100nF~1uF,具体参考手册推荐。

有些厂家也把自举电容和自举二极管叫做CBST与DBST,实际功能与前文所讲的相同,仅名称不同。

许多Buck IC集成了自举二极管,使用时仅需将一个电容连接在开关引脚(通常名为SW,PH或LX等)与自举驱动引脚(通常名为BST或BOOT等)之间即可。

有时厂家还建议在自举电容(C5)与自举引脚(BST)之间加入一个小电阻(R5),如上图所示,此电阻的作用是限制自举电容放电速度,使开关管的开关速度变缓,来削减高次谐波的能量,使开关尖峰与噪声更小,改善EMI。但这样会增大开关损耗,使效率略低一点。

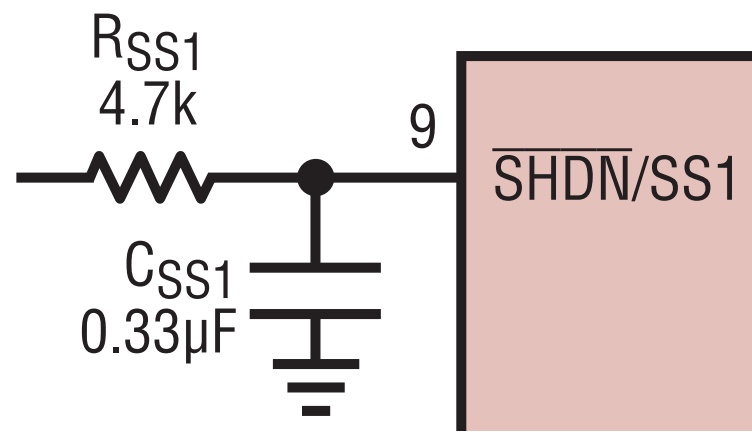

4.2-软启动(SS/Soft-Start)

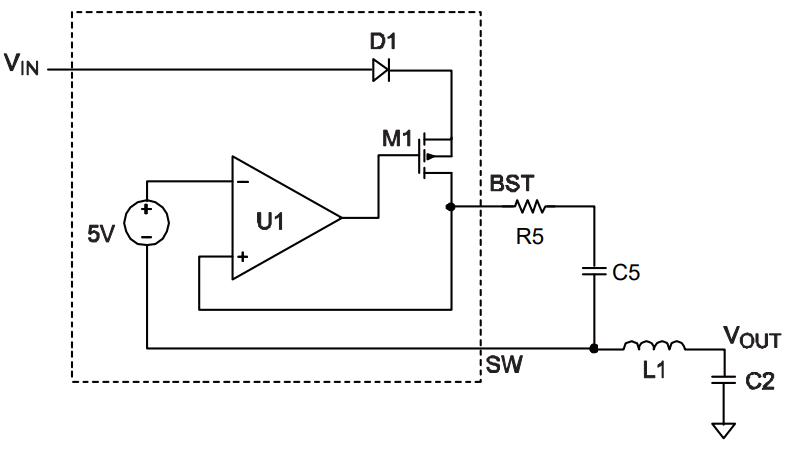

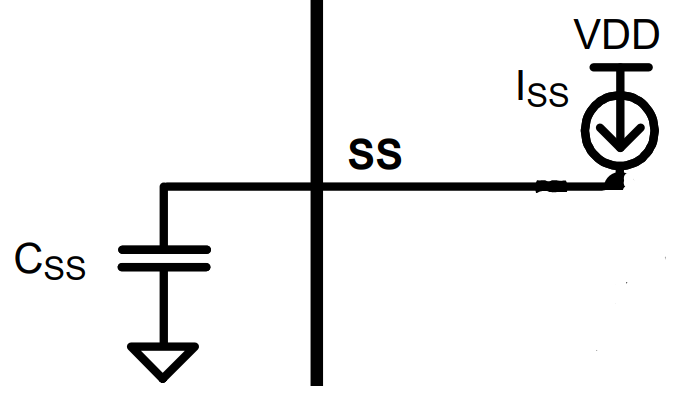

为了抑制上电时由输出电容充电引起的浪涌电流,或是对不同电源轨的上电时序有要求,有些IC提供SS功能,一般通过一个电容来设定软启动时间,而软启动的时间由这个电容的容值与为软启动电容充电的恒流源决定。下图为常见的软启动结构图:

软启动通过恒流源对电容进行充电,只要合理选择电容值(恒流源电流值一般为芯片内部固定值),就可以得到电容达到预设电压处的时间间隔,也就是软起动时间,输出电压就会按照预设的软起动时间从 0V 线性增大至稳定值。下图为不同软启动时间所对应的电压与电流的关系:

4.3-使能(EN/UVLO/RUN/ON/SHDN/OFF)

一般来讲,当使能引脚为高电平时,IC工作,为低电平时,IC关断。

4.3.1-默认使能

当我们不需要使能这个功能时,我们可以将其设置为默认使能。

TI,ADI这两家公司IC的使能引脚最大耐压一般等于输入端的最大耐压,可以直接将使能引脚与输入连在一起。

MPS的部分IC使能引脚耐压仅为5V,默认使能需要由上拉电阻将使能引脚上拉到输入,电阻阻值可根据最大输入电压V_{IN_{MAX}},使能引脚最大电压V_{IN_{MAX}},使能引脚最大电流I_{EN_{MAX}}计算:R_{PULLUP}>\frac{V_{IN_{MAX}}-V_{IN_{MAX}}}{I_{EN_{MAX}}}。其他厂家的IC也可根据此公式计算上拉电阻R_{PULLUP}。

4.3.2-EN用作欠压保护

我们也可以用电阻分压网络来连接使能引脚与输入,当输入电压低于某一值时,使能引脚的电压便会低于使能电压,IC关断。

此方法可以用作电池过放电保护等。

4.3.3-EN用作软启动

部分IC的使能引脚还兼任软启动功能,以LT3471为例,其软启动时间可由RC决定。

4.4-开关频率/同步(FREQ/SYNC)

部分IC提供开关频率调节的功能,这些IC都有一个频率调节引脚,通过改变连接在这个引脚与地(绝大多数)或输入(少数)之间的电阻来改变开关频率,数据手册中通常有计算公式,按照公式计算电阻阻值即可。

部分频率调节引脚还兼任同步功能,可以在此引脚上输入一个在其同步范围内的时钟信号,IC将会与此时钟信号同步。

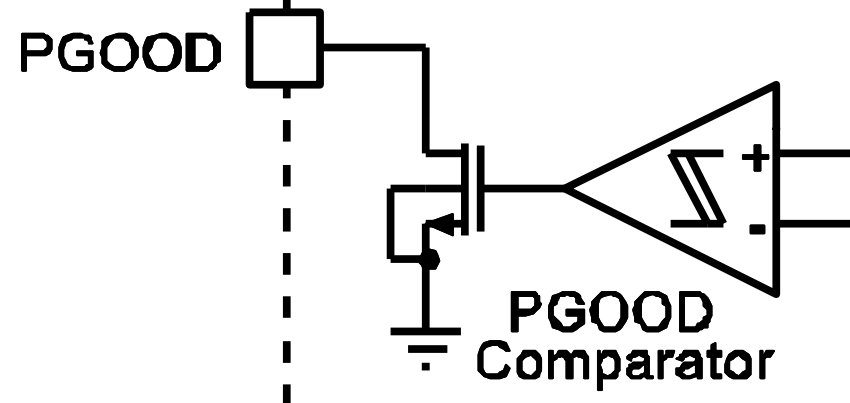

4.5-电源正常(PG/PGOOD)

部分IC提供电源正常指示,通常为检测输出电压是否在设定值附近很小的区间内,是则电源正常,否则电源异常;此引脚通常为开漏(OD/OC)输出,需要上拉电阻但可以多个输出直接并联,来实现线与逻辑。

4.6-轻载节能模式(AAM/LPM/CCM/DCM/BURST/MODE/PFM/ECO)

为了提升轻载效率,部分IC在输出电流很小时会进入节能的工作模式,开关频率大幅度下降,这样会将IC内部的功耗降低很多(主要是降低开关损耗,驱动损耗与静态电流),这在轻载时对提升效率有很大的帮助。但带来的问题是尽管输出电流较小,由于开关频率的大幅降低,输出纹波还是会增大许多。

通常,模式配置由将对应引脚连接到固定电平,或悬空完成。

以下我们讨论轻载下的各种工作模式:

4.6.1-强制PWM模式

在不关心轻载效率而关心轻载纹波时,或是需要Fly-Buck这种拓扑时,可以将IC配置为强制PWM模式(FPWM/FCCM),此时IC的开关频率固定,不会因轻载而下降,纹波也就不会因轻载而变大。

4.6.2-二极管仿真模式

同步整流IC工作在强制PWM模式且轻载时,电感上可能会出现反向的电流,将部分储存在输出电容中的能量泄放至地,造成能量的浪费,效率的降低。部分IC提供二极管仿真模式,在检测到MOSFET上出现反向的电流时,就强制关断此MOSFET,阻止能量的泄露。此时MOSFET的行为类似二极管,只能单向导电。将此模式称之为二极管仿真模式。

二极管仿真模式可以在不提升输出纹波的情况下降低轻载时的损耗,提升轻载效率。

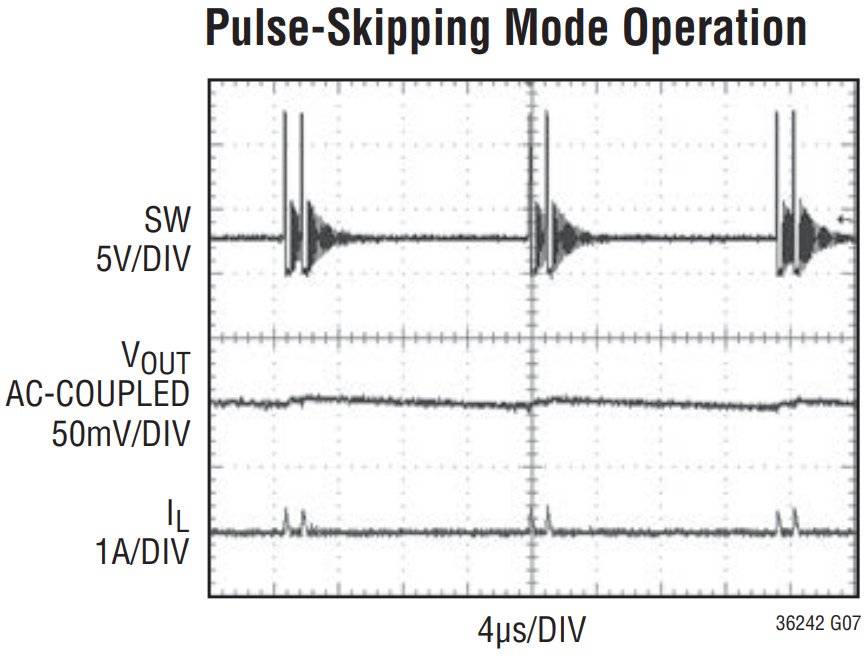

4.6.3-跳频模式

部分IC在轻载时会进入跳频模式(PSM),因为在DCM模式下,占空比会随着负载电流的减小而持续减小,而受最小导通时间的限制,占空比不能无限小。这里控制器会屏蔽掉一些脉冲,在相邻的几个开关周期内以原开关频率,较大的占空比工作,给输出电容充电储能;之后的几个周期内不工作,由输出电容维持电压,如下图所示:

跳频模式的优点是瞬态响应较好且纹波较小,但其轻载效率不如突发模式。

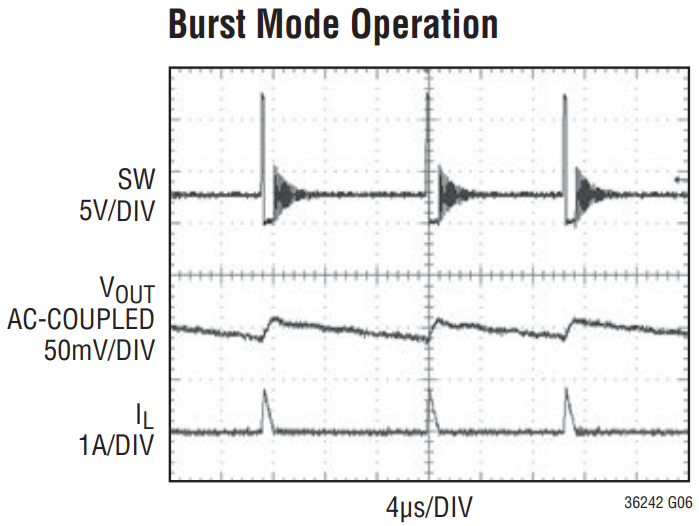

4.6.4-突发模式

突发模式(Burst/PFM)相比跳频模式,更加“平均”,直接采用降低开关频率的方式来节能。

突发模式的优点是效率高,但相比于跳频模式纹波较大且瞬态响应较慢。

MPS的AAM类似于突发模式,此处略去不讨论。

4.7-外部供电(EXTVCC/VCC/BIAS)

在部分高压输入的IC中,为了提升效率,会提供一个外部供电引脚。

以一个100V输入转5V输出的Buck芯片为例,在这个IC中,内部控制电路由一个输出4V的LDO供电,假设内部控制电路的静态电流为1mA,而输入电压为100V,那么在这个LDO上消耗的功率就为96mW;而如果我们将输出的5V连接到VCC引脚,给内部电路供电,那么内部的这个LDO上的功耗就会变成1mW,省下的95mW可以减小发热,提升效率。

而部分高压Buck转换器没有内置比较器与开关,而是采用了高压低压LDO串联的架构,如下图所示:

这样做的好处是可以实现更低的静态电流(高压LDO通常静态电流更大),但是这样就需要通过一个外部的二极管将Buck的输出电压连接到VCC引脚,防止在启动时高压LDO的电流全部流向负载,如下图所示:

在使用输出电压给芯片内部电路供电之后,轻载效率将会提升很多,如下图所示:

4.8-检流电阻

部分电流模式的控制器需要外部检流电阻 R_S 来实现电流感应,或实现限流。此电阻阻值一般为毫欧级。

在选取功率电阻时,要注意电阻上耗散的功率,及其额定功率在特定环境下的降额。

4.9-栅极驱动电阻

当栅极驱动器到MOSFET栅极的连线存在较大的寄生电感时,可能会在MOSFET的栅极产生振铃。我们可以在MOSFET的栅极与栅极驱动器之间加入一个电阻(称为栅极驱动电阻R_G),作为走线寄生电感与栅极寄生电容LC振荡的阻尼,来抑制振铃。

注意,栅极驱动电阻R_G不应过大,否则会较大降低MOSFET的开关速度,进而使开关损耗变大,效率变低。

实际设计中,可以在MOSFET栅极与栅极驱动器之间加入一个电阻的焊位,默认焊接0Ω电阻,如出现栅极振铃的现象,再逐渐增大阻值。

有时,还在电阻上并联一个二极管,来加速关断。

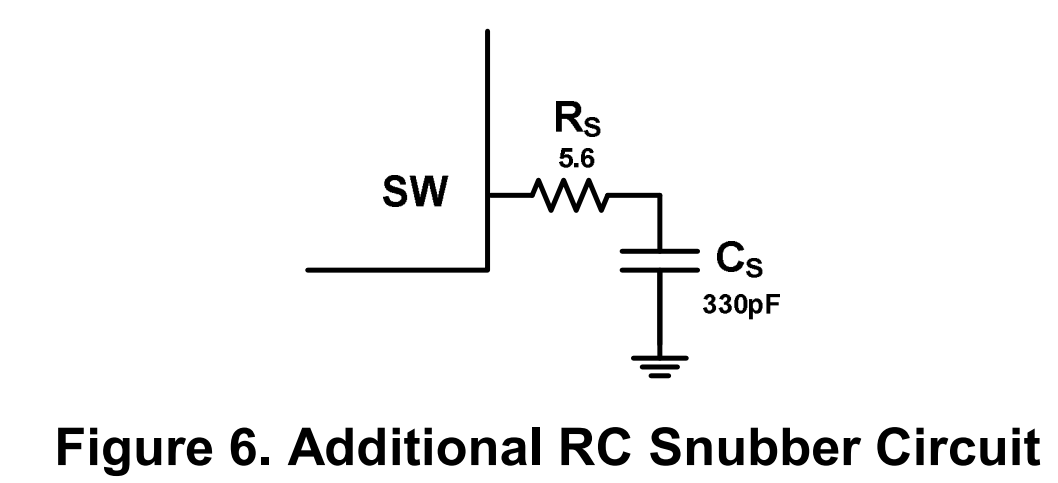

4.10-RC尖峰吸收

当开关节点SW上的振铃较为严重时,可以在SW节点处加上一个RC尖峰吸收电路来缓解,过大的C与过小的R会降低效率,通常R为欧姆量级,C为pF量级。

5-STEP 5: 验证器件热性能

5.1-哪些器件需要验证热性能?

有源的功率器件,例如MOSFET,肖特基二极管,或是内置了功率器件的芯片,都需要验证热性能。

无源器件通常注意不要超过额定电流值就一般不会出问题。

5.2-计算耗散功率

当我们选择完所有外围器件之后,我们就可以来计算整个系统的功耗了。

开关稳压器的耗散功率计算通常比较麻烦,涉及导通损耗,开关损耗和驱动损耗。其中开关损耗尤为难以计算。

这里建议使用各厂家的辅助设计软件,或是Spice/PLECS/Simplis仿真来获得各器件的耗散功率,将复杂的计算交给电脑。

下图为几种常见的封装通常所能承受的最大耗散功率。

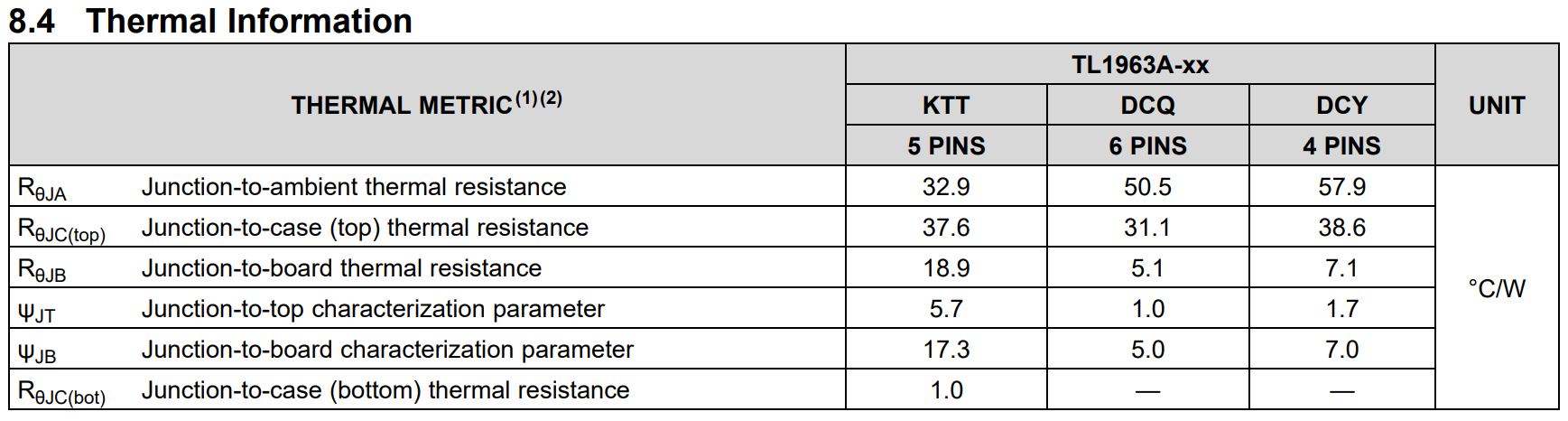

5.3-计算结温

在获知了耗散功率后,我们就可以根据数据手册中给出的热阻来大致估算结温了。

这里,我们以TL1963A为例,分别讲解各个名词的含义,再给出大致的估算方法。

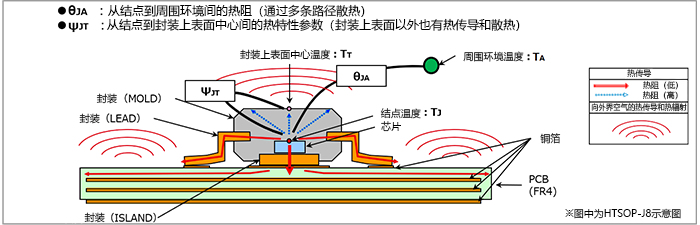

R_{θ_{JA}}:晶圆到环境的热阻,通常来是代表封装散热能力最重要的值。

R_{θ_{JC(TOP)}}:晶圆到封装顶部的热阻,在芯片封装顶部加散热片时需要注意这个值。

R_{θ_{JC(BOT)}}:晶圆到封装底部的热阻,通常有散热焊盘的封装会标出这个值,在使用散热焊盘散热时需要注意这个值。

R_{θ_{JB}}:晶圆到PCB板的热阻,在通过PCB散热的设计中需要注意这个值。

Ψ_{JT}:晶圆到封装顶部特性参数

Ψ_{JB}:晶圆到PCB板特性参数

其中,其他的厂家可能会将热阻中的"R"省略,例如,ADI常将R_{θ_{JA}}缩写为θ_{JA}。

R/θ与Ψ的区别是,R为实际的热阻,而Ψ并不是真正的热阻,它是在考虑了所有热量传递途径之后测得的值;R则是仅考虑单一方向热量传递的值。在实际的电子系统散热时,热会由封装的上下甚至周围传出,而不一定会由单一方向传递, 因此Ψ之定义比较符合实际系统的量测状况。

通常,我们最关心晶圆到环境的热阻R_{θ_{JA}},这个参数的单位是℃/W,如40℃/W,代表这个芯片上每有1W的功耗,这个芯片的晶圆会相对环境温度上升40℃。

不过,我们要格外注意热阻的测试条件,大部分厂家会在手册中给出热阻的测试条件,例如某个QFN封装的R_{θ_{JA}}是在1.6mm厚的FR4板上,通过9个内径0.3mm的热过孔连接到板背面,并且背面有20mm²的裸露铜,在无空气流动的情况下测得。

我们需要根据我们实际的情况,来进行一些修正,例如,假如我们给一个TO-263的功率器件,将其底部的散热焊盘直接焊接到一个巨大的带风扇的纯铜散热片上,那么我们就大可以用R_{θ_{JC(BOT)}}加一点当作实际的热阻。

那么,我们知道了功率耗散以及热阻之后,应当如何计算结温?

结温计算公式:T_{Junction}=T_{Ambient}+R_{θ_{JA}}×P_{Dissipation}

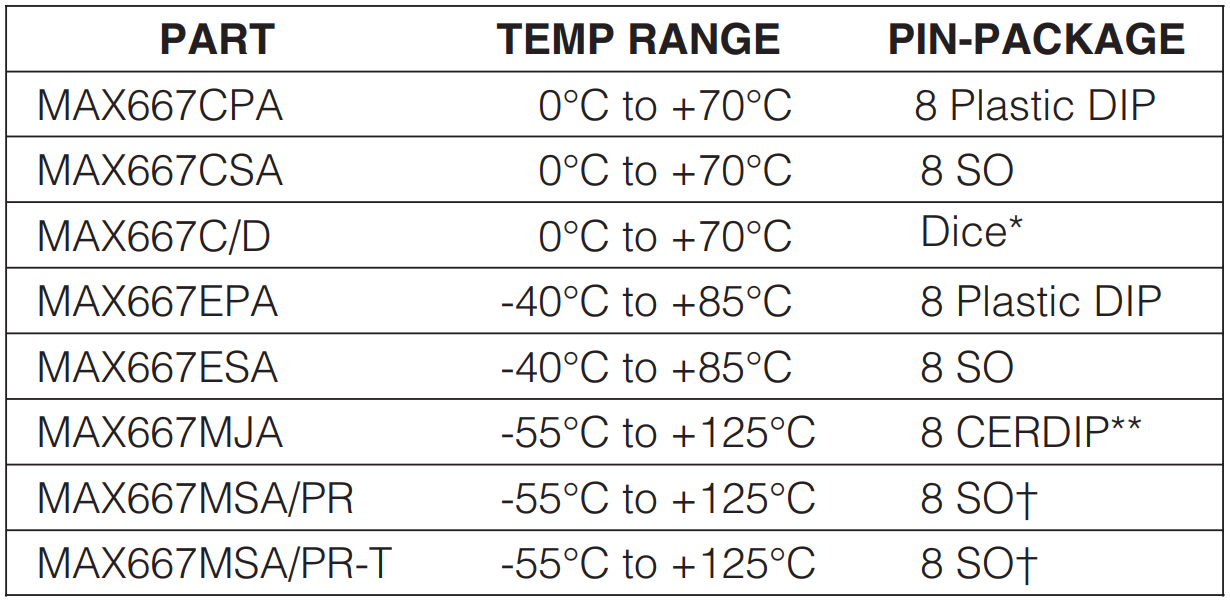

那么,芯片最大的结温是多少呢?

下图为MAX667不同温度等级的结温范围:

通常,电子元器件的温度范围分为以下几种:

商用级: 0℃ ~ +70℃ 常用字母代码:C

拓展商用级: 0℃ ~ +85℃ 常用字母代码:U

工业级: -20℃ ~ +85℃ 常用字母代码:I

拓展工业级: -40℃ ~ +85℃ 常用字母代码:E

车规AEC-Q100 2级: -40℃ ~ +105℃ 常用字母代码:G

车规AEC-Q100 1级: -40℃ ~ +125℃ 常用字母代码:A

车规AEC-Q100 0级: -40℃ ~ +150℃ 常用字母代码:T

军用级: -55℃ ~ +150℃ 常用字母代码:M

极端级: -55℃ ~ +175℃/+210℃ 常用字母代码:H

注意,宇航级仅指是否抗辐照,其温度范围与军用级类似。

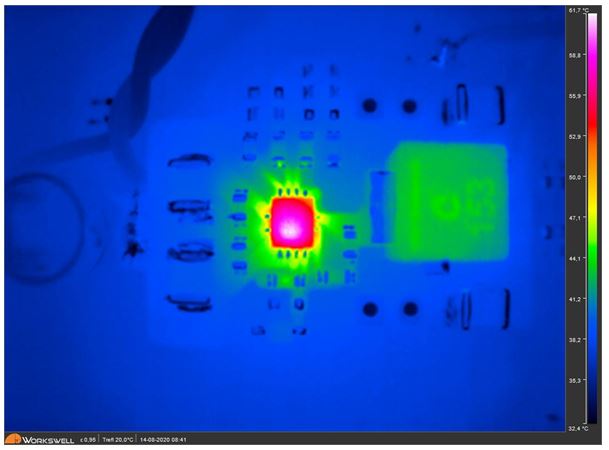

5.4-如何测量芯片结温?

5.4.1-间接测量

我们可以利用热阻来间接计算IC的结温。

在芯片封装的表面用导热胶固定一个小型温度传感器(如小型 4 线PT1000),或将一个小型热电偶焊接在芯片附近(建议焊在GND或V_{IN}上),如下图所示:

或者,直接用热成像仪观测IC表面的温度,如下图所示:

在测得温度之后,我们就可以利用数据手册中提供的芯片的热阻值(通常用Ψ_{JT}),间接计算出结温了。

5.4.2-直接测量

通常的IC并不会内置专门的温度传感器,这时如果我们要直接测量芯片的结温,可以借助二极管在正向电流一定的情况下正向压降V_F与温度的关系来得到芯片结温。

5.4.2.1-用哪里的二极管?

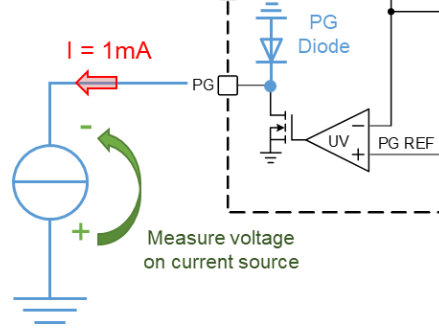

- OD输出的PG下拉NMOS的体二极管

如果我们选用的芯片有PG输出的话,我们可以借助这个PG输出下拉NMOS的体二极管来测试。

- ESD保护二极管

如果我们选用的芯片没有PG输出的话,我们还可以借助ESD保护二极管来测试。

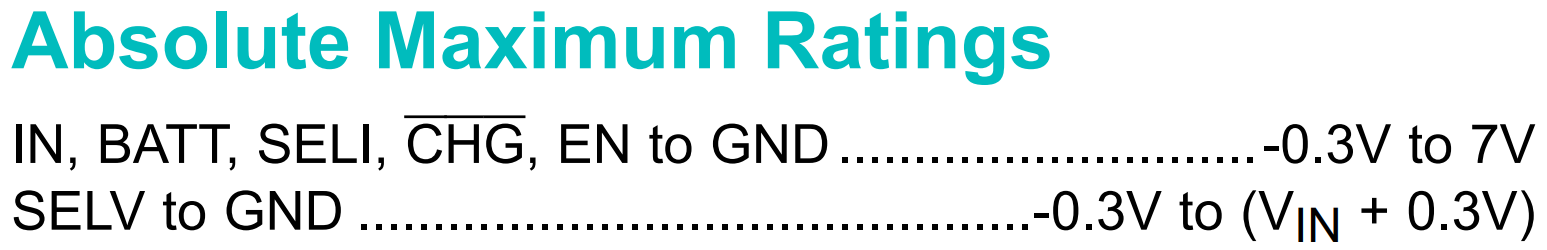

以MAX1811为例,我们可以观察Absolute Maximum Ratings里面包含"0.3V"的项,如下图所示:

那么,我们可以根据这个0.3V,很容易地推断出它内部的ESD二极管分布,如下图所示:

这时,我们就可以选择一个能够在IC处于工作状态的情况下被正向偏置的内部ESD二极管,用它来测量温度。

5.5-测量前的准备步骤

1.断开所选二极管引脚上任何其他的连接。

2.在IC封装上固定一个小型温度传感器。

3.将带二极管正向压降测试功能的万用表接在所选二极管引脚上。

4.放入温度试验箱中,等待读数稳定。

5.短时启动器件,读数后关闭器件。

6.重复上述步骤,测量在相同正向电流下,多个不同温度时的正向压降。

7.拟合曲线。

完成准备步骤之后,就可以将测得数据带入拟合过的曲线中,来得到对应的结温了。

6-STEP 6: 验证环路稳定性

我们在验证环路稳定性时,需要将不同控制类型的IC分开考虑。

6.1-迟滞控制(Hysteretic/COT/ACOT/D-CAP/DCS)

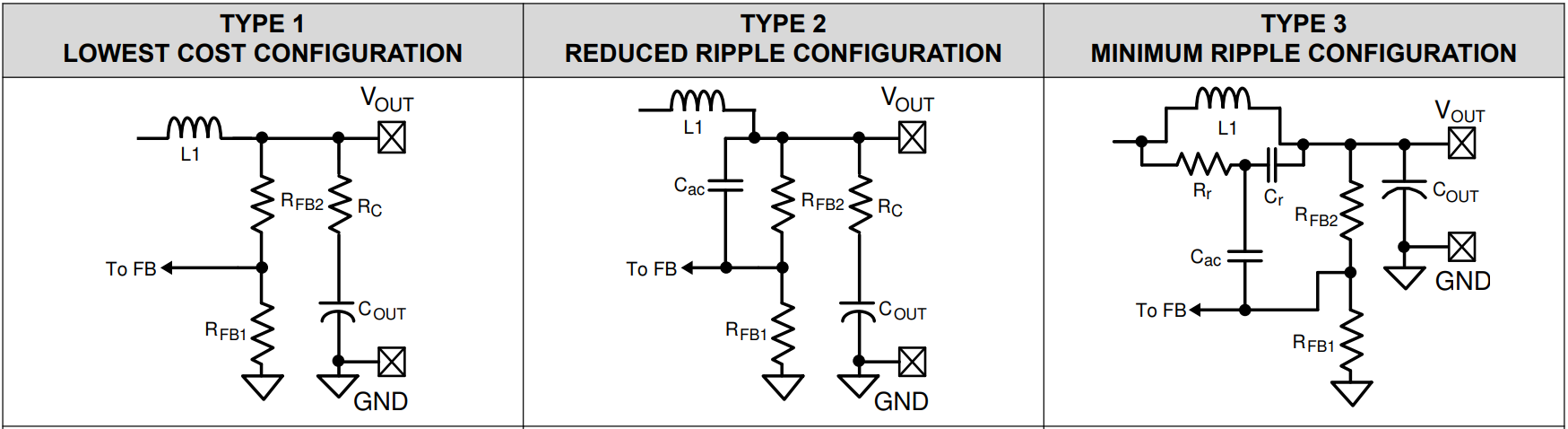

通常,迟滞控制的反馈有三种配置方式,分别如下图所示:

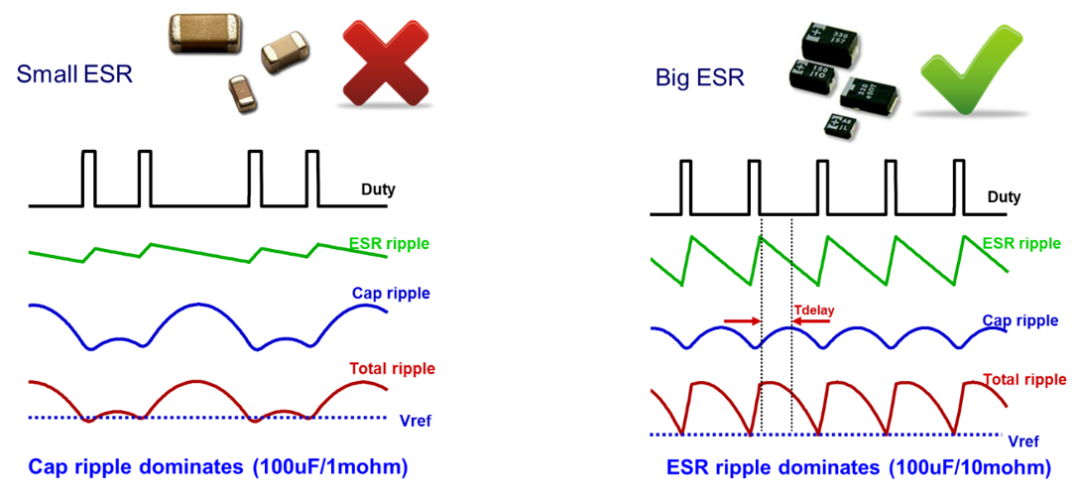

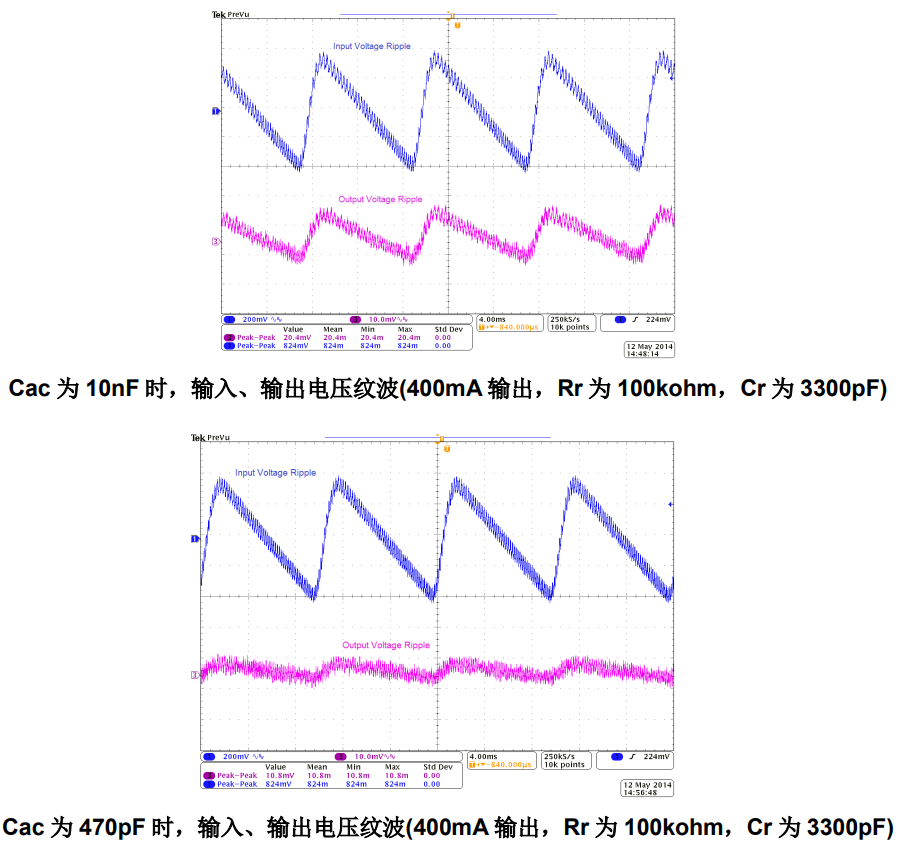

TYPE 1 利用输出电容C_{OUT}的ESR产生纹波,并在反馈电阻分压衰减后送入FB。

TYPE 2 同样利用输出电容的ESR产生纹波,但在顶部反馈电阻R_{FB2}上并联了一个前馈电容C_{ac},让交流分量几乎无损失地穿过电容到达FB。

TYPE 3 则利用R_r与C_r,借助SW处的方波来产生纹波,并通过C_{ac}隔离掉直流分量后送入FB。

三种方法中,只推荐使用后两种,其中第三种更推荐,因为它可以让输出纹波接近于0。

6.2-三种方式的环路稳定性判据

6.2.1-TYPE 1 环路稳定性判据

6.2.1.1-判定条件①

R_C≥\frac{V_{Ripple_{min}}×V_{OUT}}{V_{FB}×ΔI_L}

其中,V_{Ripple_{min}}为芯片要求的FB引脚的最小纹波电压,会在数据手册中给出,较新的芯片的典型值为20mV或25mV; ΔI_L为电感电流纹波,可通过ΔI_L=\frac{V_{OUT}×(V_{IN}-V_{OUT})}{V_{IN}×L×F_{SW}}来求出。

这个式子很好理解,电感纹波电流ΔI_L在输出电容C_{OUT}的等效串联电阻R_C上产生的电压纹波,在经过反馈电阻按\frac{V_{OUT}}{V_{FB}}的比例衰减送入FB后,仍然要大于芯片需要的最小FB纹波电压V_{Ripple_{min}}。

6.2.1.2-判定条件②

C_{OUT}≥\frac{V_{OUT}}{2×V_{IN}×F_{SW}×R_C}

这个式子的意思是,要求输出电压纹波中,由电容充放电引起的纹波占比要够小,由电感纹波电流流过电容的等效串联电阻R_C而产生的纹波要占主导地位。

因为I=C\frac{du}{dt},所以由电容充放电产生的纹波相对纹波电流会具有90度的相位差,而90度的相移会导致相位裕度的下降,进而很可能会导致次谐波振荡,所以,电容充放电引起的纹波占比要够小,这就要求电容容值要足够大。

6.2.1.3-判定条件③

R_C×C_{OUT}>\frac{T_{ON}}{2}

推导环路稳定性过程中用到了Pade Approximation,即e^{-sT_{sw}}=1-\frac{sT_{sw}}{1+\frac{sT_{sw}}{2}+\frac{T^2_{sw}}{π^2}},这是数学上的一个近似,在\frac{1}{2}F_{SW}之前是有效的,它服从采样定理。这里可以将系统对Ripple与基准电压进行比较时,每次翻转理解成一次采样,这样,我们需要采样频率大于二倍所需采集信号的最大频率,即得到上式。

6.2.2-TYPE 2 环路稳定性判据

6.2.2.1-判定条件①

R_C≥\frac{V_{Ripple_{min}}}{ΔI_L}

此处类似TYPE 1 ,只不过前馈电容C_{ac}的存在使得交流信号不用经电阻分压衰减,直接通过电容进入FB。我们此处假设C_{ac}很大,对交流分量近似短路,那么要求由ESR引起的输出电压纹波大于芯片要求的FB纹波最小值即可。

6.2.2.2-判定条件②

C_{OUT}≥\frac{V_{OUT}}{2×V_{IN}×F_{SW}×R_C}

此处同TYPE 1 ,略过。

6.2.2.3-判定条件③

C_{ac}≥\frac{1}{2×π×F_{SW}×(\frac{R_{FB1}×R_{FB2}}{R_{FB1}+R_{FB2}}))}

这个式子可以从时域或频域两个角度来理解:

从时域看,C_{ac}在F_{SW}处的阻抗要小于两个反馈电阻R_{FB1}和R_{FB2}在经过等效变换之后的源阻抗,以确保交流信号可以通过电容这个低阻路径,较小衰减地到达FB。

从频域看,C_{ac}与反馈电阻R_{FB1}和R_{FB2}在经过等效变换之后的源阻抗所形成的零点,要在开关频率之前,此时整个网络对交流信的增益接近0dB,交流信号可较小衰减地到达FB。

此判定条件为判定条件①中假设成立的判定条件。

6.2.2.4-判定条件④

R_C×C_{OUT}>\frac{T_{ON}}{2}

此处同TYPE 1 的判定条件③,略过。

6.2.3-TYPE 3 环路稳定性判据

6.2.3.1-判定条件①

C_{ac}≥\frac{1}{2×π×F_{SW}×(\frac{R_{FB1}×R_{FB2}}{R_{FB1}+R_{FB2}}))}

此处同TYPE 2 的判定条件③,略过。

6.2.3.2-判定条件②

C_{r}≥\frac{10}{F_{SW}×(\frac{R_{FB1}×R_{FB2}}{R_{FB1}+R_{FB2}}))}>C_{ac}

此式的意义是,要让C_r在F_{SW}处的阻抗要足够小,让流经R_r上的电荷大多流经C_r,这样我们在判定条件③中的纹波计算方式才比较符合实际。

6.2.3.3-判定条件③

R_r×C_r≤\frac{(V_{IN}-V_{OUT})×\frac{V_{OUT}}{F_{SW}×V_{IN}}}{V_{Ripple_{min}}}

此式的意义是,要让R_r与C_r产生的纹波,大于等于芯片要求的FB处的纹波最小值。

FB节点处被注入的纹波V_{Ripple_{p-p}}=\frac{(V_{IN}-V_{OUT})×T_{ON}}{R_r×C_r},按照此式反推即可获得本判定条件。

注意我们此处要考虑最坏情况,在输入电压最小时进行计算。

6.2.3.4-判定条件④

\frac{L_1×C_{OUT}}{R_r×C_r}>\frac{T_{ON}}{2}

此处类似TYPE 1 的判定条件③,略过。

6.2.3.5-判定条件⑤

C_{ac}≥\frac{T_{Settle}}{3×R_{FB2}}

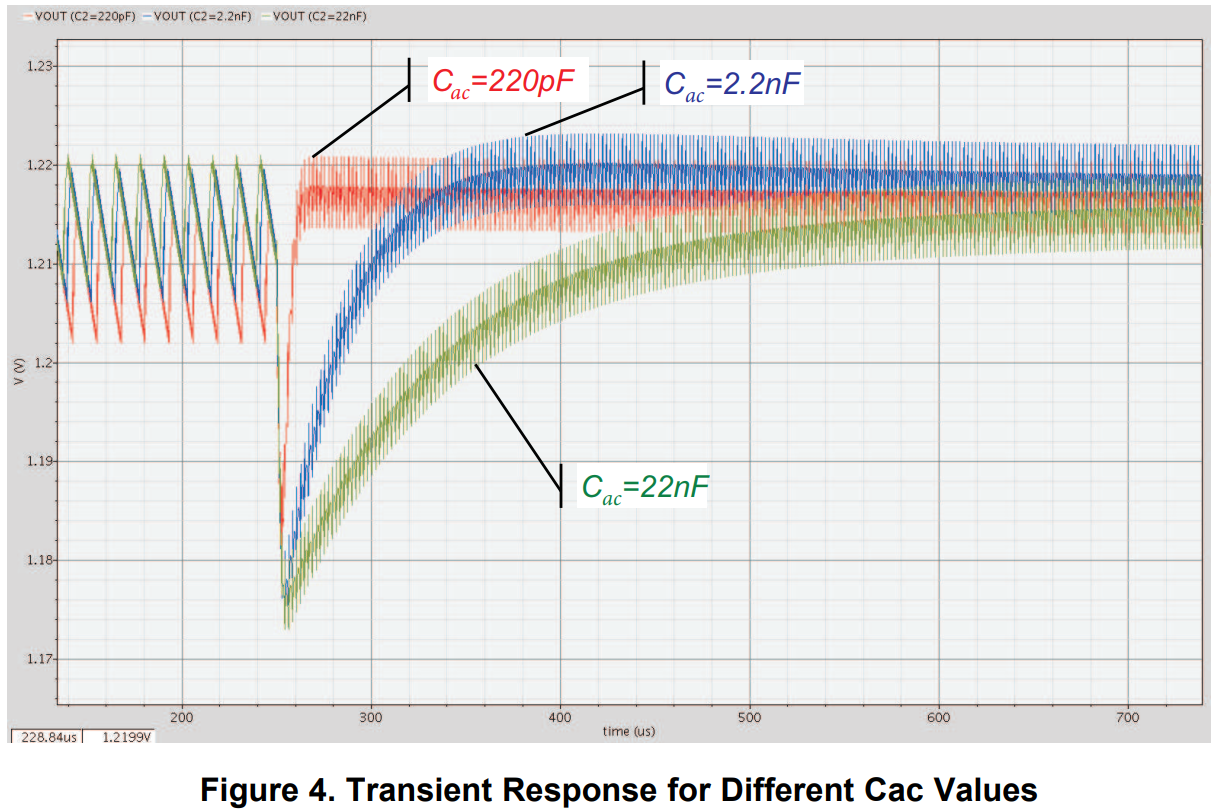

上式中,T_{Settle}为系统响应时间,C_{ac}越小,系统响应速度就越快。

6.3-如何设计纹波注入网络

由于TYPE 1 与TYPE 2 都很简单,所以这里只讨论如何计算TYPE 3 如何设计纹波注入网络。

6.3.1-STEP 1:确定Cac的取值

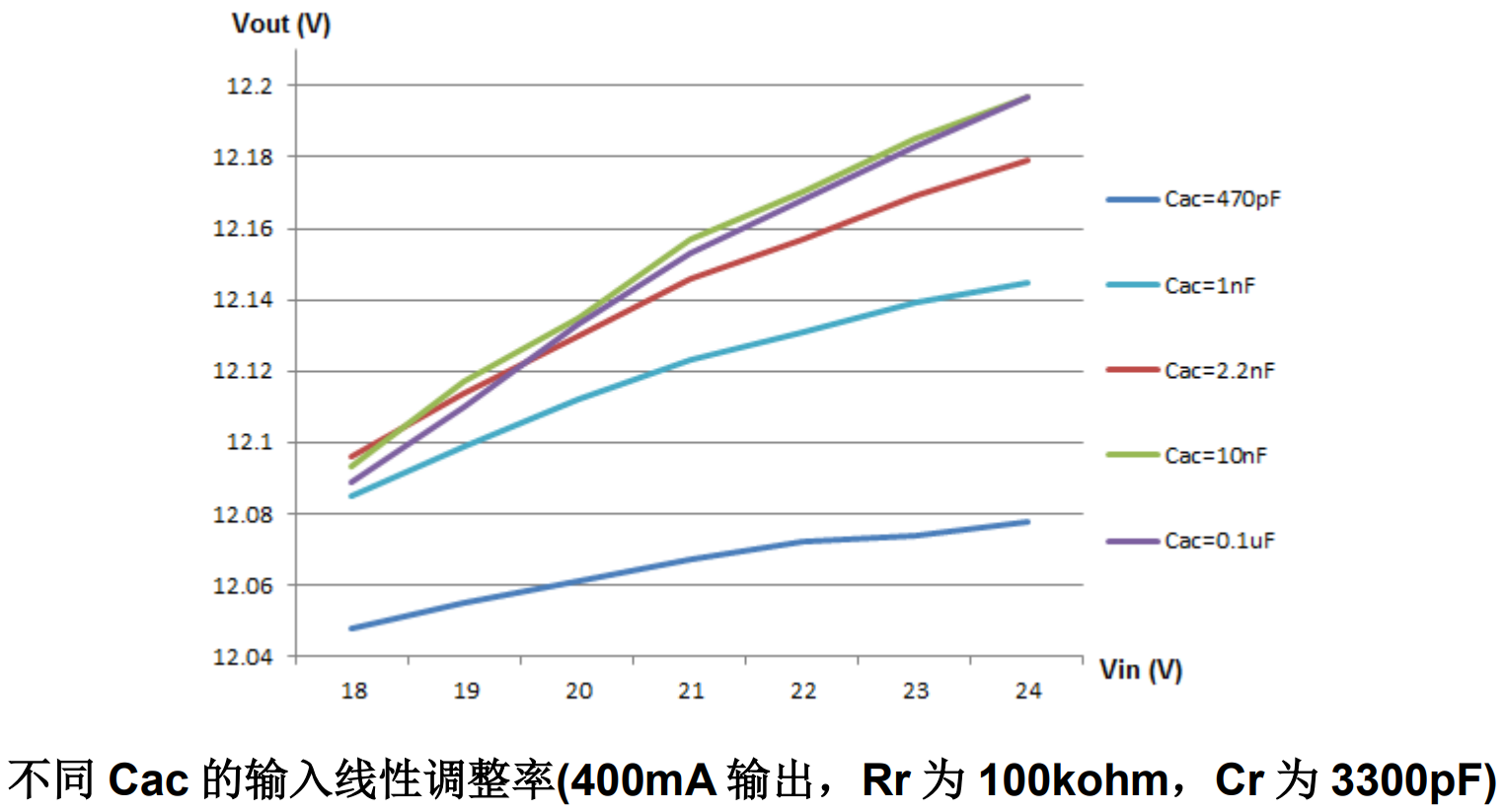

C_{ac}越小,系统的响应速度越快,低频纹波抑制越好,线性调整率越好,如下面几幅图所示:

我们根据判定条件①,计算出C_{ac}的最小值,再取一个略大于最小值的值即可。

注意,部分芯片的手册中会直接给C_{ac}取一个随意的值,例如10nF,不要这样做,会劣化系统的性能。

6.3.2-STEP 2:确定Cr的取值

根据判定条件②,计算出C_r的最小值,同样再取一个略大于最小值的值即可。

6.3.3-STEP 3:确定Rr的取值

根据判定条件③,计算出R_r的最小值,同样再取一个略大于最小值的值即可。注意此时要考虑最坏情况。

6.3.4-STEP 4:验证环路稳定性

根据判定条件④,验证环路是否稳定,注意此时同样要考虑最坏情况。

6.4-电压型(Voltage Mode)与电流型(Current Mode/Peak Current Mode)

如果你选择了模块,或是集成了补偿网络的转换器和控制器,并且没有加前馈电容那么你可以跳过此步骤,它们的环路通常不存在稳定性问题。

如果你选择了外部补偿的IC,它们会有一个补偿引脚,一般名为"COMP","VC","ITH"等;又或是期望更好的瞬态响应而给反馈电阻上并联了前馈电容,那么你需要按照此步骤来验证环路稳定性。

我们对环路有以下期望:

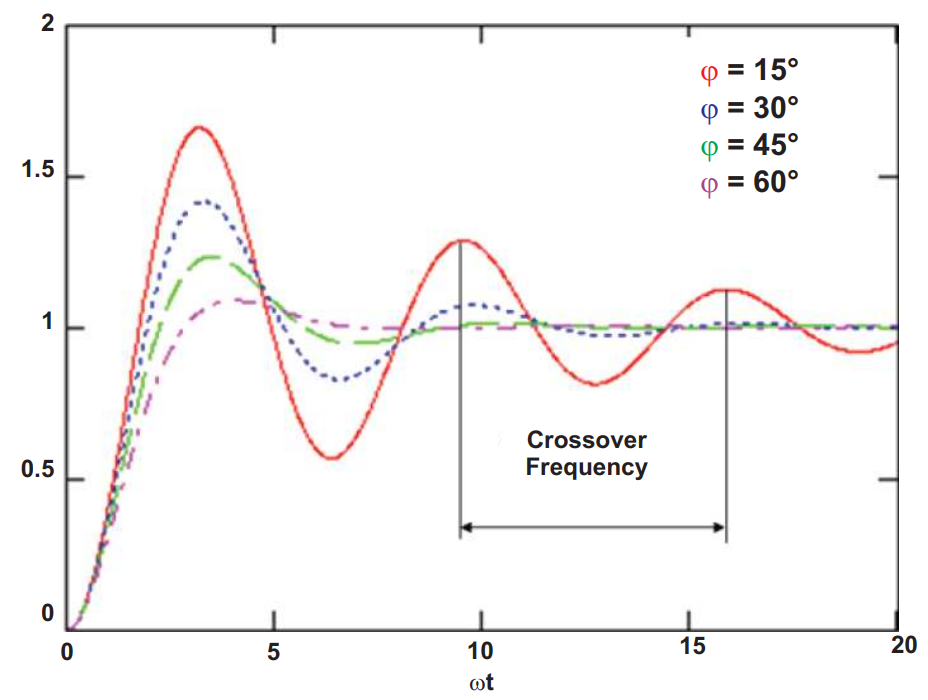

相位裕度PM:我们通常希望相位裕度在60°左右;更小的相位裕度可能导致系统不稳定,过大的相位裕度可能导致较慢的反应速度。

增益裕度GM:我们通常希望增益裕度在10dB以上,这样可使系统较稳定。

穿越频率fCROSS:穿越频率指环路增益为0时的频率,我们通常取穿越频率为1/20~1/5的开关频率;穿越频率越高意味着系统的环路带宽越大,拥有更好的瞬态响应;但为了避免开关频率对环路的影响,穿越频率也不能太高。

6.5-验证环路稳定性

验证环路稳定性有以下四种常用的方法:

6.5.1-手算

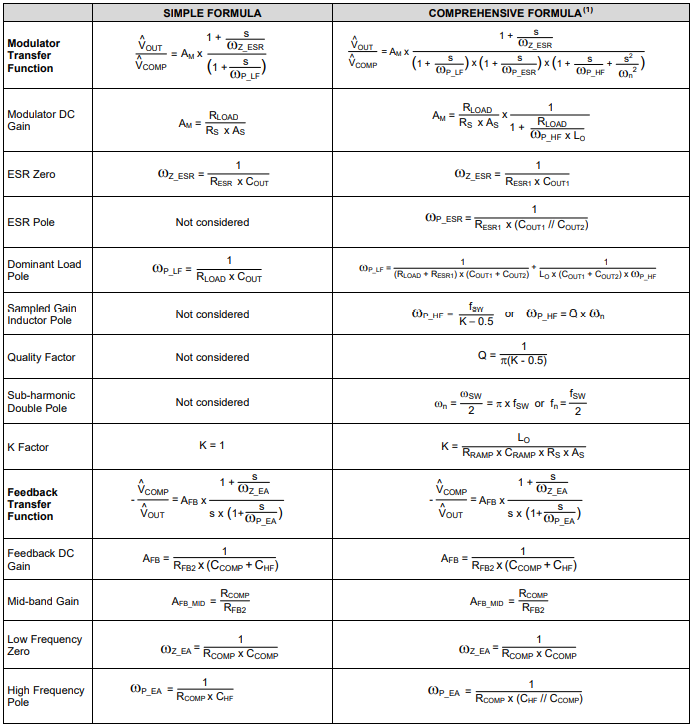

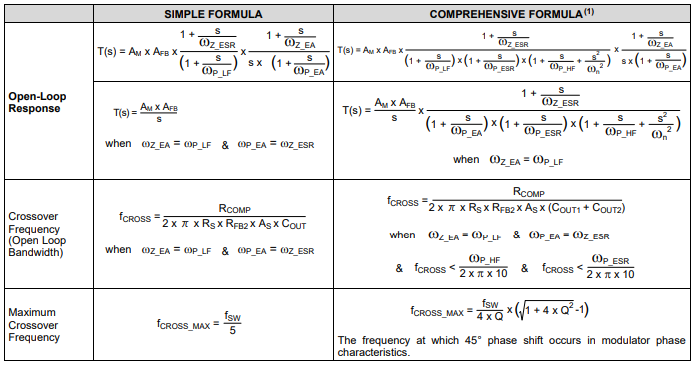

这是LM25117数据手册中完整的频率分析公式表:

你真的想手算吗?

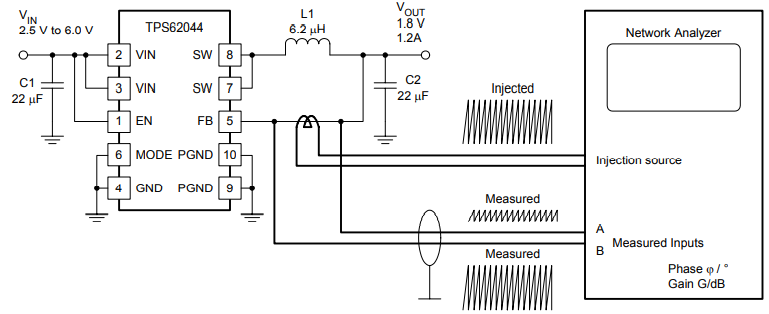

6.5.2-矢网分析

焊接好实际电路,并且用矢量网络分析仪来得出它的波特图,是最准确的方法。

但这个方法过于麻烦,并且矢网也不好搞,略过。

6.5.3-瞬态响应分析

6.5.3.1-瞬态响应分析穿越频率

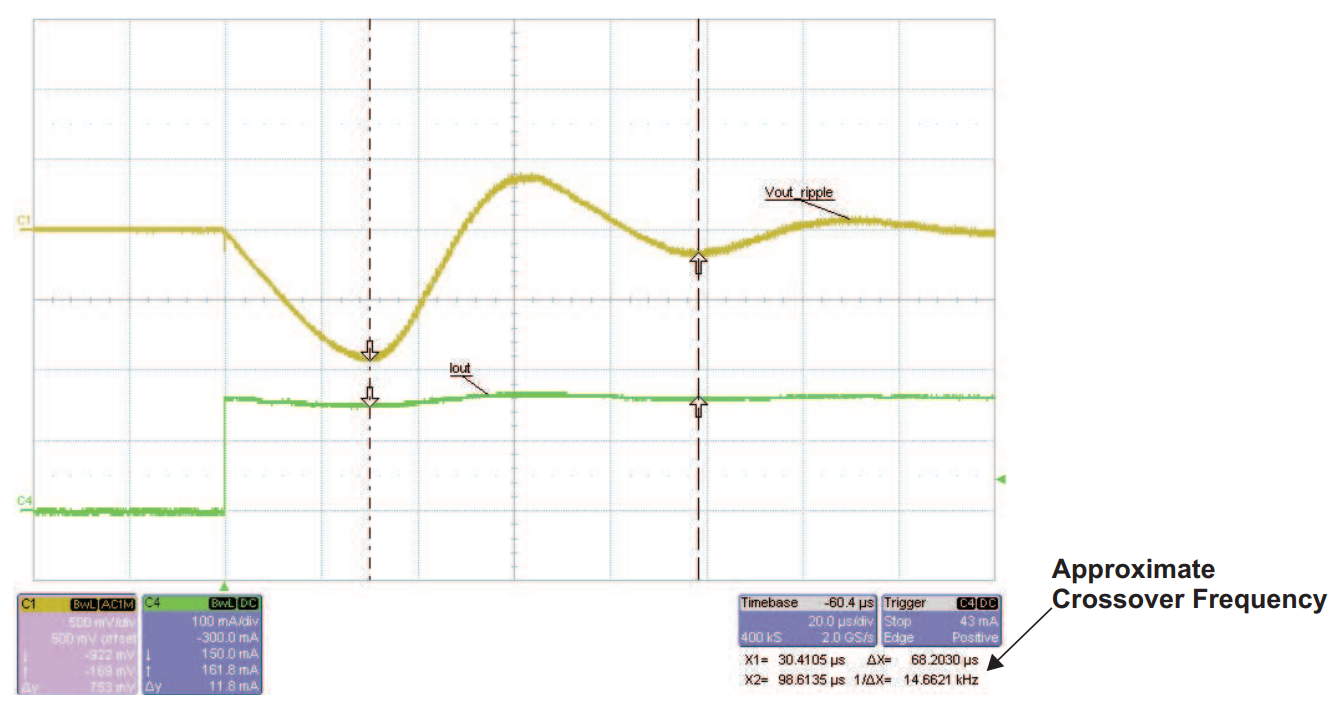

如上图所示,让DCDC变换器的输出电流突变,在相位裕度不足时,电压也会随之产生抖动后趋稳,记其中两个相邻的两个尖峰的时间差为t0,则fCROSS≈(1/t0)。

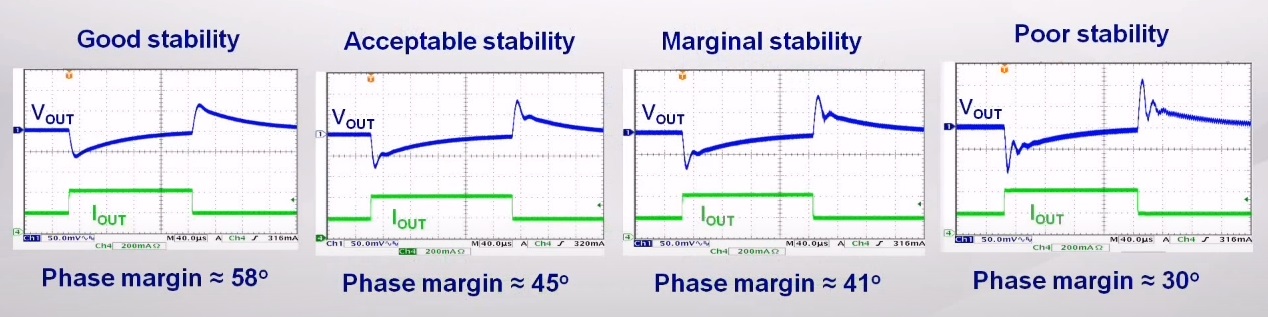

6.5.3.2-瞬态响应分析稳定性

上图显示了在不同相位裕度情况下的瞬态响应波形图,我们可以通过修改环路补偿容阻值,来获得一个60°左右的相位裕度,此时不会有振铃产生。

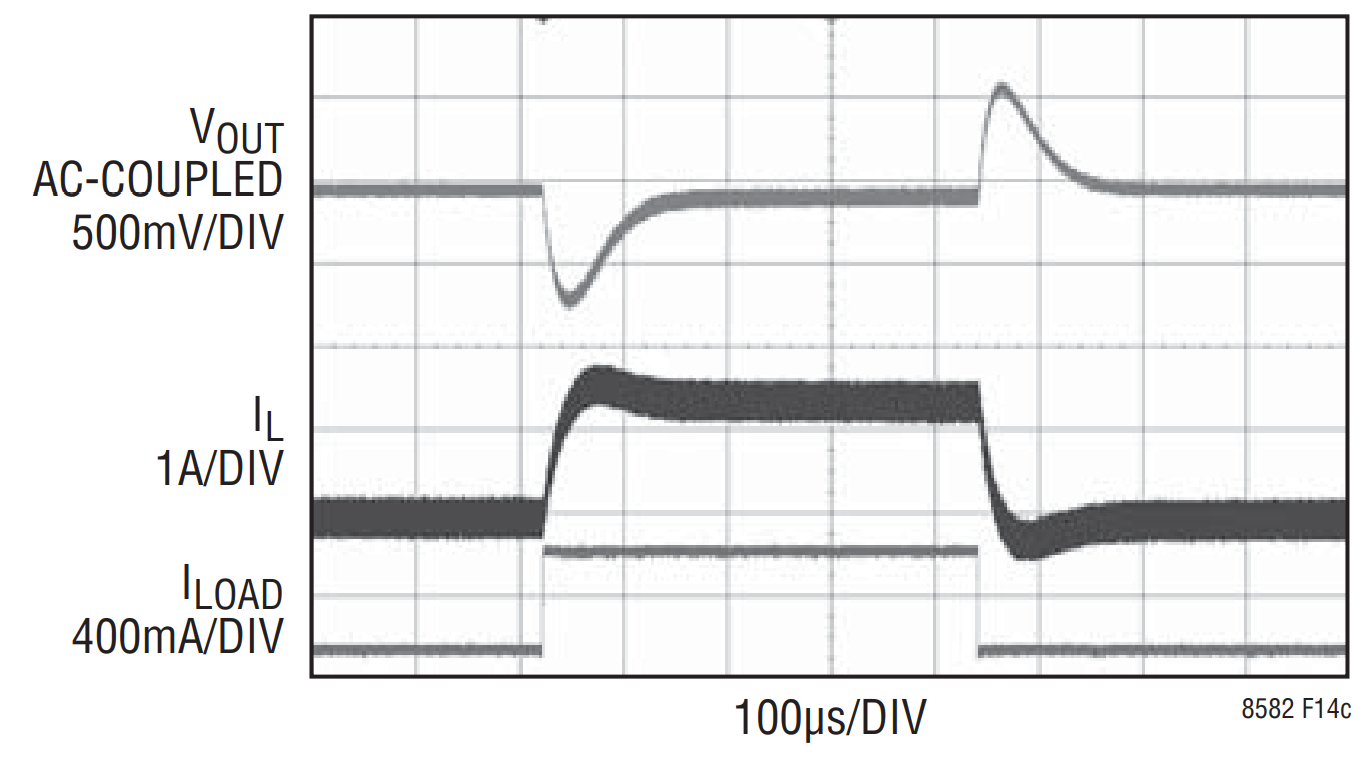

上图为相位裕度充足时的瞬态响应波形图,电压曲线平滑,没有振铃。

6.5.4-辅助设计软件

大厂基本都有各自的DCDC辅助设计软件,比如TI的WEBENCH,ADI的LTpowerCAD,MPS的DCDC Designer和Maxim的EE-Sim。这些软件可以帮助我们快速完成原理图设计,验证环路稳定性。

TI的WEBENCH为在线设计工具,无需下载,功能较为齐全,支持绝大部分TI的DCDC IC,但其速度较慢,并且可供选择的外围器件较少。

ADI的LTpowerCAD为离线设计工具,可以对你的设计进行非常详细的分析,并且可以与LTspice联动,但似乎是软件的原因,老是闪退。

MPS的DCDC Designer拥有在线和离线两个版本,功能一样,但是我强烈推荐使用离线版,速度快很多。软件本身比较简约,只给出必要的参数,不能像LTpowerCAD一样对你的设计进行详尽的分析,并且模型不准确,其中MLCC的模型几乎为理想电容:ESR与ESL均为0,容量不随直流偏压而变化。适合入门使用。

6.5.5-仿真

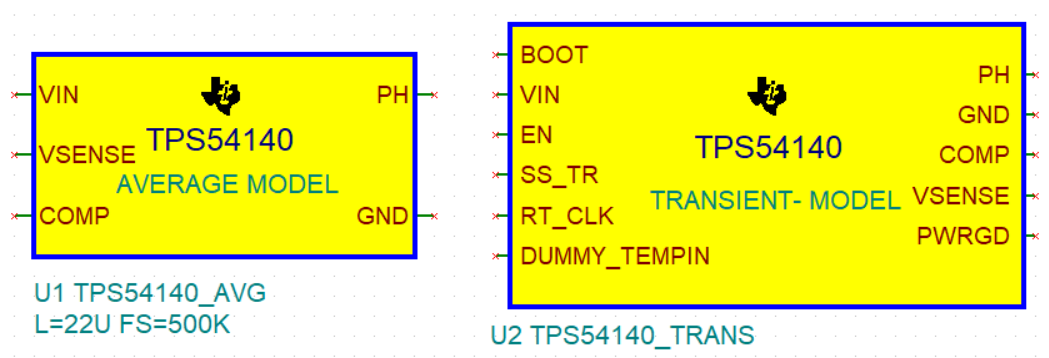

一般厂家给出的DCDC IC仿真模型有两种,平均模型(AVG)与瞬态模型(TRANS)。下图为TINA中TPS54140的两种模型。

如果厂家给出了平均模型,例如像TINA中给出的平均模型,那么用平均模型来得出DCDC转换器的环路小信号波特图非常简单,交流扫描即可,此处不再赘述。

但通常厂家给出的DCDC的模型是瞬态模型,不能用简单的交流扫描来得出环路小信号波特图。这里以LTspice为例,来讲解DCDC的环路稳定性分析方式,并给出参考SPICE命令。

6.6-使用瞬态模型来获得环路小信号波特图的方法:

6.6.1-第一步:绘制原理图

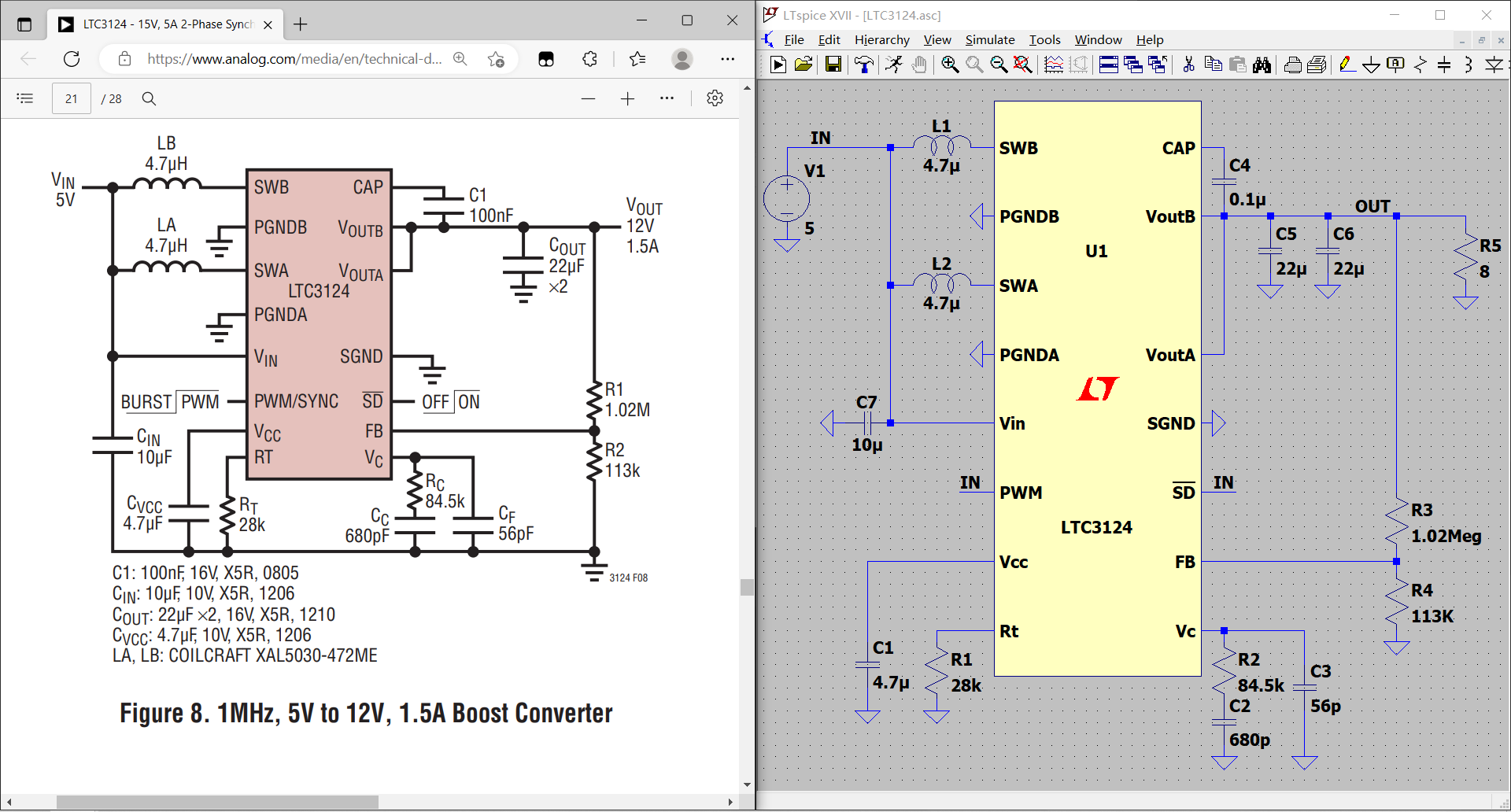

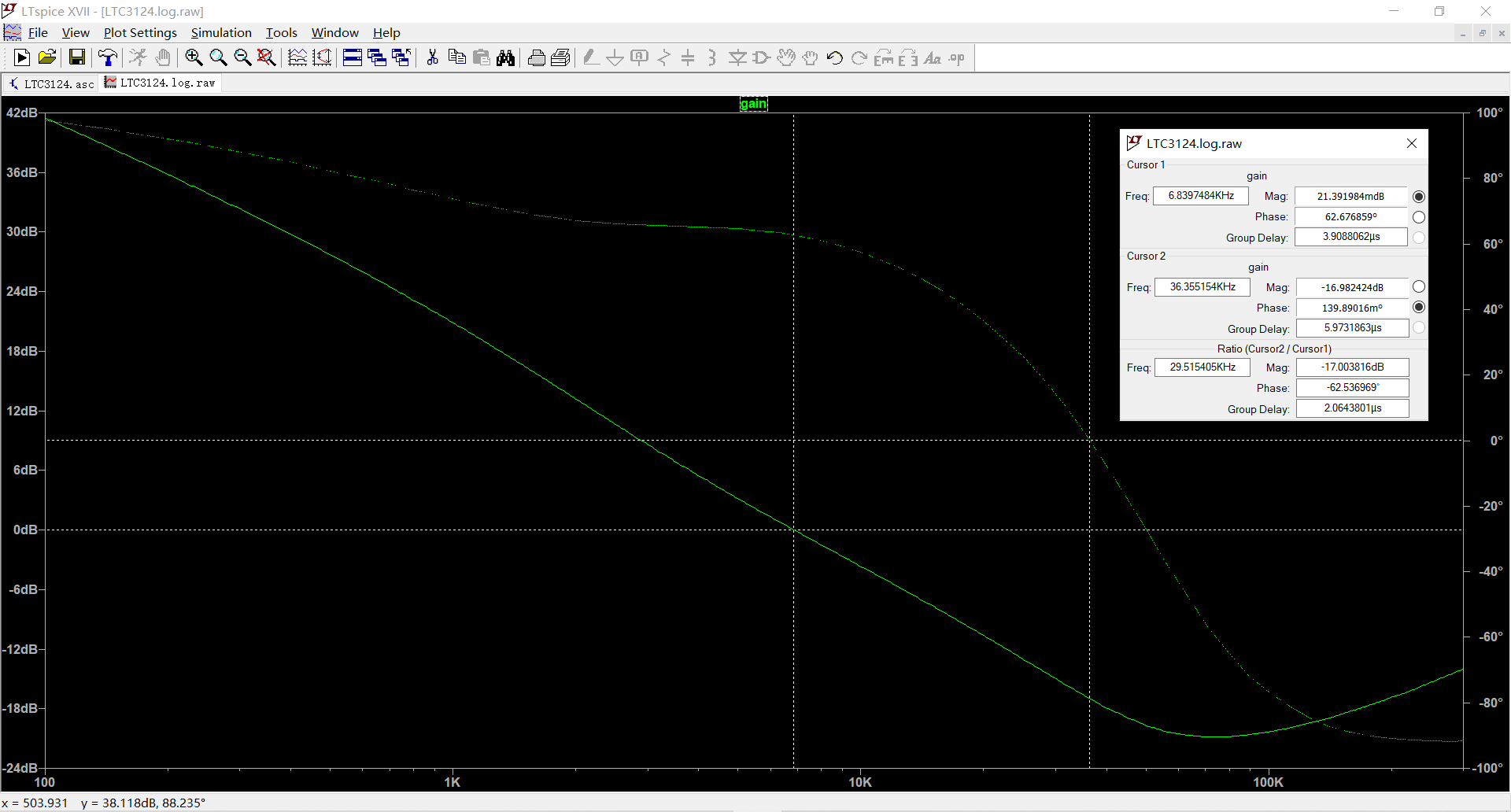

这里我按照LTC3124数据手册中的典型应用来绘制原理图,方便之后与实测波特图对比。

6.6.2-第二步:求稳定时间

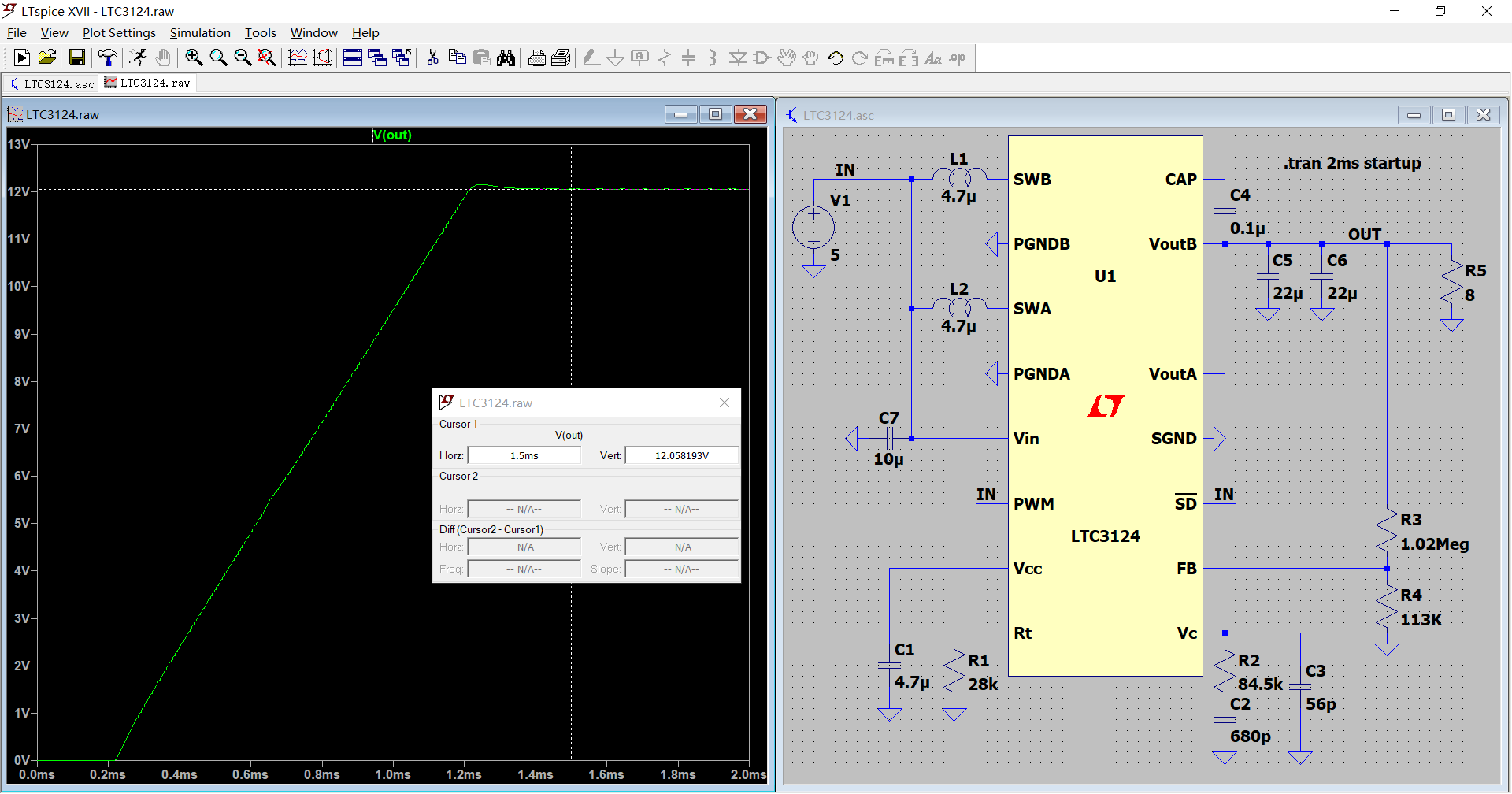

我们首先进行一个瞬态仿真(.tran 2ms startup),观察系统稳定所需的时间。

观察输出节点的电压波形图,我们可以看到,在1.5mS后整个系统基本上已经稳定,我们取稳定时间为1.5mS。

6.6.3-第三步:测试信号注入

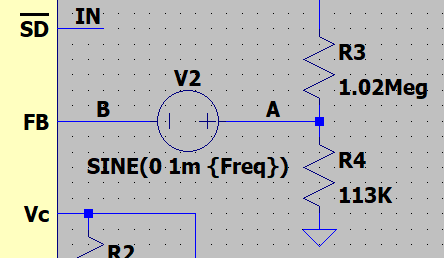

将原理图中FB引脚与分压电阻断开,插入一个电压源。

将交流电压源两边的节点分别命名为A与B。

将电压源的直流偏置设置为0。

幅值通常设置为1m~20m,较小的幅值会使信噪比下降,较大的幅值会使频响不准确,这里设置为1m。

由于我们需要扫频,所以我们这里将频率设置为一个变量,名为"Freq",后续我们会在SPICE命令中调用它。

6.6.4-第四步:加入完整的SPICE命令

参考SPICE命令(以LTSpice为例):

.measure Aavg avg V(a)

.measure Bavg avg V(b)

.measure Are avg (V(a) – Aavg) cos(360 time Freq)

.measure Aim avg -(V(a) – Aavg) sin(360 time Freq)

.measure Bre avg (V(b) – Bavg) cos(360 time Freq)

.measure Bim avg -(V(b) – Bavg) sin(360 time Freq)

.measure GainMag param 20 * log10(hypot(Are,Aim) / hypot(Bre,Bim))

.measure GainPhi param mod(atan2(Aim, Are) – atan2(Bim, Bre) + 180,360) – 180

.save V(A) V(B)

.option plotwinsize = 0 numdgt = 15

.param t0 = 1.5m

.tran 0 {t0 + 25 / freq} {t0}

.step dec param freq 100 300K 20

其中,measure命令用作傅里叶变换,计算增益和相位,一般不需要修改。

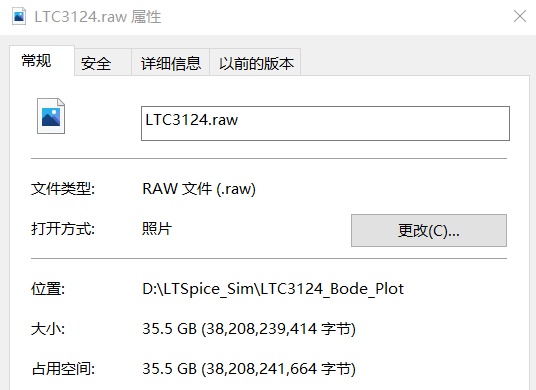

save命令为让仿真器只保存我们关心的A,B两节点的电压数据,此命令很重要,不加不影响仿真结果但可以轻松让内存和硬盘空间爆掉,一般不需要修改。下图的仿真结果文件为加上save命令后的大小,不加的话。。。节点数翻好多倍,还要加上电流数据。。。。。。

option中的plotwinsize=0命令为关闭仿真结果数据压缩,numdgt=15命令为将数据位数设置为15位;这两个命令均用于提升精度,一般不需要修改。

最下方的三行命令需要根据不同的原理图以及需求来修改参数

.param t0=1.5m

t0为DCDC变换器进入稳态所需的时间。由第二步所得的结果,此处我们将t0设置为1.5mS。过长的t0会增大仿真时间,过短的t0会产生不正确的结果。如果你观察到生成的波特图很奇怪,比如波特图像锯齿波,或者得到了负4000°的相位裕度,那么有可能是t0过短。

.tran 0 {t0+25/freq} {t0}

此命令使仿真器记录从t0开始的25个周期的时间,多个周期取平均可以减小误差。将"25"改小可以缩短仿真时间,但会增大误差。一般15~25为较合适的取值。

.step dec param freq 100 300K 20

此命令设置扫描范围为100Hz~300kHz,每十倍频20个点。

为了节约时间,实际使用时,我们可以先仿一小个频率区间,并且降低精度,如设置为每十倍频5个点,来大致确定fCROSS,之后再进行高精度的完整频率扫描。

宽范围,高精度扫描所需的仿真时间很长,此处仅为与数据手册中的波特图做对比用,实际使用时可以只扫描包含从Gain=0到PM=0的一小段,来判断相位裕度PM,增益裕度GM及穿越频率fCROSS。

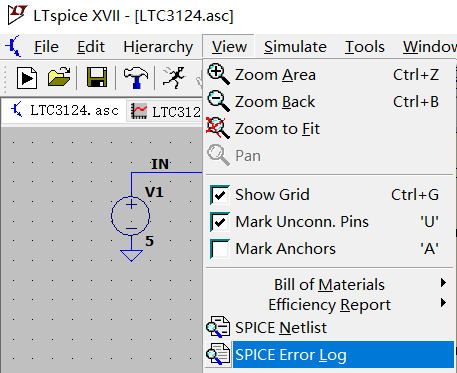

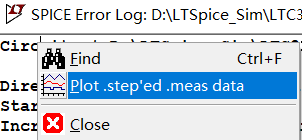

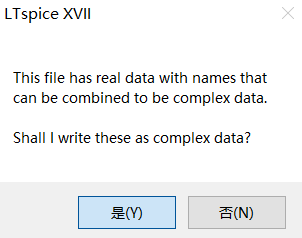

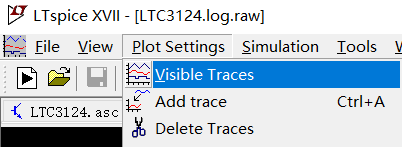

6.6.5-第五步:在SPICE Error Log中查看结果

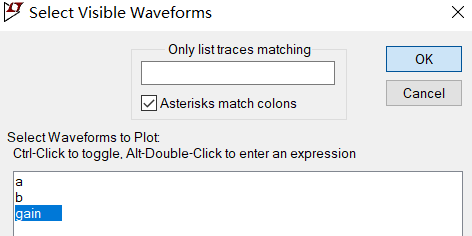

View -> SPICE Error Log -> 右键 -> Plot .step’ed .meas data -> YES

Plot Settings -> Visible Traces -> gain -> OK

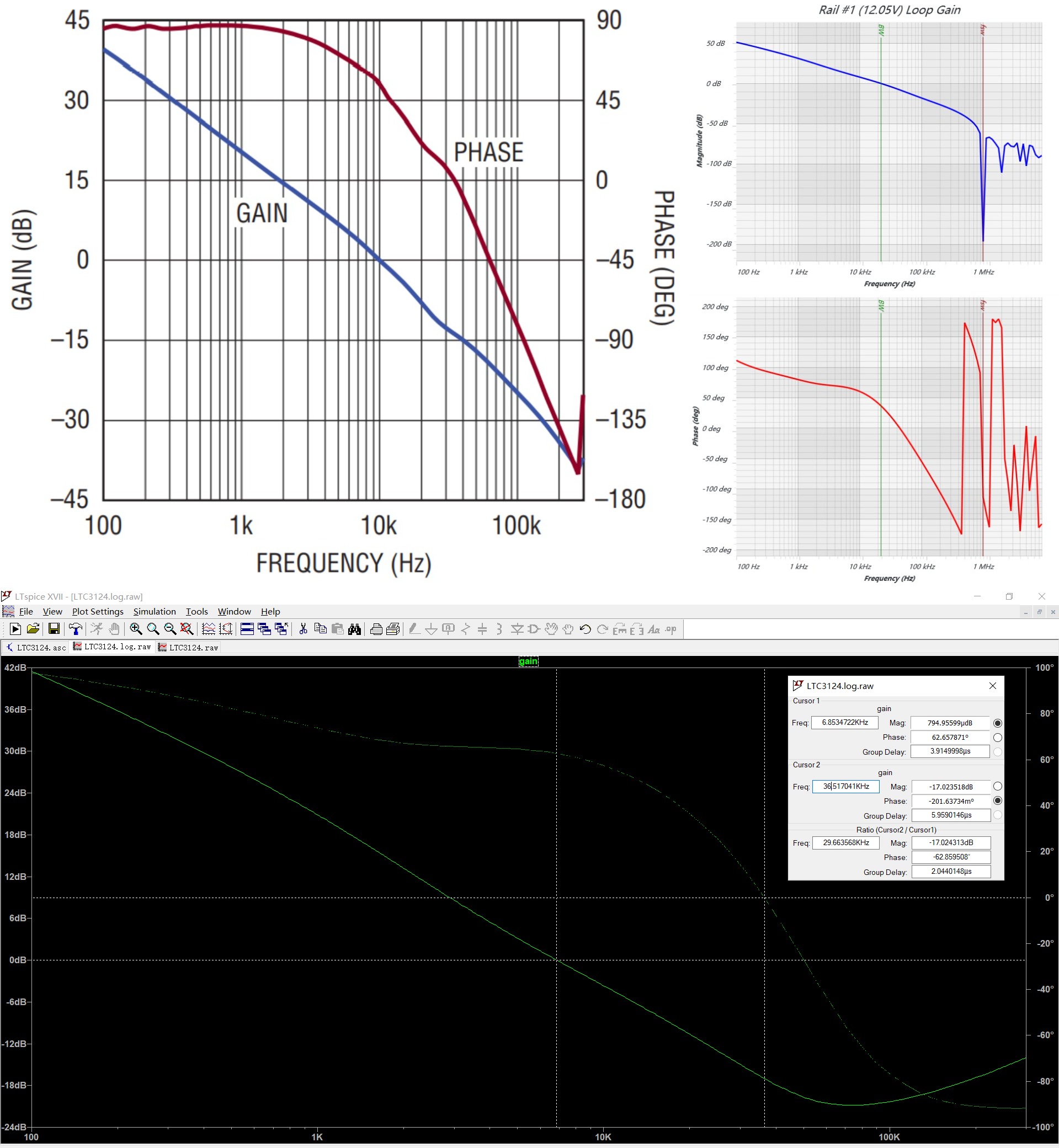

图中实线为增益,虚线为相位裕度,我们从图中可看出,此原理图的相位裕度约为62°,增益裕度约为17dB,穿越频率约为6.8kHz。

6.7-几种方法,不同厂家软件得出的波特图准确性对比:

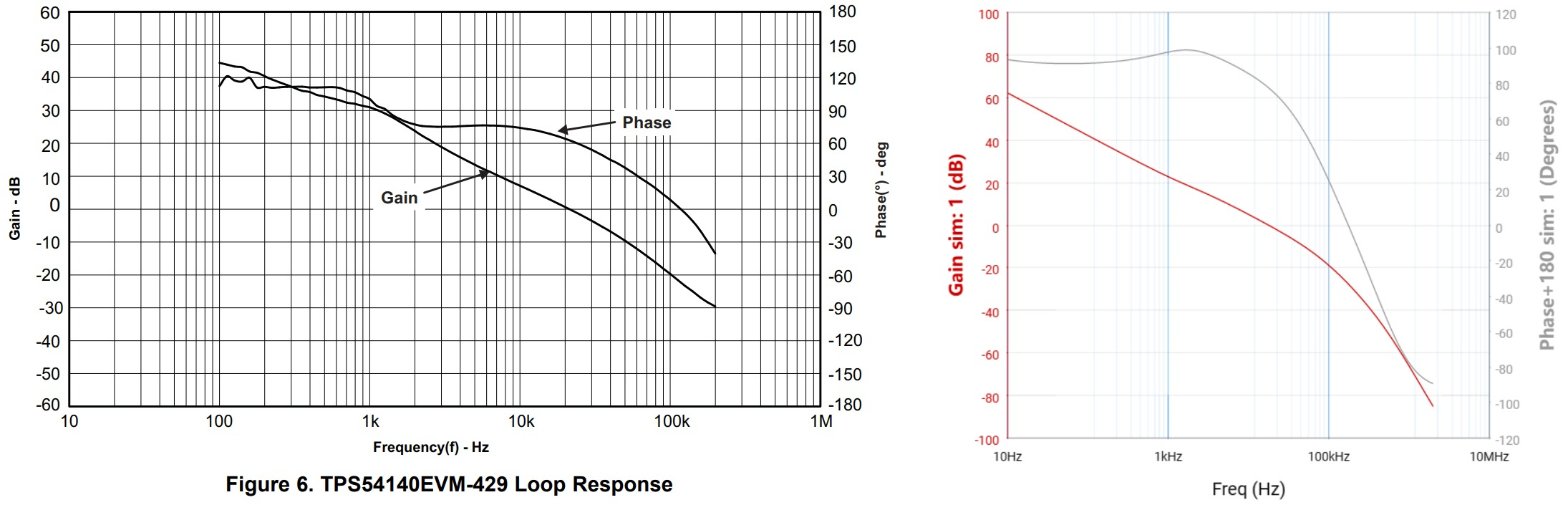

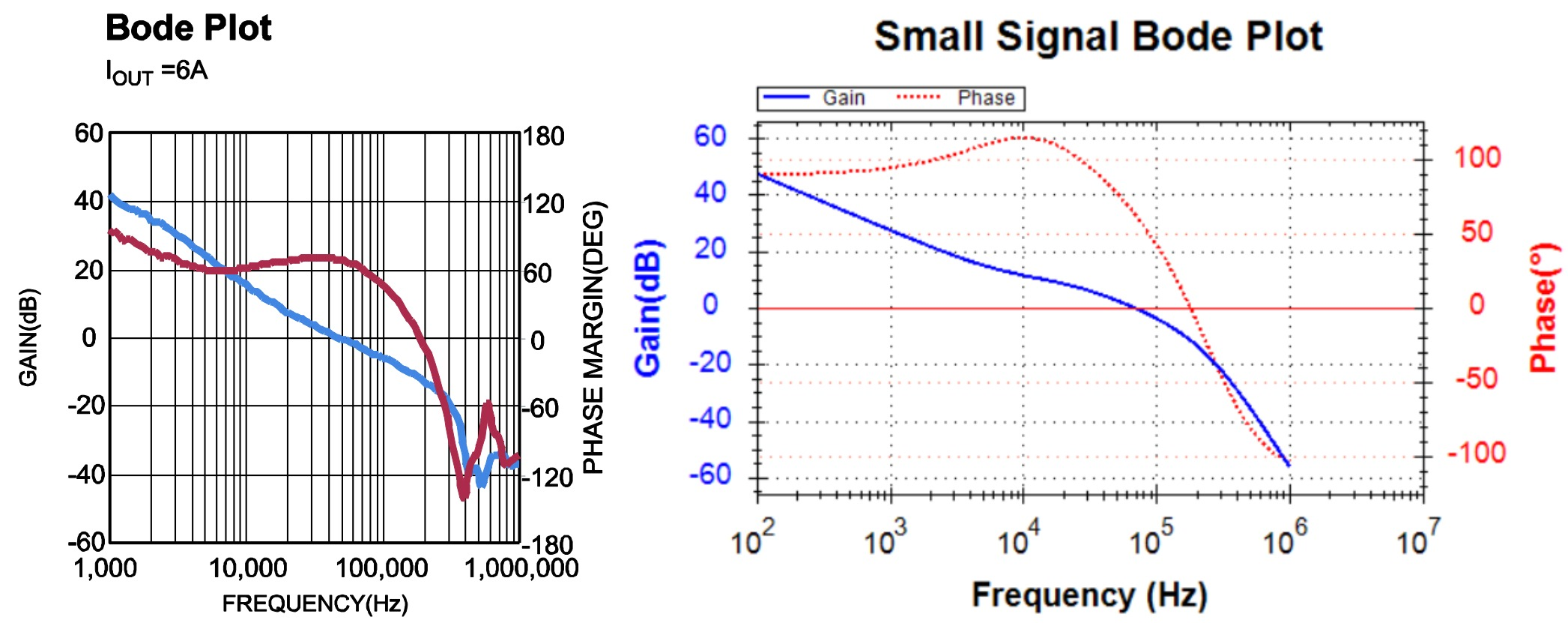

上图左侧为TPS54140的数据手册中的实测波特图,右侧为WEBENCH中生成的波特图。原理图一致。

上图左侧为MP2229的数据手册中的实测波特图,右侧为DCDC Designer中生成的波特图,原理图一致。

上图上方左侧为LTC3124数据手册中的实测波特图,上方右侧为LTpowerCAD中生成的波特图,下方为LTspice中仿真得到的波特图。

原理图均一致。

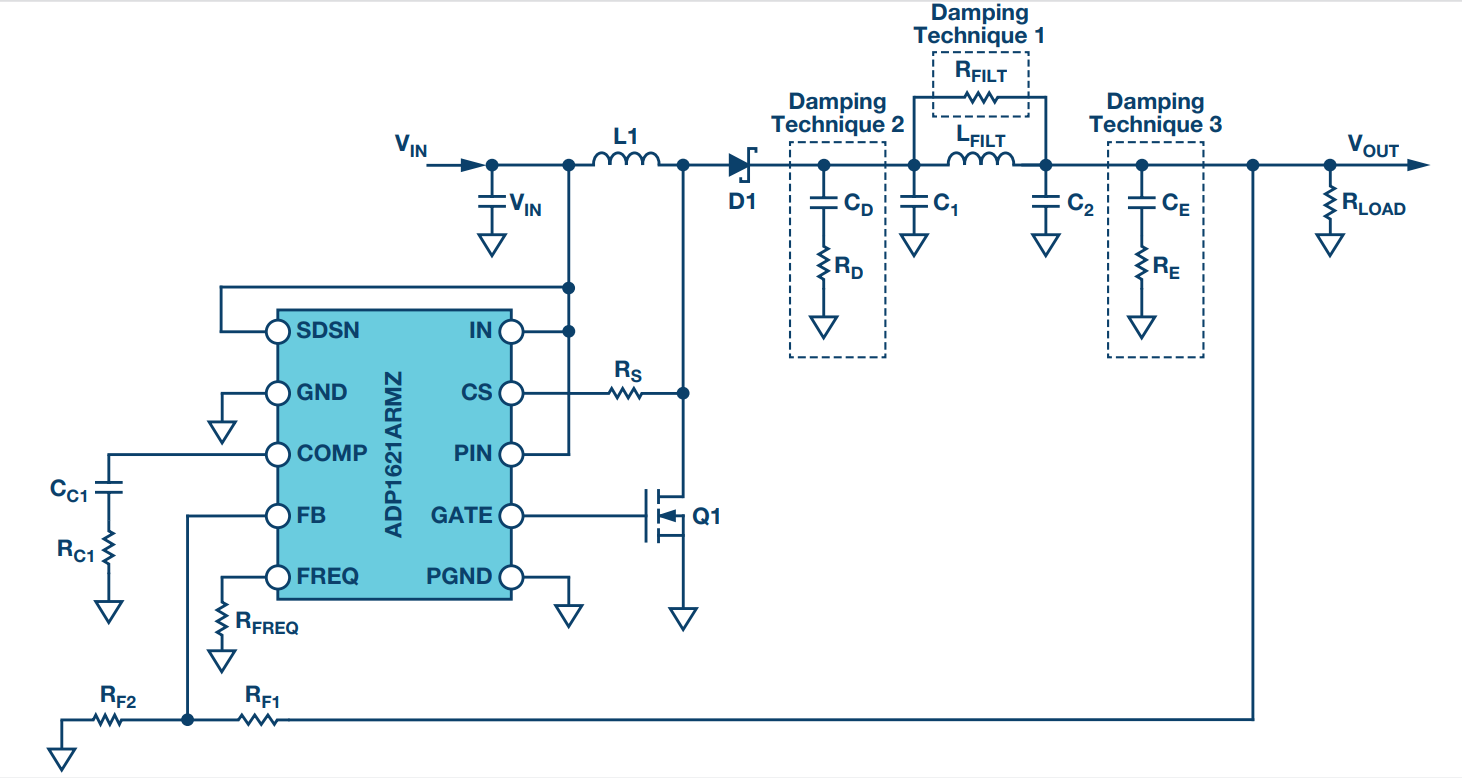

7-STEP 7: 是否加入额外的滤波器?

额外的滤波器可以有效降低电压纹波,并且改善EMC。

加入滤波器的位置建议放在高di/dt环路之前/之后,例如Buck的输入端,Boost的输出端。

也可以在有电感的端口之后再加上二级滤波,来达到更好的性能。

额外的滤波器一般为Π型滤波器,由电容+电感/磁珠组成。一般一级滤波器用电感,二级滤波用磁珠。

在加入额外的Π型滤波器时,要注意品质因数Q带来的增益尖峰的问题,设计不当的滤波器反而有可能放大纹波。

一般不将二级滤波电路放在反馈环里,因为除了像TPS6291X这样集成了二级滤波补偿的IC,其他的IC一般不针对二级滤波进行补偿,将二级滤波放入反馈环中可能导致稳定性问题,或是给环路补偿电路容阻取值计算带来麻烦。

当然,如果所选的IC的补偿网络是外置的,那么可以将二级滤波器放入反馈环内,这样有助于改善负载调整率与瞬态响应,但补偿计算会变复杂,如下图所示:

上图中,为了避免LC的Q值过高导致的增益尖峰的出现,还在LC上加上了电阻,来降低Q值。

参考资料:

- Power Topologies Quick Reference Guide SLYU032

- Optimizing Transient Response of Internally Compensated dc-dc Converters With Feedforward Capacitor SLVA289B

- Evaluation and Performance Optimization of Fully Integrated DC/DC Converters

- Basic Steps in Generating a Bode Plot of SMPS

- OPTI-LOOP Architecture Reduces Output Capacitance and Improves Transient Response AN76

- Compensation for Current Mode Control SEPIC Converters

- A Unified LTspice AC Model for Current-Mode DC-to-DC Converters

- Analog Dialogue Volume 44 Number 2

- Synchronous Zeta Converter Outperforms The SEPIC H2PToday1405

- Designing A SEPIC Converter

- Monitor Heat Dissipation in Electronic Systems by Measuring Active Component Die Temperature AN3500

- Using the TPS5430 as an Inverting Buck-Boost Converter SLVA257A

- Control-Mode Quick Reference Guide SLYT710B

- Power Loss Calculation With Common Source Inductance Consideration for Synchronous Buck Converters SLPA009A

- An Improved Topology for Creating Split Rails from a Single Input Voltage AN-1106

- Switch Mode Power Supply Current Sensing—Part 2: Where to Place the Sense Resistor

- Switch Mode Power Supply Current Sensing—Part 3: Current Sensing Methods

- Operating Voltage Ratings For Inductors

- It’s All About Voltage Ratings – New Addition to Power Inductor Ratings

- Semiconductor and IC Package Thermal Metrics

- MPQ4470 – Application Note AN095

- Selecting an Ideal Ripple Generation Network for Your COT Buck Converter SNVA776A

- Stability Analysis and Design of COT Type-3 Ripple Circuit SNVA874

- D-CAP2 Frequency Response Model, based on frequency domain analysis of Fixed On SLVA546

- Controlling Output Ripple & Achiev ESR Indep Constant On-Time Reg Designs SNVA166A

- D-CAP Mode with all ceramic output capacitor application SLVA453

- Designing Second Stage Output Filters for Switching Power Supplies

- Generating Multiple Isolated Bias Rails for IGBT Motor Drives with Flyback, SEPIC, and Ćuk Combination AN-1316

- More Boost with Less Stress: the SEPIC Multiplied Boost Converter AN-1126

- Diode fundamentals, characteristics and applications

- SiC MOSFET Bridge Configuration

- 智能电表:采用LM5017实现1‰纹波输出 ZHCA611

- 使用 LMR36520 设计隔离式降压 (Fly-BuckTM) 转换器 ZHCAB40A

- 恒定导通时间(COT)控制的过去与现在

- 控制方式 (电压模式、电流模式、迟滞控制)

- 消除 Buck 转换器中的 EMI 问题 AN045

- 功率电感器的啸叫对策

- 音频产品Buck转换器设计考虑 ZHCAC02

- IC 的热特性-热阻 ZHCA592

- 直流开关电源结温的直接测量法

- 一文让你了解静态电流和关断电流

- 热阻和热特性参数的定义

- Characteristics of MLCC

- Low-ESL MLCCS

- MLCC Capacitance Change & Effect on a SET

- LT8582 – Datasheet

- LTC3124 – Datasheet

- LTC3810 – Datasheet

- LTC3624 – Datasheet

- LTC7820 – Datasheet

- LM3150 – Datasheet

- LM5169 – Datasheet

- LM5164 – Datasheet

- LM5017 – Datasheet

- LM25117 – Datasheet

- LM5118 – Datasheet

- TPS54140 – Datasheet

- TPS5450 – Datasheet

- TPS62913 – Datasheet

- MP4470 – Datasheet

- MP2229 – Datasheet

- MP3426 – Datasheet

- MPM3620 – Datasheet

- MAX1811 – Datasheet

- MAX889 – Datasheet

- IRF6644 – Datasheet

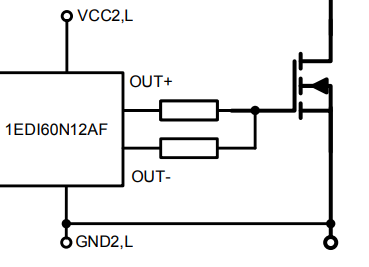

- 1EDI60N12AF – Datasheet

- SCT2A23STER – Datasheet

![Read more about the article 电子入门教程[02]—会呼吸的光](https://www.emoe.xyz/wp-content/uploads/2019/09/1-300x221.png)