本文目录

精密电压源设计

唔,看到标题,你就可以预见——这又是一个烧钱的项目。

但是,哪个男孩子不想要一个精密电压源呢?!!!

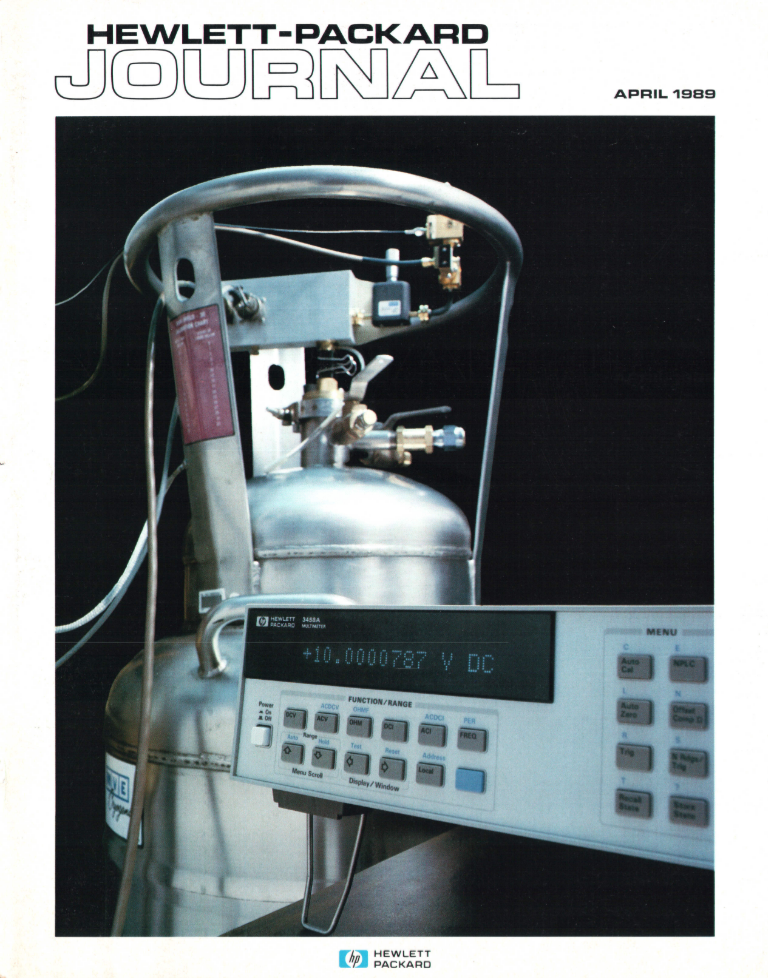

Josephson-Junction Array 标准电压源与HP3458A 8位半数字万用表

基准电压源的关键参数

基准电压源器件和线性稳压器的结构十分相似,不过后者能够输出更大的电流,而前者在设计时会更多的侧向于保证其精度与稳定性。

一般我们选择一个基准电压源,主要考虑它的如下指标:

- 输入输出电压,及最小压差

- 初始精度误差(容差)

- 温度漂移系数

- 噪声

- 短期稳定性与长期稳定性

- 负载灵敏度

- 线路灵敏度

- 动态负载响应

- 封装形式与湿度敏感性

- ……

一长串指标看着是不是头大了…没办法咯,既然来到了精密的领域,设计时就必须考虑周全,事事谨慎。

各家半导体公司都有基准电压源芯片产品,比如ADI的LTZ1000、ADR系列,TI的REF系列。国际电压值标准是由上面那张图中的铁罐罐所标定的。它背后的理论基础是约瑟夫森效应(Josephson effect),是一种巨观量子效应。我国最早的电压基准由中国工程院院士-高洁负责主导完成。

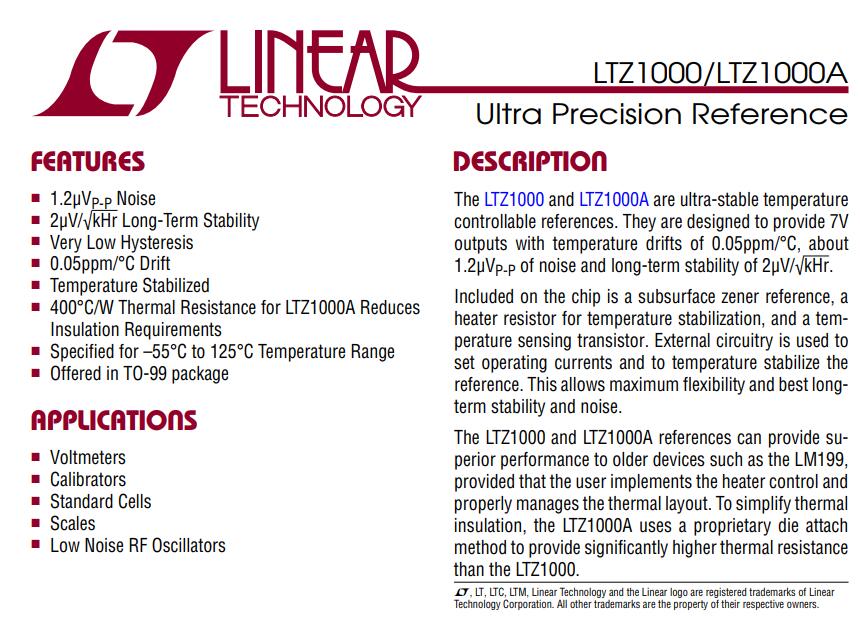

而商用电压基准源的最高水平是Linear Technology(现属于ADI)在1983年设计并生产的LTZ1000系列。ADI收购LT之后,使用更先进的工艺和技术,又推出了新一代超精密电压基准源ADR1000系列,相比前者具有更低的噪声,不过温度系数竟然不如LTZ1000,不懂。

基准电压源的诅咒

不过电压基准源好是好,但是它却不是那么的灵活。一般电压基准源IC在设计时就被设计者设下了永伴其身的诅咒,只能输出固定的电压值。(当然诅咒的效力是会随着时间流逝与环境变化而逐渐消失的…)比如说大名鼎鼎的LTZ1000,输出电压在7V-7.5V左右,是个定值。如果我们想得到任我们随意掌控的基准电压源,我们就需要一些特殊的技术手段了~

- 1.使用电阻分压器

- 2.使用高分辨率DAC器件

- 3.

电子黑洞(哈哈哈其实我在嘲讽某些搅乱市场秩序的老烧。)

电阻分压器

根据欧姆定律,我们容易得知,使用合适的电阻组合对一个固定电压分压,可以得到我们想要的另一个电压。但事情可没有这么简单——你怎么知道电阻的阻值是恒定不变的呢?况且,电阻中存在热噪声,其均方根值与电阻阻值成正比,它也会为我们的电压基准测量带来不便。其次,我要怎么保证我使用的分压电阻的比率是精确的呢…毕竟每个电阻都有误差。

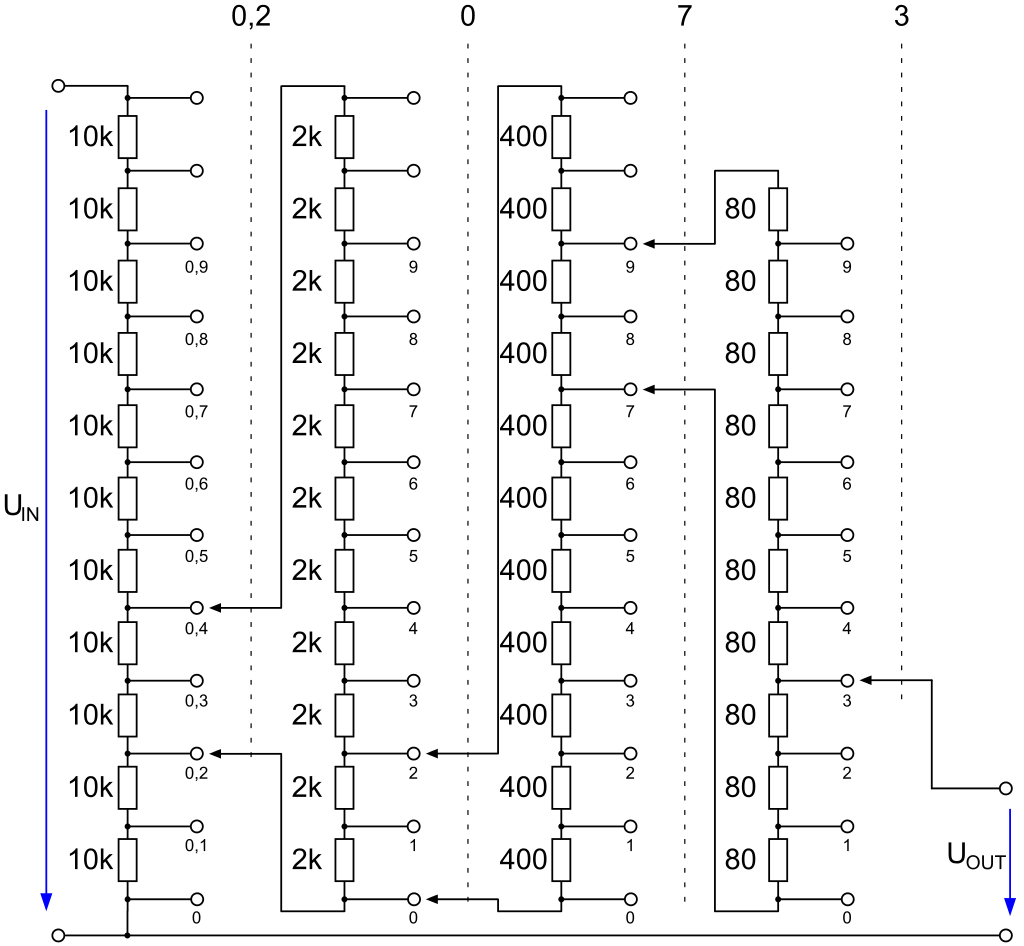

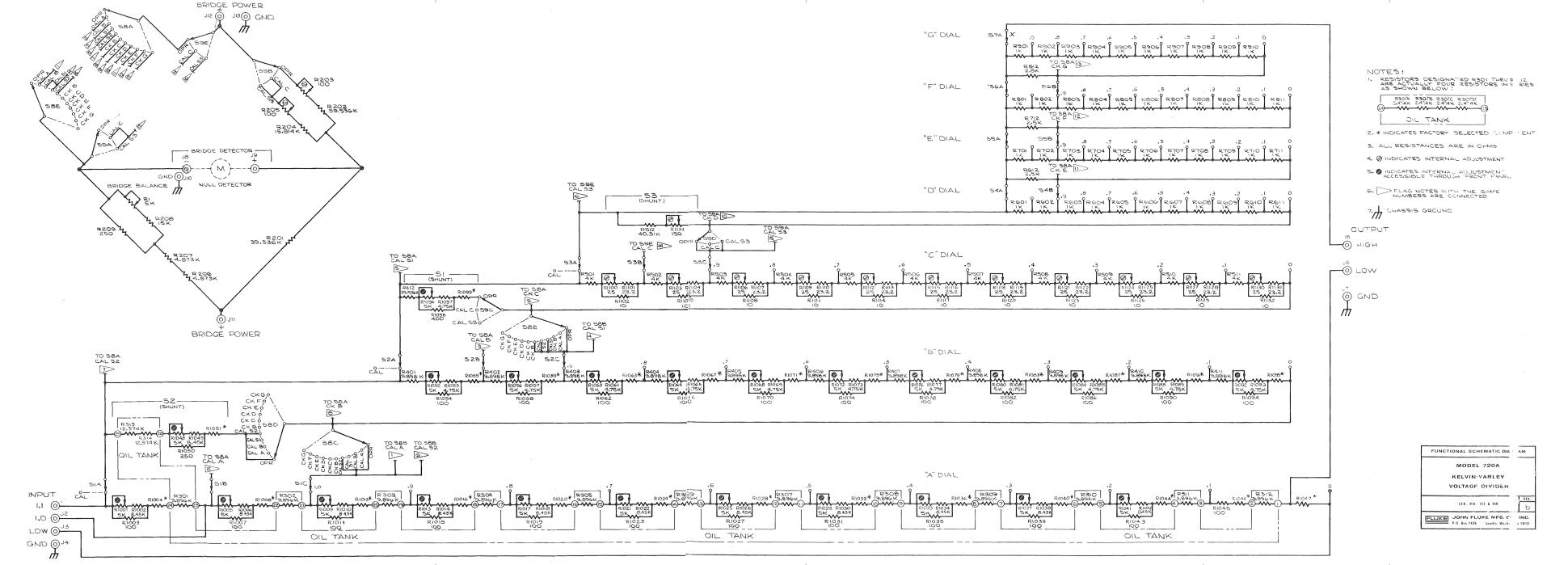

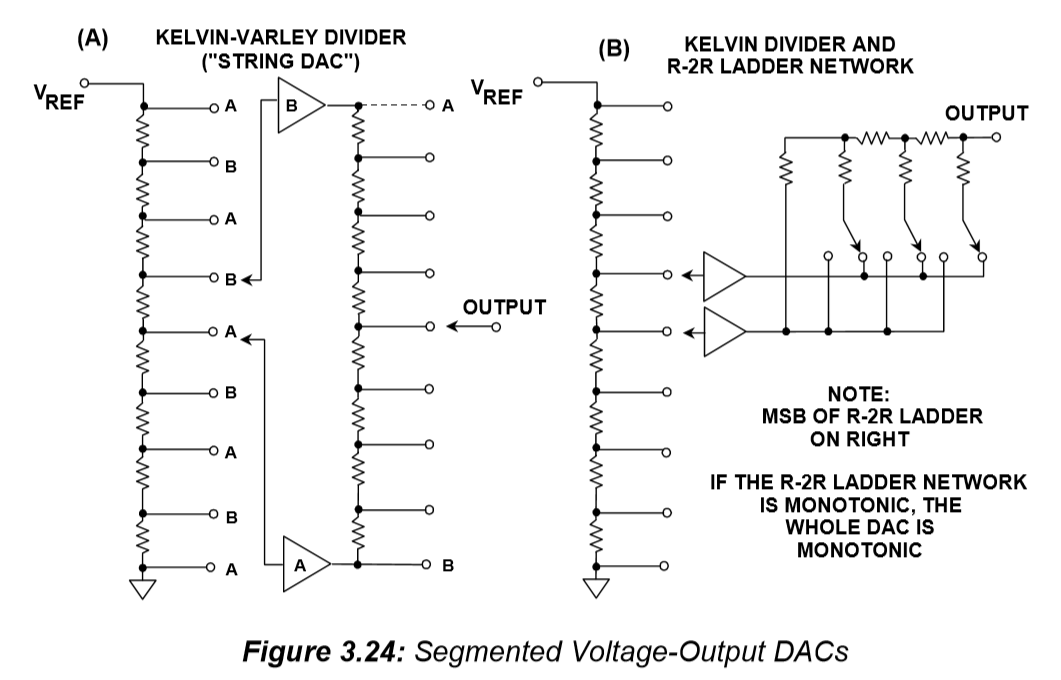

不过,如果不计成本,是可以使用电阻分压的方案的。我们可以使用Kelvin-Varley Divider结构来简化电路设计、减少器件使用,同时提高稳定性:

如果我们要将一个已知的电压细分为1000个档位(也就是1000等分),最直接的想法可能是串联1001个同样阻值的电阻(当然,不可能完全阻值相同,所以使所有电阻器精密匹配的过程是极其…痛苦且烧钱的。)。而Kelvin-Varley Divider可以使用更少的器件来完成分压工作,虽然它同样要求电阻精密匹配,但是数量上直接少了2个数量级。

Kelvin-Varley Divider的设计思想是使用 级联(cascaded)结构。一级包含11个精密匹配电阻,它们将电压细分为10个档位,然后通过设计电阻值让前后级的输入输出阻抗匹配,即可完成极为精密的细分工作。

Fluke 720A就是一款K-V分压器。它的设计我只能说…十分奢侈。不过这也是没办法的事233.

要制作一个K-V分压器,需要若干阻值成比例关系的精密匹配电阻,同时需要保证所有的电阻的温度变化趋势相同,最好为同一温度。Fluke使用了冷却油浸设计来保证关键部分的电阻器的温度保持一致。

当然,720A是正儿八经的校准仪器,一般是用来做计量校准工作用的。他不是特别适合作为随身携带的电子设备使用…(好吧随身携带这个要求是我提的,我喜欢能随身带的:D)

精密DAC器件

现代半导体技术已经能在一定程度上做出"理想"器件了。比如说使用激光在硅片上雕刻形状,来精细控制硅电阻以实现匹配,通过这种硅片上匹配技术,能制造许多高精度的模拟器件。

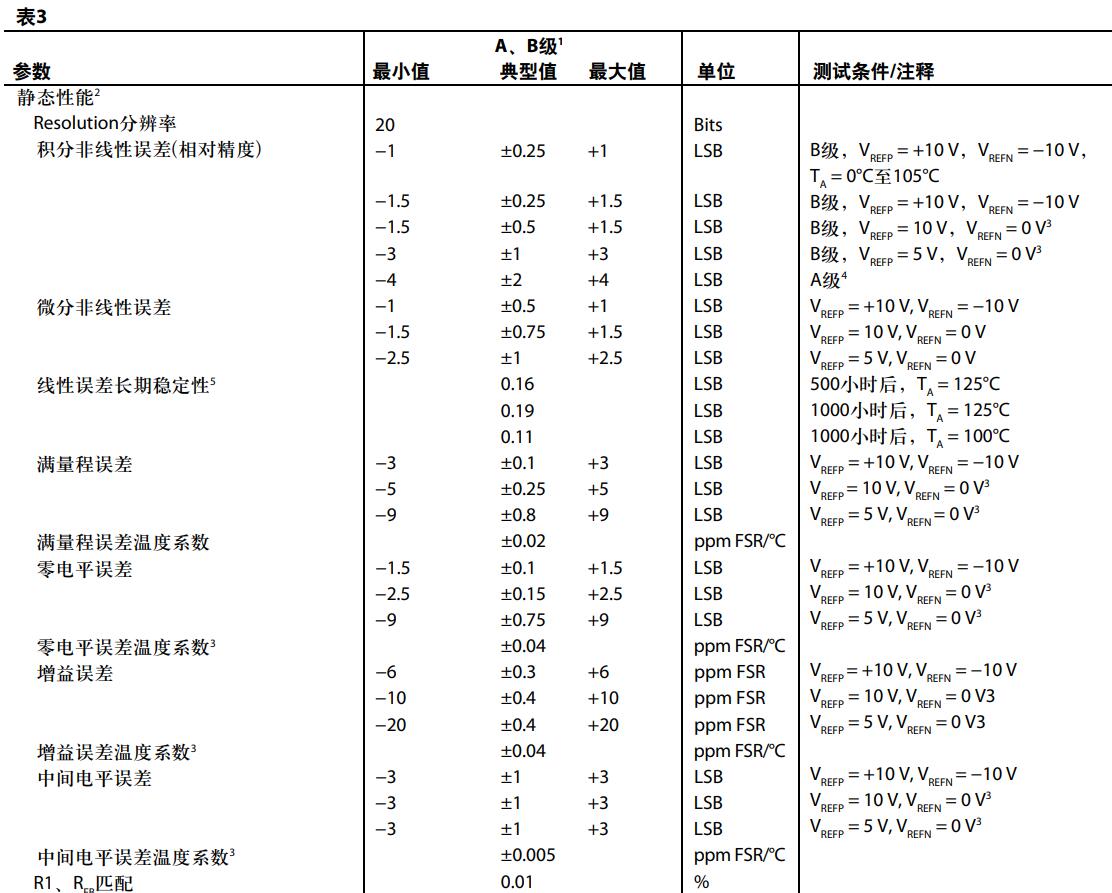

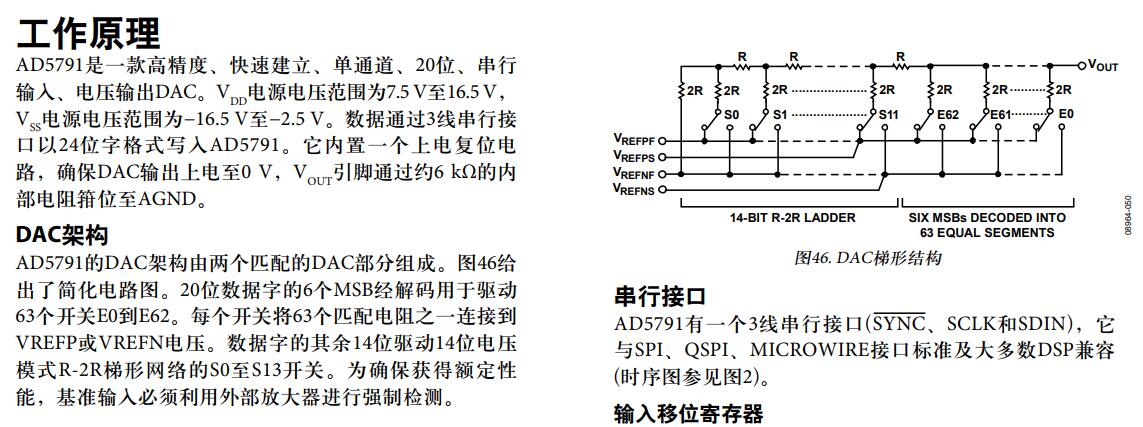

比如ADI公司生产的20位电压输出型DAC-AD5791,其各项误差指标均达到了哈人的水平。AD5791是R2R型DAC,这需要在芯片内部实现极高精度的电阻值匹配,才能做出指标这么哈人的DAC。。。

那么,价格呢?其实也不贵,不至于让人死心,也就50美刀。不过最大的问题是,它缺货。。

在2022年全球半导体产业大缺货的大环境下,不知道ADI是真排不到生产线还是没有客户有这个需求,ADI不产了。。。(好吧其实它不缺货我也买不起)

不过好在我们有Alternate Choice。20位DAC弄不到,可以弄18位的嘛。

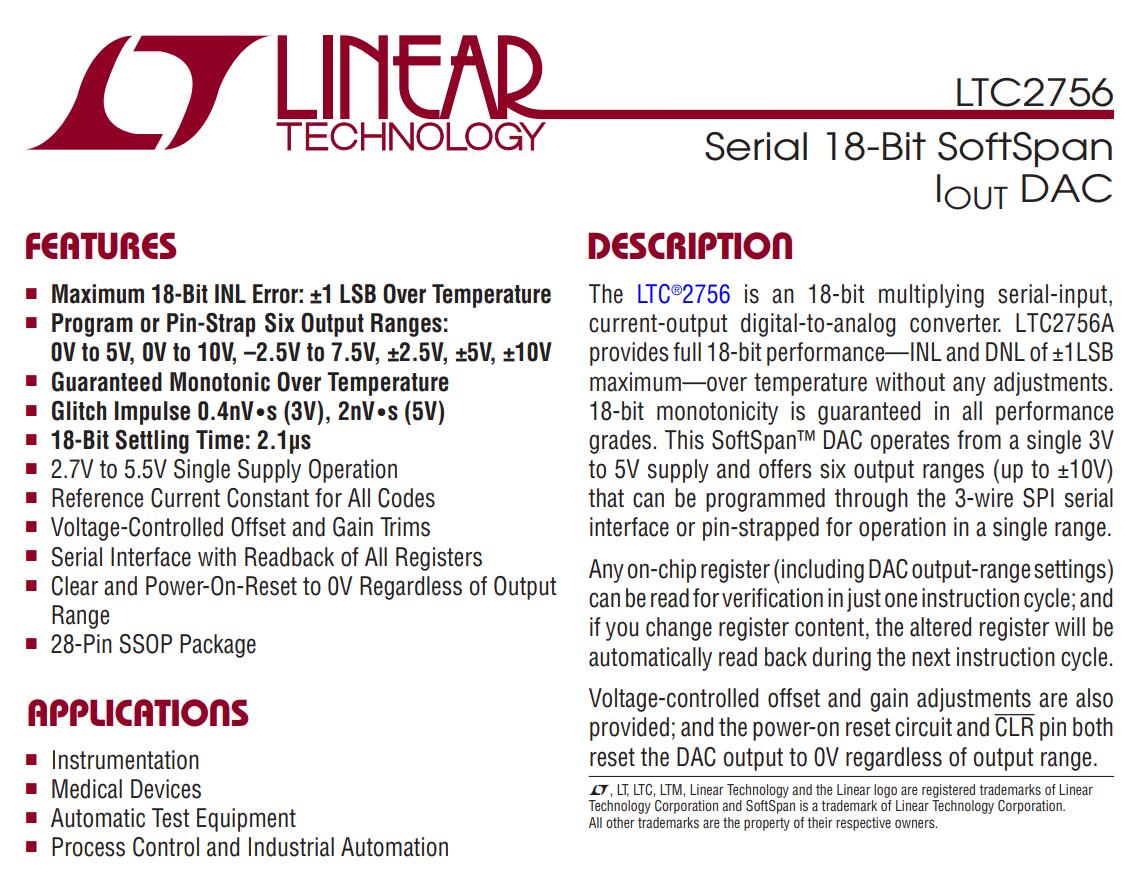

LTC2756-18位DAC

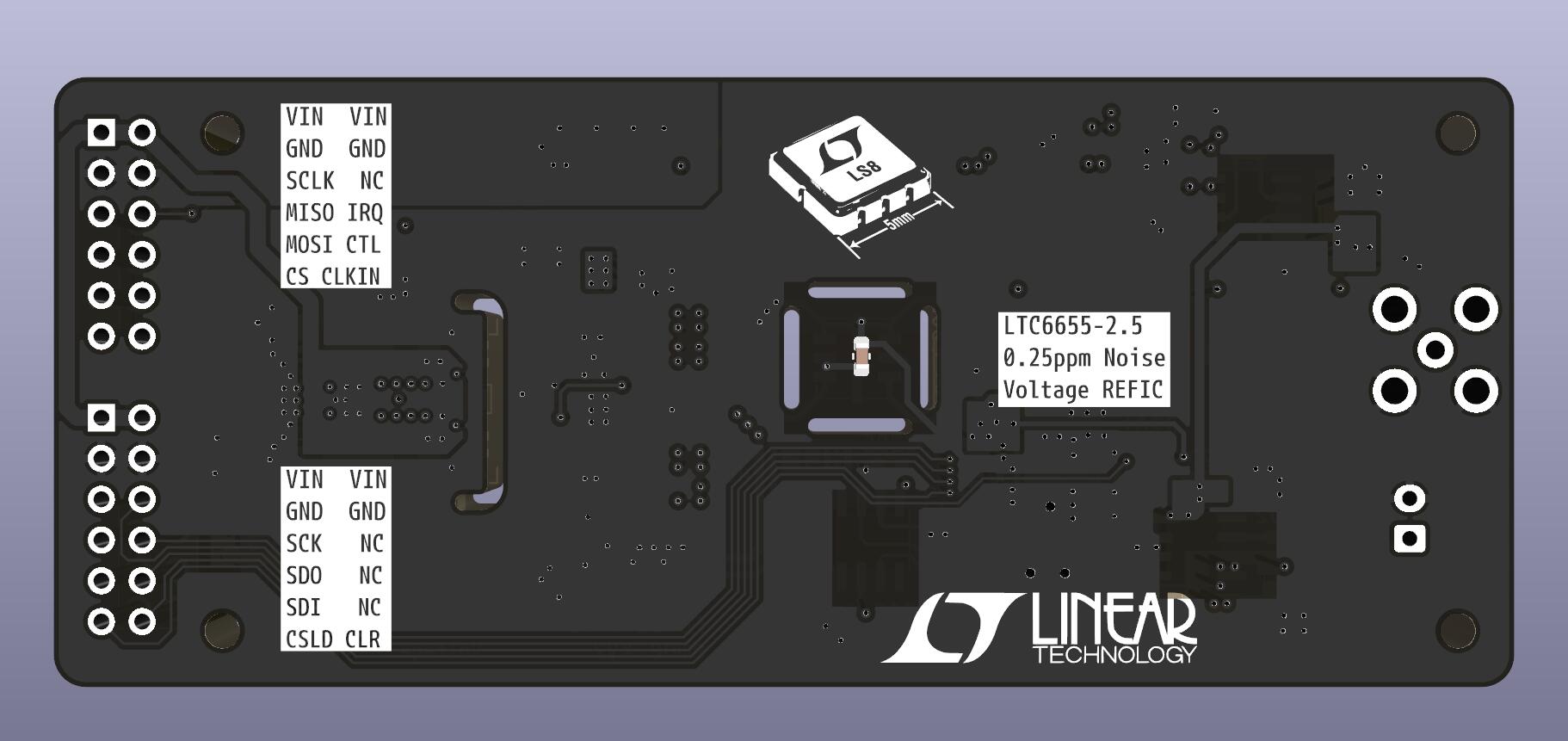

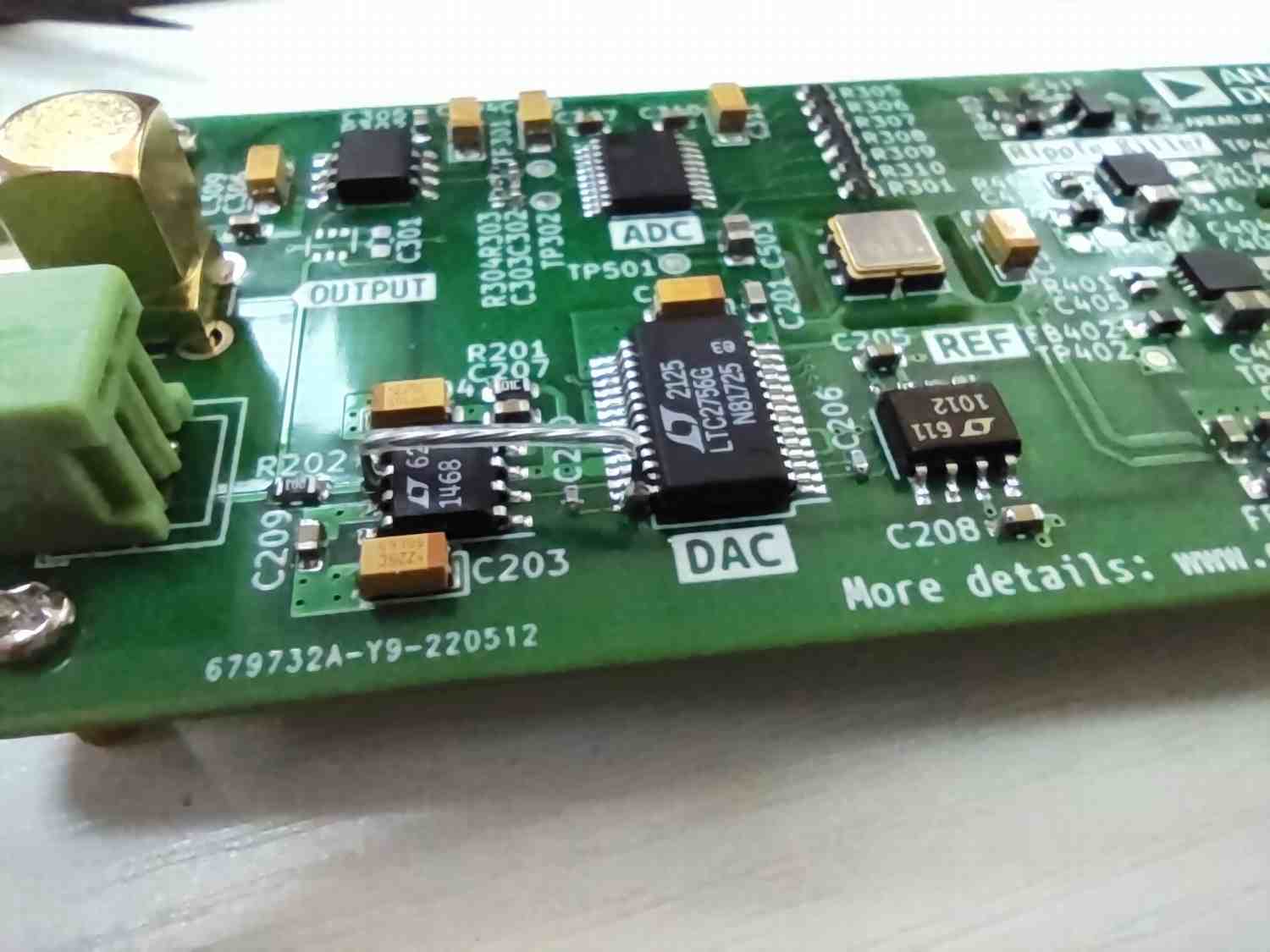

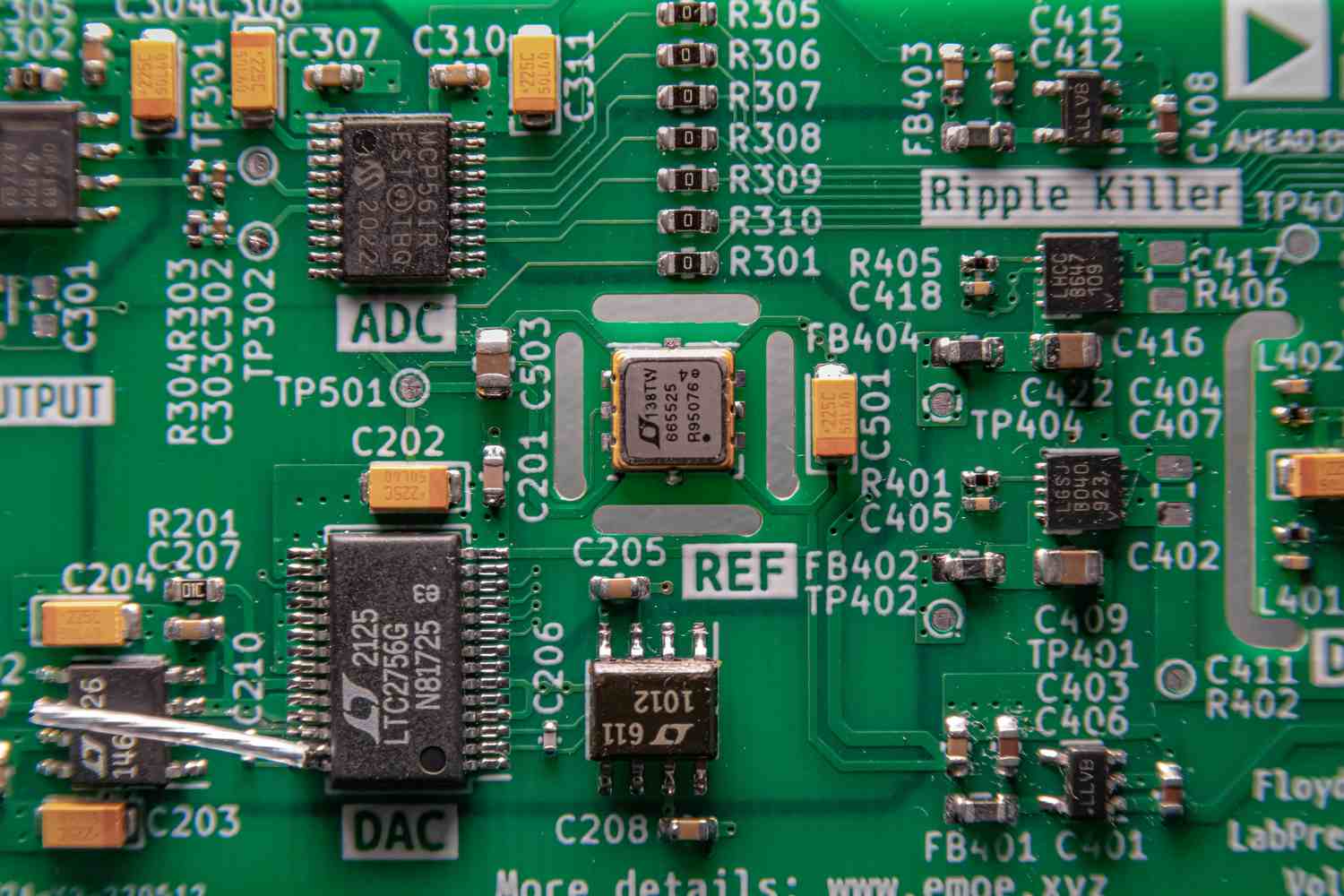

上次在ADI申请样片申请了一片LTC2756,以及2片电压基准源-LTC6655-2.5-LS8。我想这个组合刚好用来做精密电压源~

虽然没有5791那么高的分辨率和辣么低的非线性误差,LTC2756性能也不差,至少拉出来市面上没几个能打的。

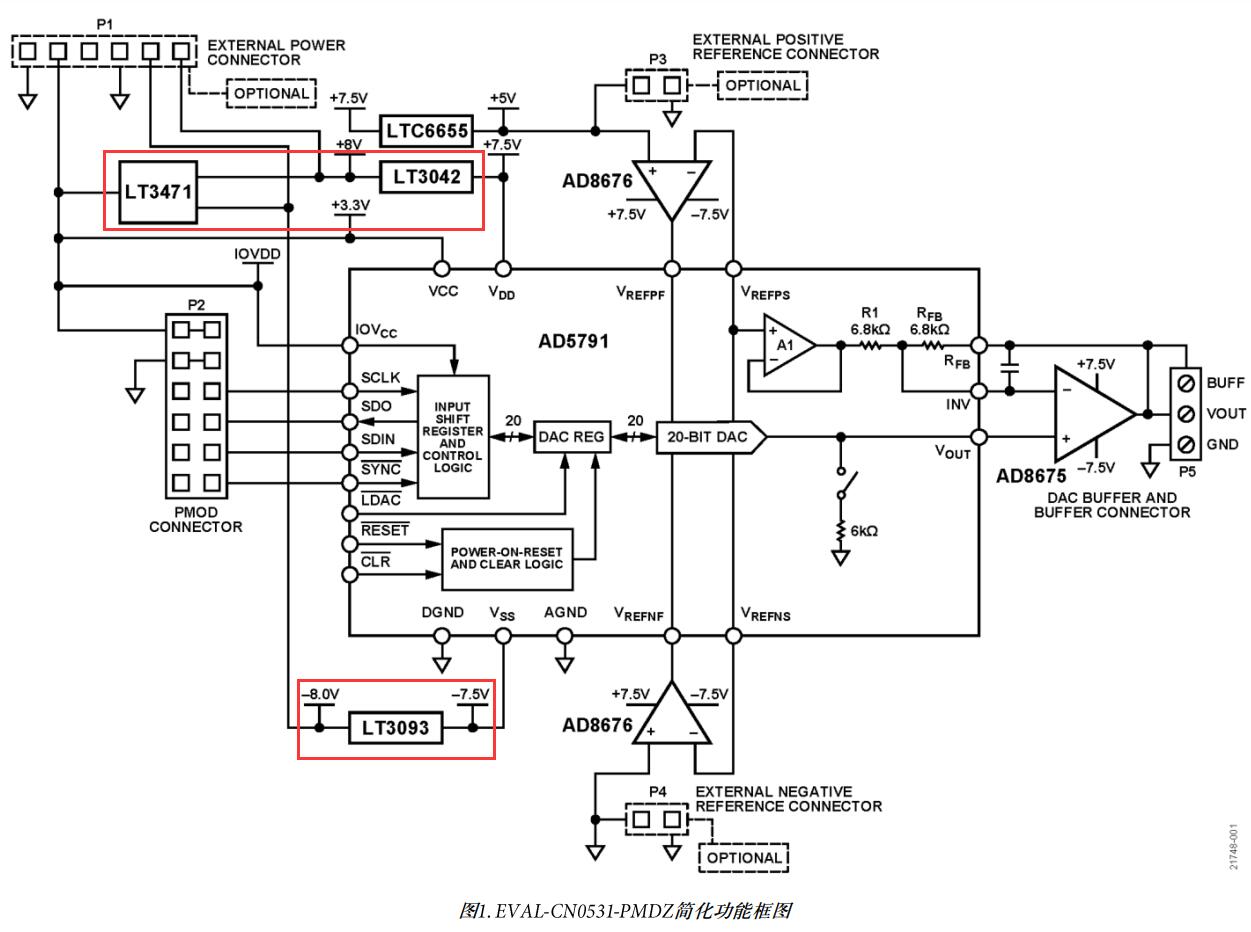

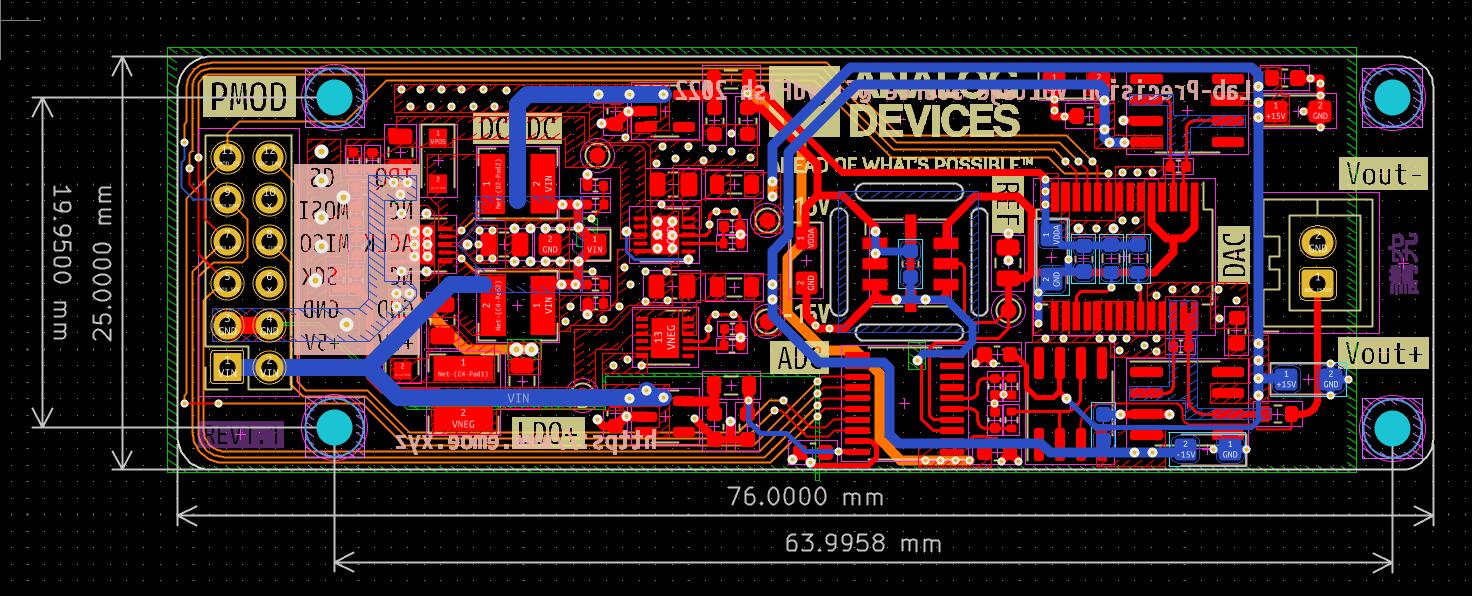

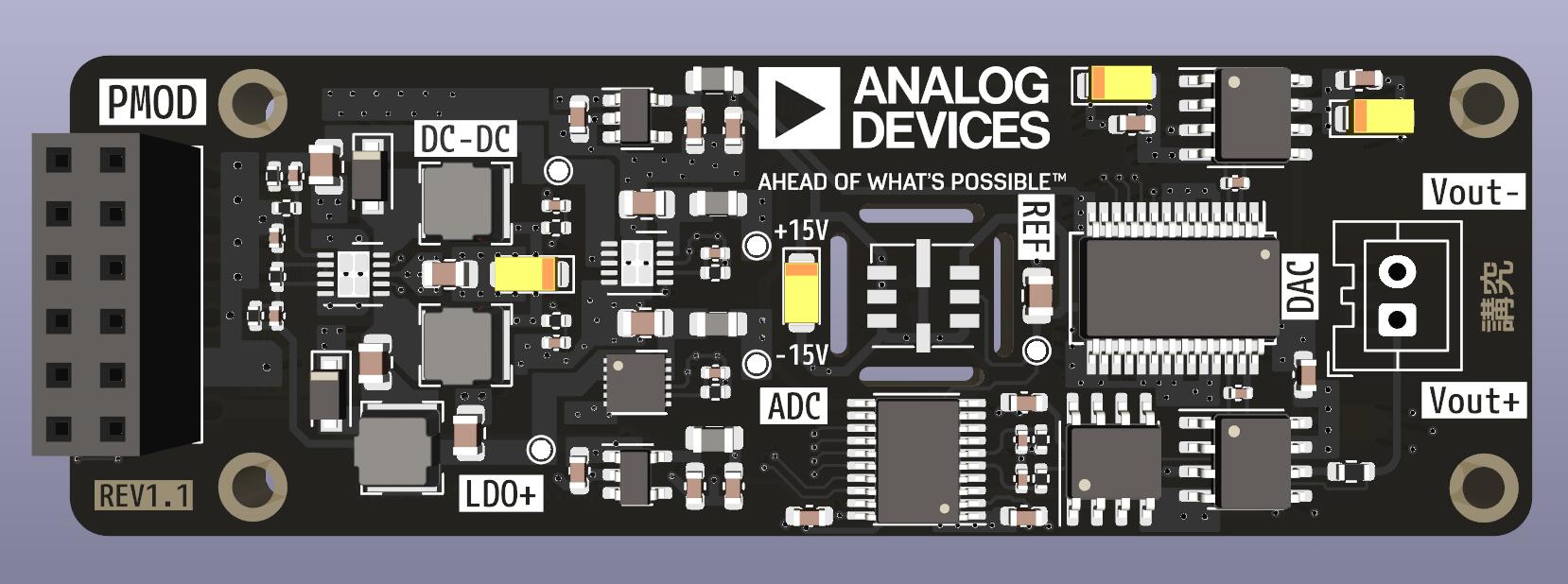

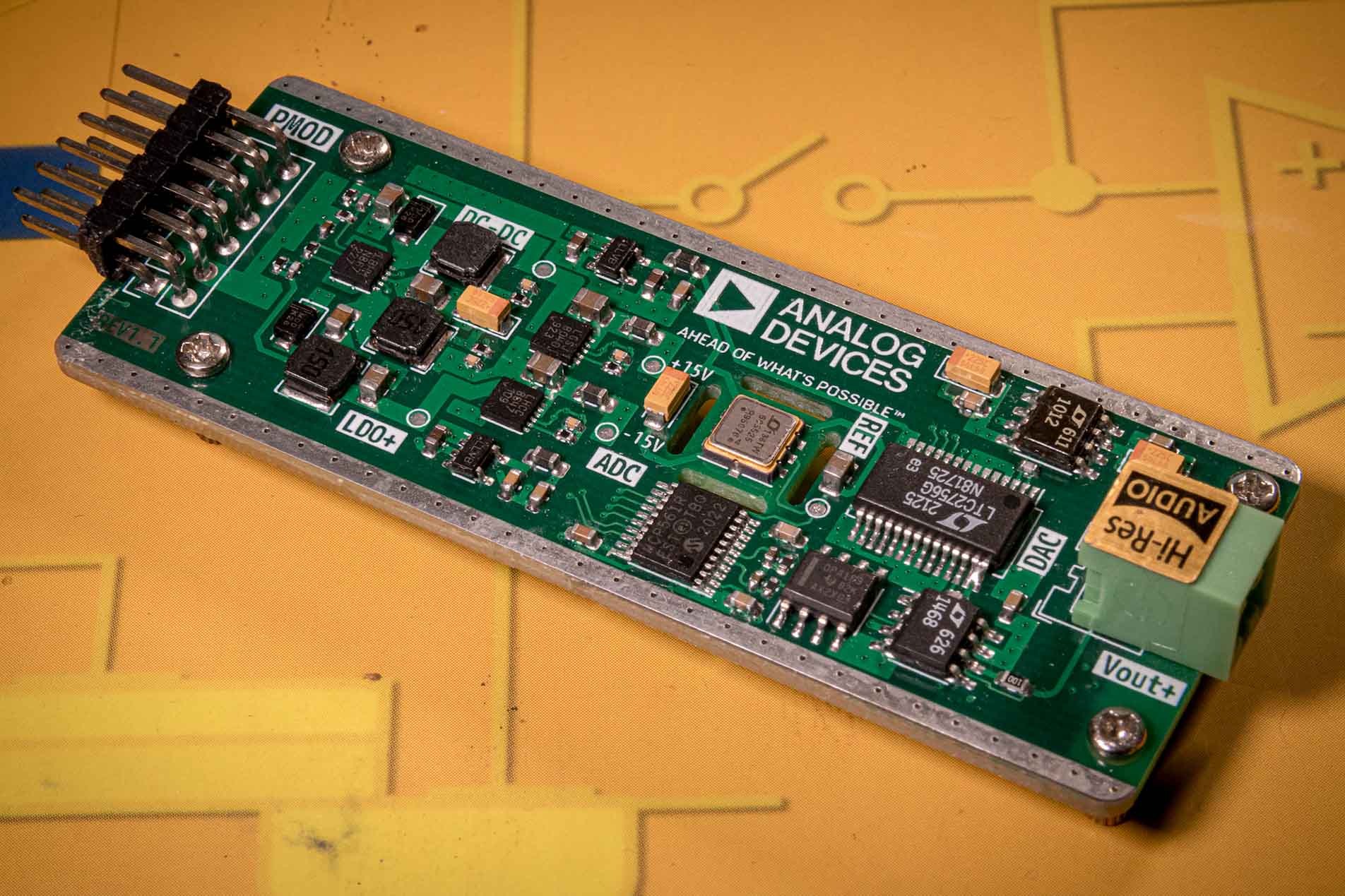

于是我打算用LTC2756和LTC6655-2.5设计一版精密电压源。参考了一下AD5791的应用,以及CN-0531参考设计,我决定使用我之前设计的 精密低噪声电源 作为这次的精密电压源的模拟部分供电。具体的就是图中红框框出来的部分啦。LT3471是双路DC-DC转换器,设计一路Boost和一路反压拓扑,将3.3V至5V的输入电压转换为正负16V的输出。LT3042/LT3093是具有超高PSRR和超低噪声的正负LDO,具有200mA输出能力,完全足够我们使用。在这里我设置2个LDO工作输出±15V,作为运算放大器的供电。

然后我还为这个电压源设计了一个24位的Sigma-Delta ADC-MCP3561来实现闭环检测,我预想的是使用闭环检测和某种抖动算法来让DAC实现更高的有效位数,不过算法我还没想好怎么实现。

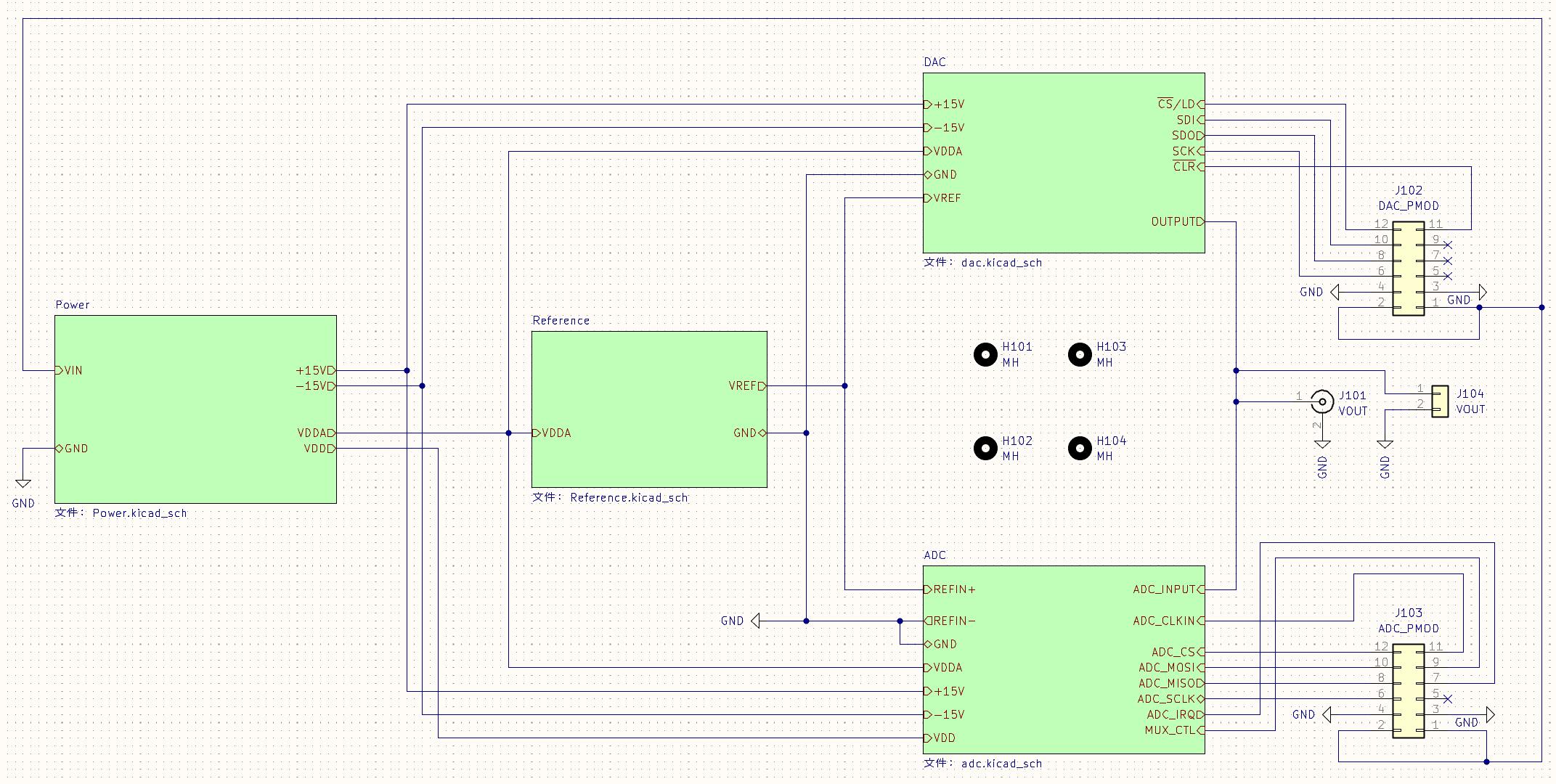

然后ADC和DAC的供电也需要区分模拟与数字,我用了2个LDO,同时模拟部分的LDO也负责给基准源-LTC6655供电。电路的顶层模块如下:

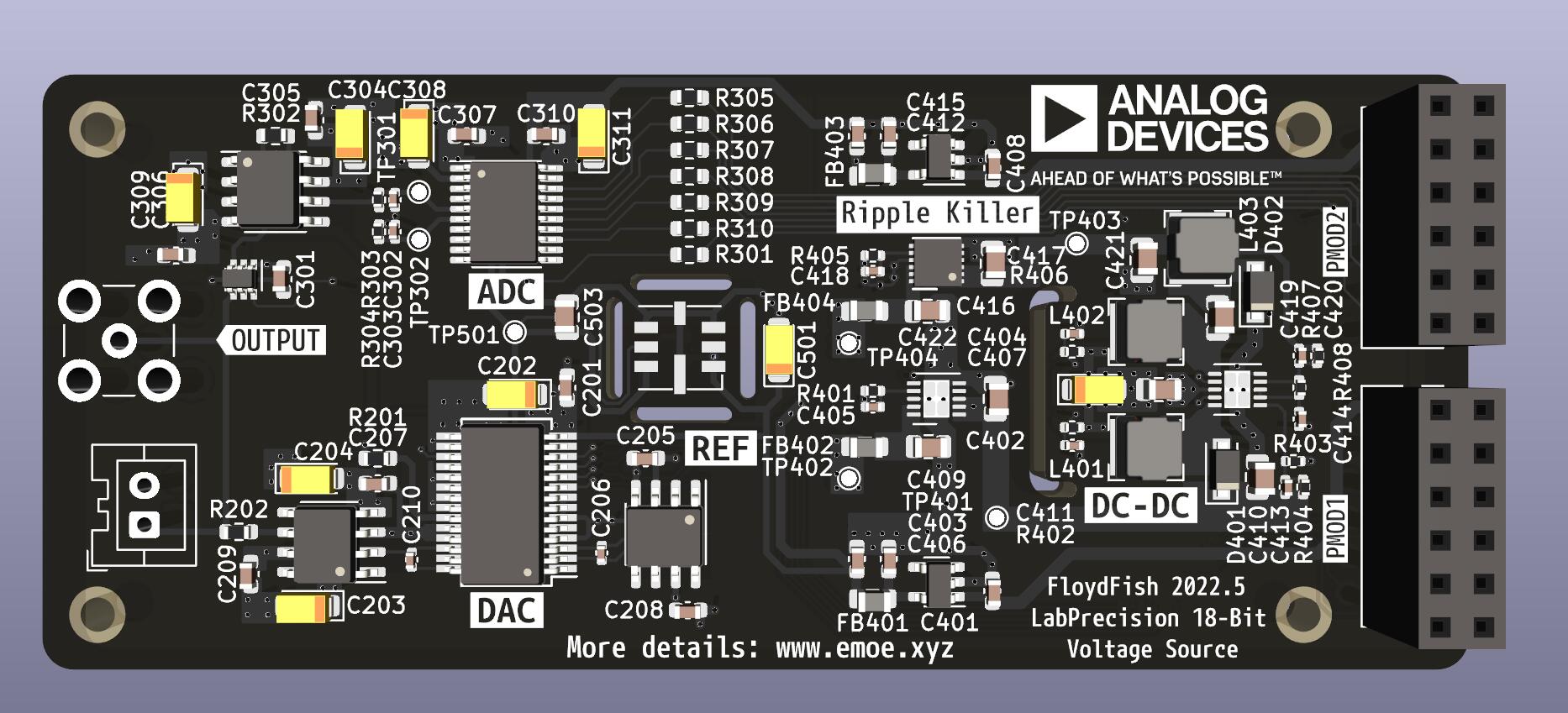

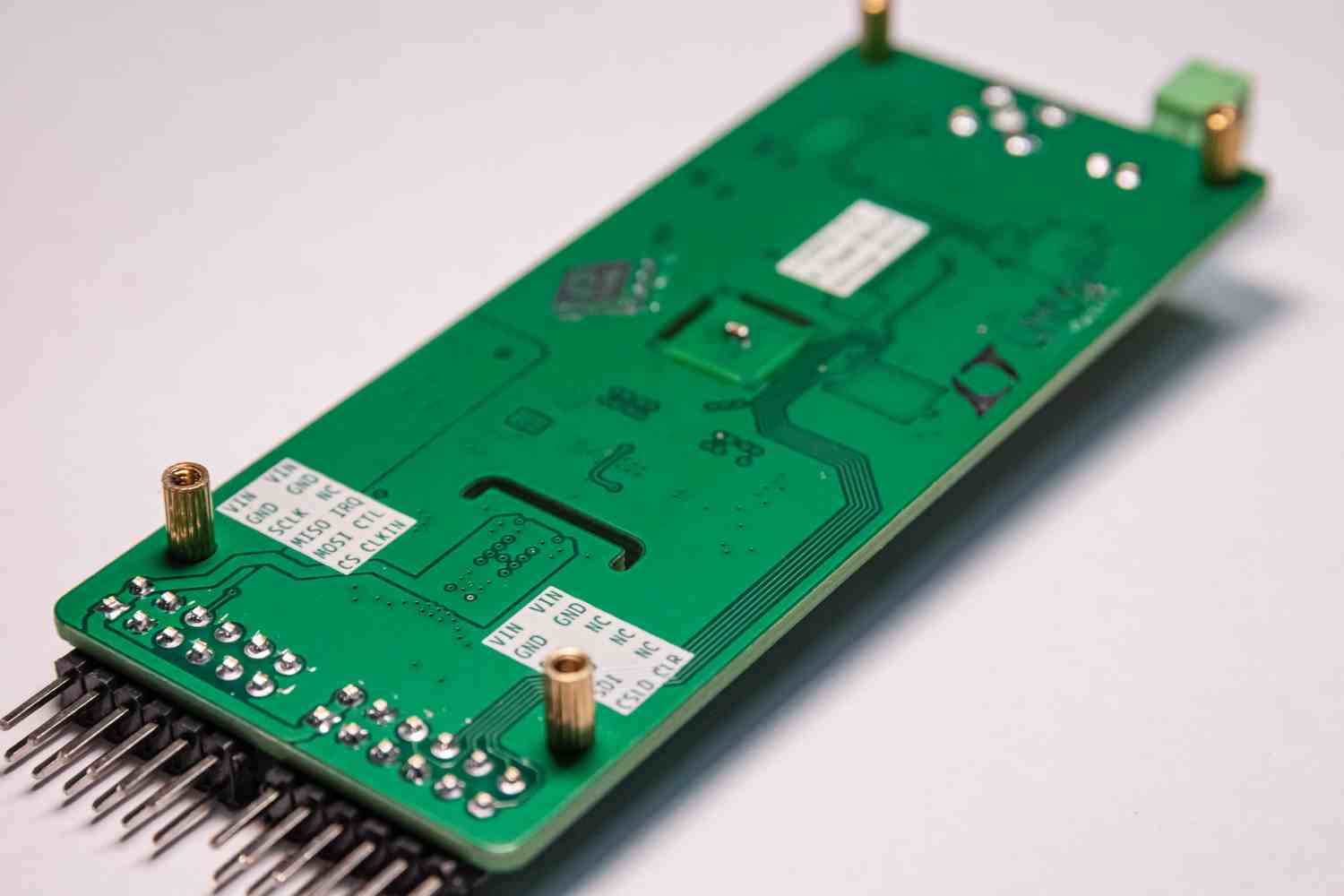

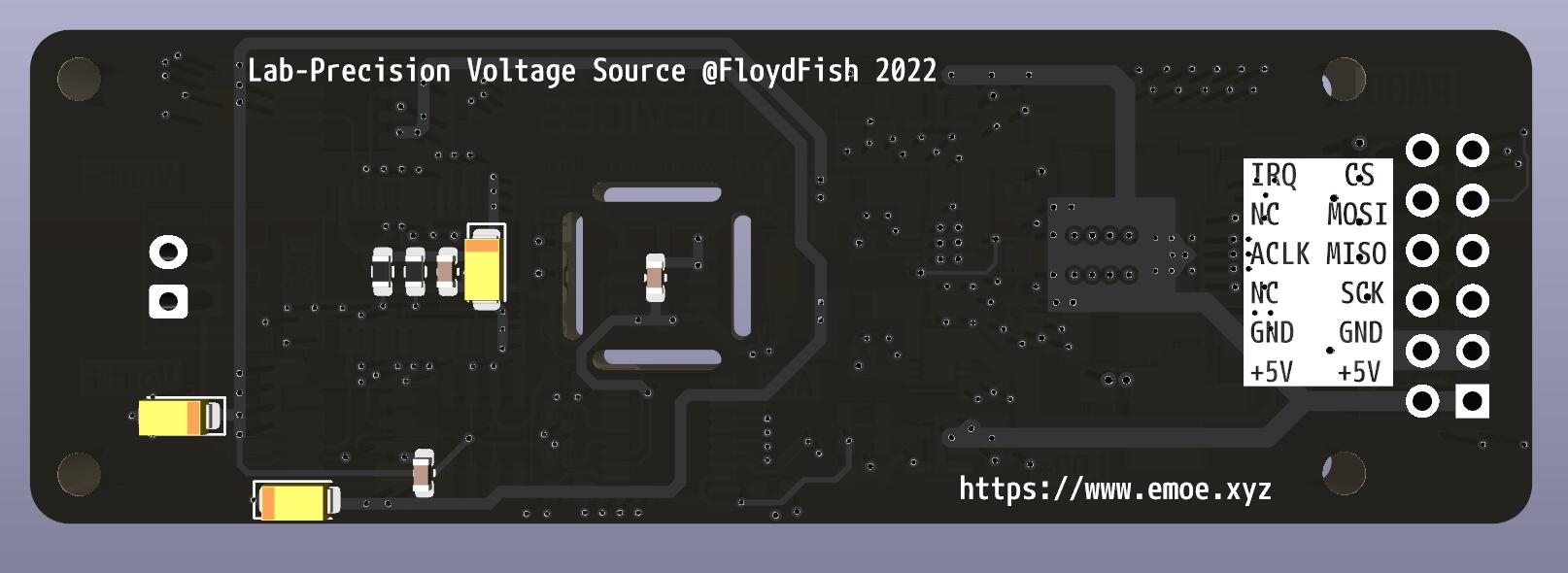

数字和供电接口用了2个PMOD接口(第一次用,想试试)。PCB渲染图如下:

然后一点实物图与测试图:

焊接精密低噪声电源

果然第一版都难逃设计bug的噩运…

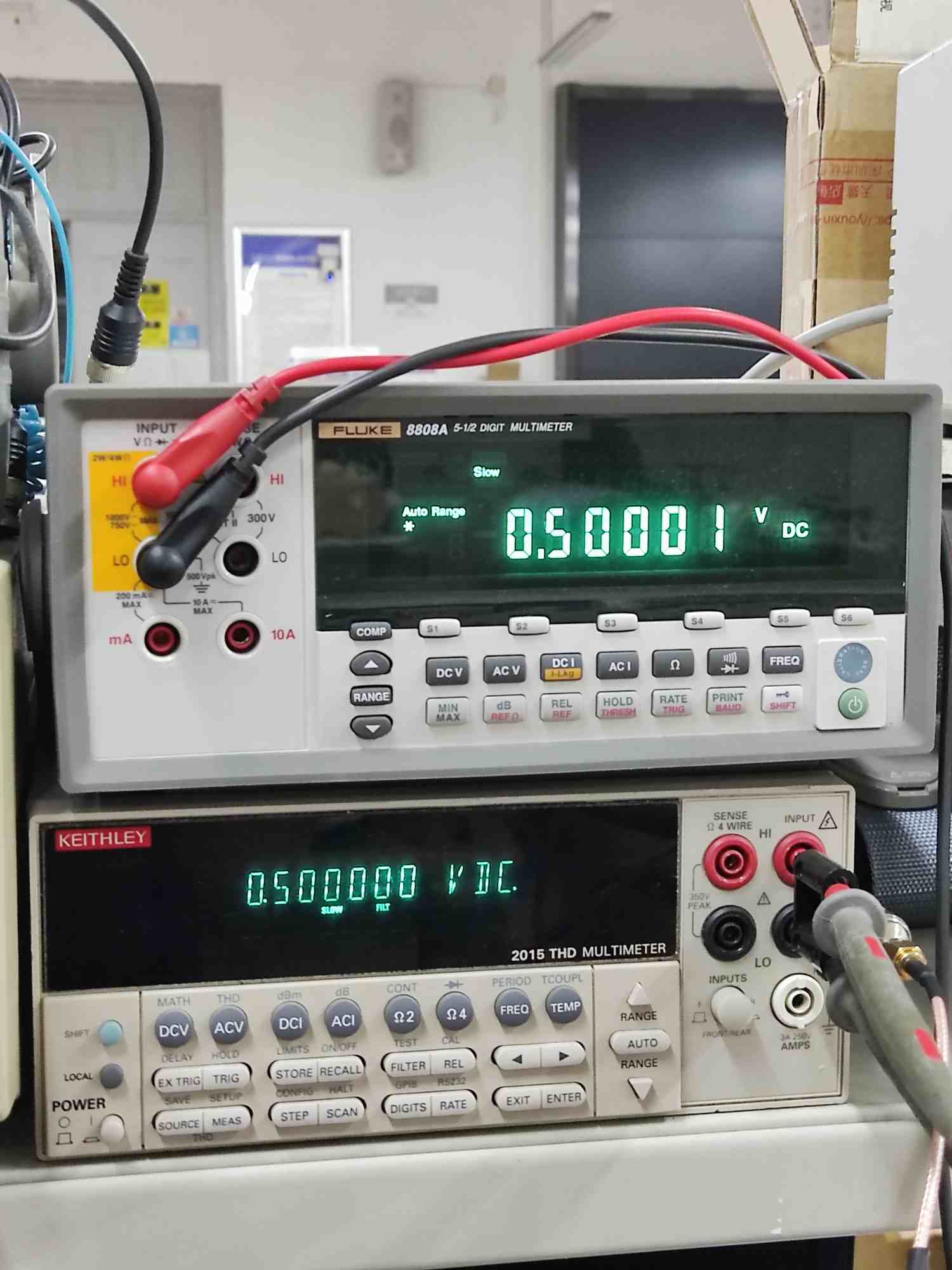

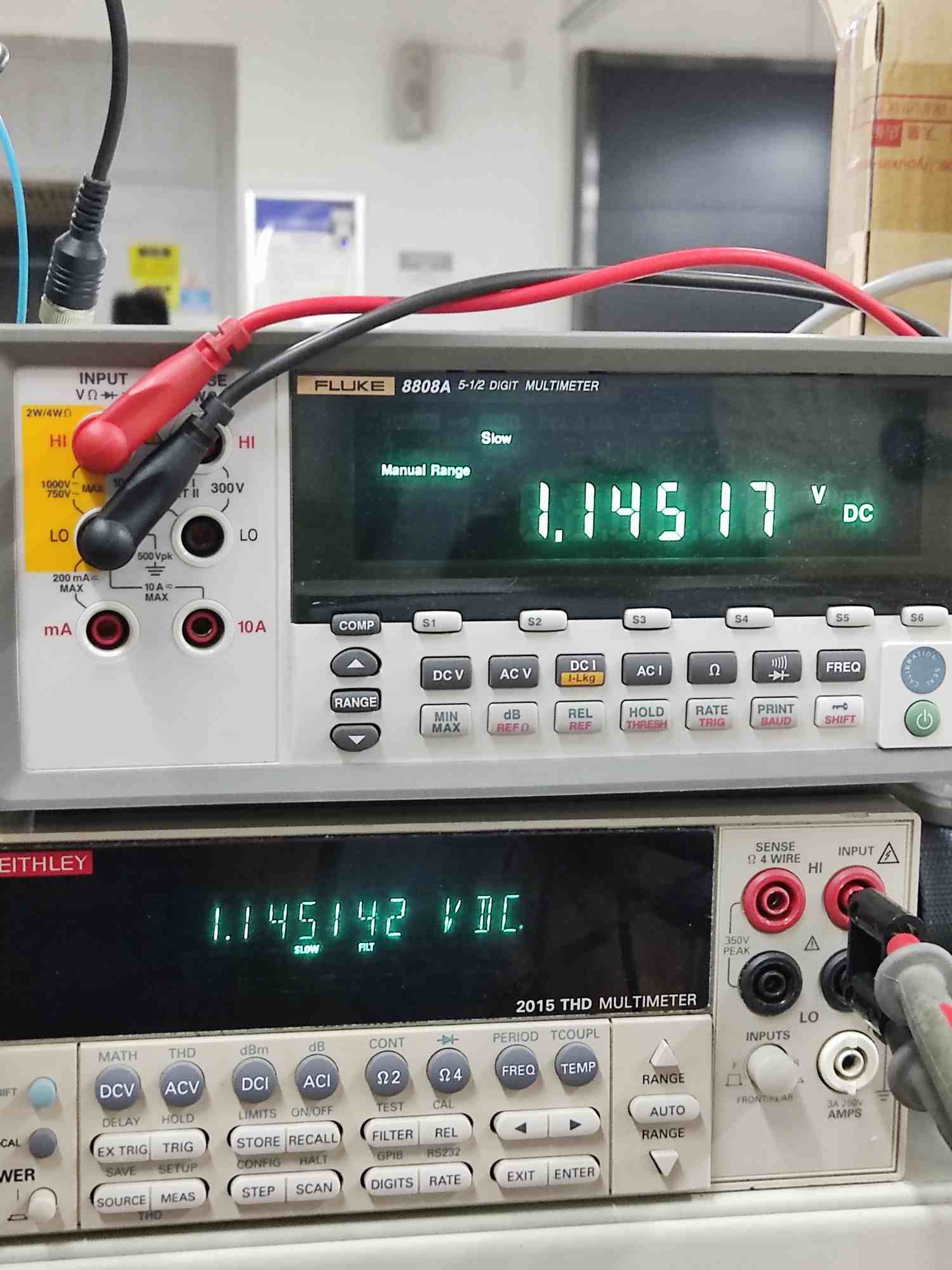

使用5位半(上)和6位半(下)输出0.5V测试

臭臭的电压-口区

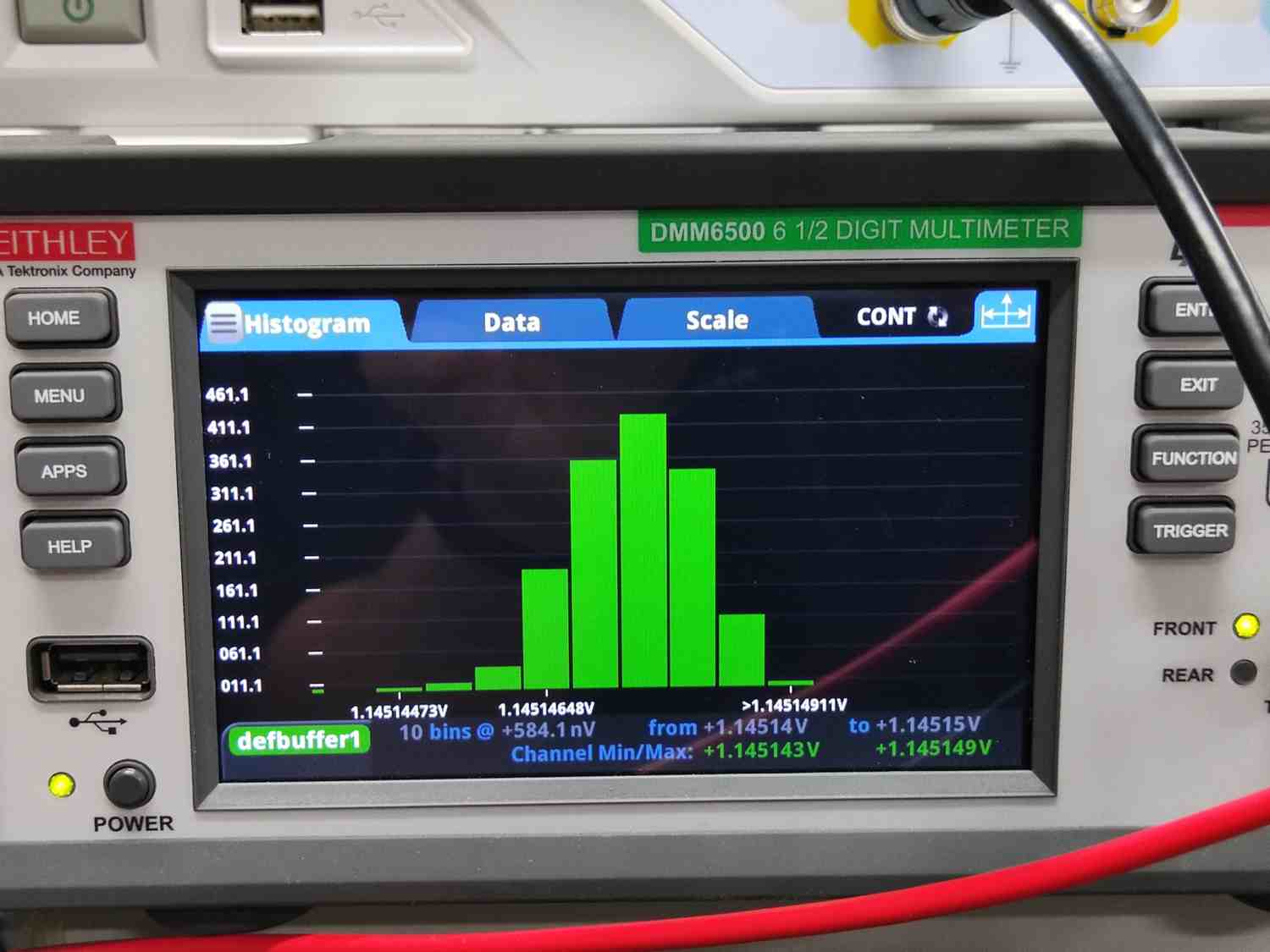

用完CNPP的表,又跑去楼下实验室蹭6位半的吉时利DMM6500用

使用DMM6500的直方图统计功能,有些漂是因为没有做密封外壳,同时有些机械振动,可以看出,稳如老狗。

然后是我用相机拍的一些电子涩图。

金封的LTC6655真好看啊。

不过我做完了这版还不满意,我想把他装进一个小盒子里,用锂电池供电,用编码器调节参数,同时有显示器能显示参数。所以我做了Rev 1.1,目的是缩小PCB体积,同时将PMOD整合到一个接口上去。

嗯,PCB面积相较于上一版缩小了约50%,但是没地方放logo了……..(sad。)

板子还没打样,做完了我会把所有设计文件和软件扔到github上。

后续

后续是填坑啦。当然,我可能还需要使用高位数字万用表(比如HP 3458A,不过显然我是没有的)去标定我的电压基准源,同时测试这个精密电压源的各项指标性能,看看他达到了datasheet中的标称性能没有。

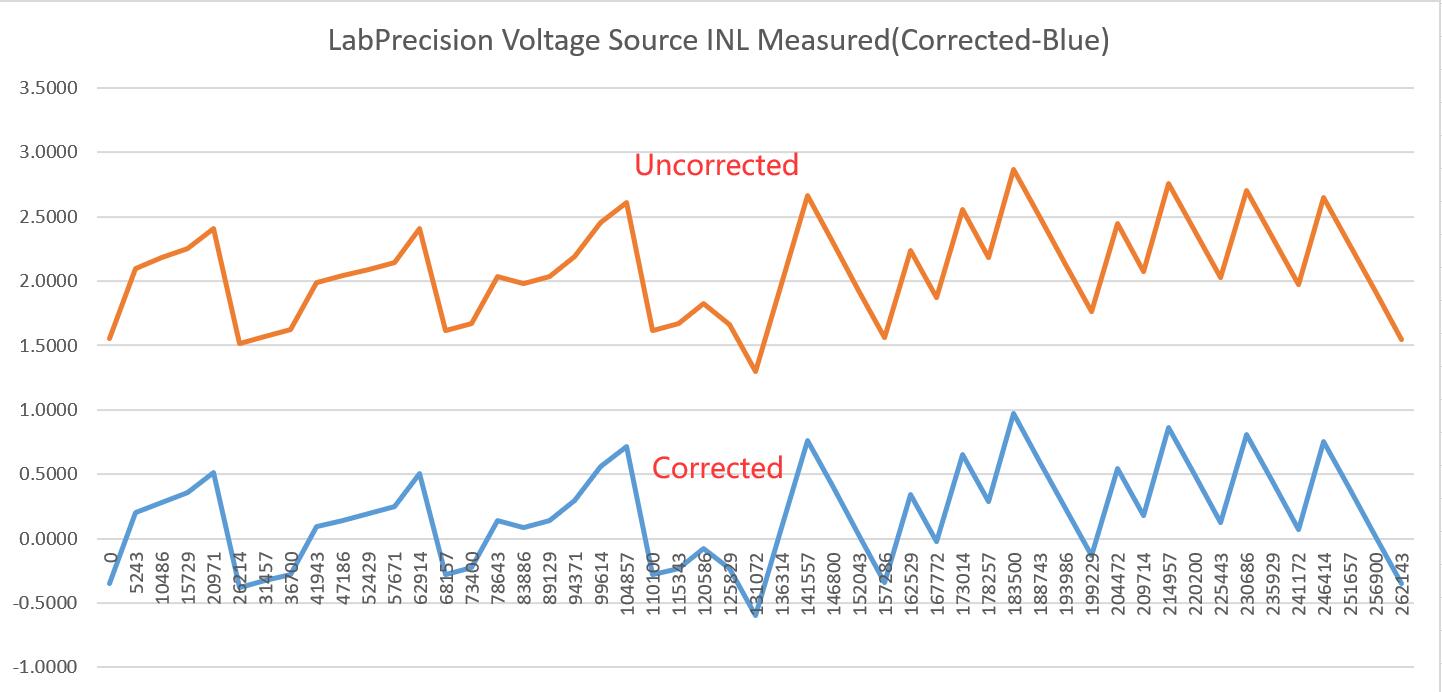

2023-6 积分非线性度测量

🐟现在手头有一台Keithley 2015 6位半DMM,于是可以试着粗略测试一下这个板子的指标了~

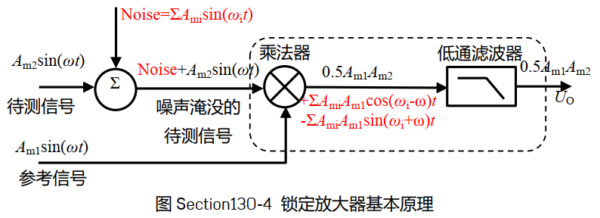

我们来测试一下LTC2756的积分非线性度(INL)。测量步骤和计算公式参考MAXIM的应用手册—— AN4159:Measuring the Linearity of Differential-Output,Current-Mode Digital-to-Analog Converters (DACs)

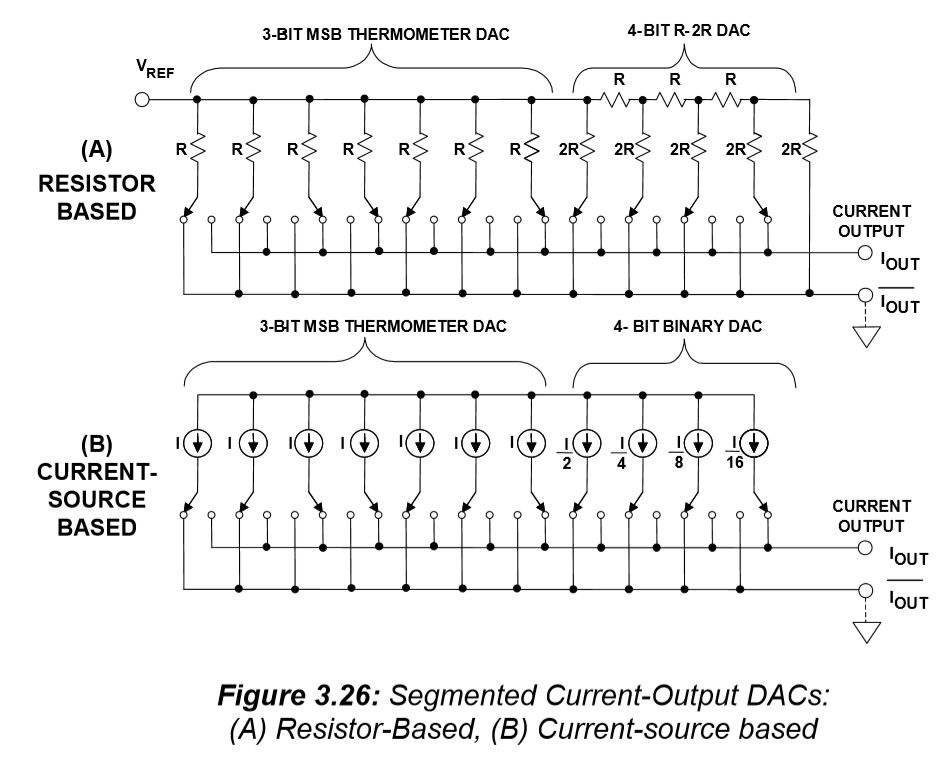

MAXIM的Application Note中,测试的DAC器件是一个分段加权式二进制DAC(Segmented Binary weighted DAC),他用了一些技巧,取了很少的测试点就实现了全码值的性能评估分析。

分段式电压DAC,将多个DAC级联拼凑成一个DAC,可以实现分辨率的叠加,同时降低设计和生产制造的难度。

二进制加权电流型DAC,3-bit MSB和4-bit LSB拼接起来可以得到一个7-bit DAC。

MAXIM分别取了各级权重的电流源开启,其他电流源关断的工况测试,然后利用这些单独的电流源开启所测得的数据可以通过加减不同的bit来得出完整的DAC传输曲线。这种测试方法要求DAC的内部结构已知(需要知道分段的各段落DAC的位数及权重)。然而LTC2756却是个蒙面人,我们无法从datasheet中得知其内部结构。

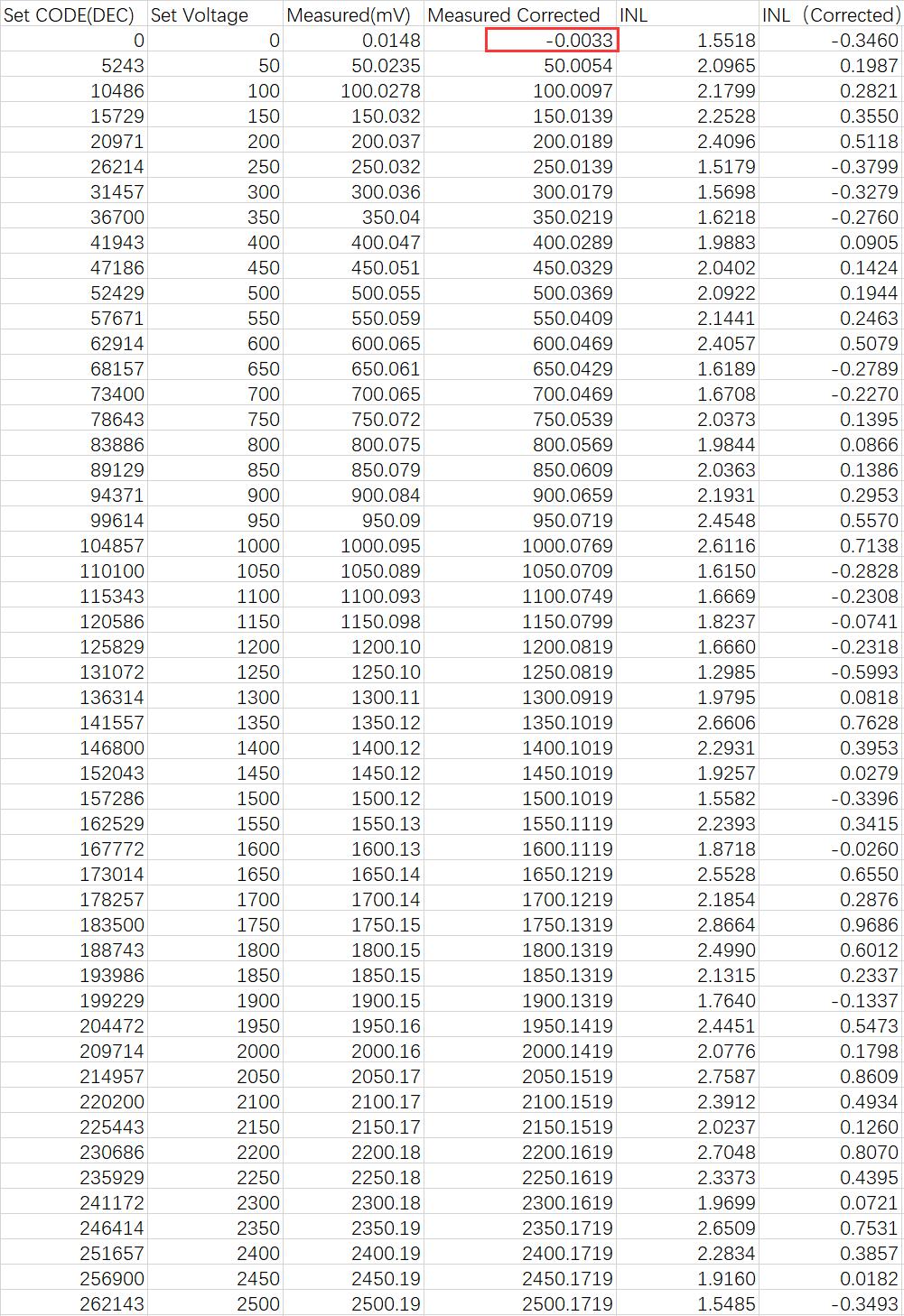

在不知道其内部结构的情况下,采用上述简略的测试方法去测量几个特定的工作点,然后通过这些点计算得出完整的DAC传输曲线是无法实现的(除非瞎猫碰上死耗子…)。我们现在想要对2756进行完整测试,只能去大量取点测量。按理来说,通过VISA编程DMM(数字万用表),并通过脚本控制DAC连续输出值,然后用PC自动收集数据,可以完成无人值守的自动测量。可惜🐟现在对Python还不是特别熟悉,完整的测量待我学学Python之后再来整…现阶段我们先简化一下,间隔50mV取一个测试点,在2500mV内共测试51个点,然后粗略评估一下INL和DNL。

在输出满量程内(2.5V),间隔50mV取一个测试点,对DAC输出电压进行测量。在计算CODE值时,假设VREF电压为理想值2.50000V(实测LTC6655LS8-2.5的输出为2.50008V)。

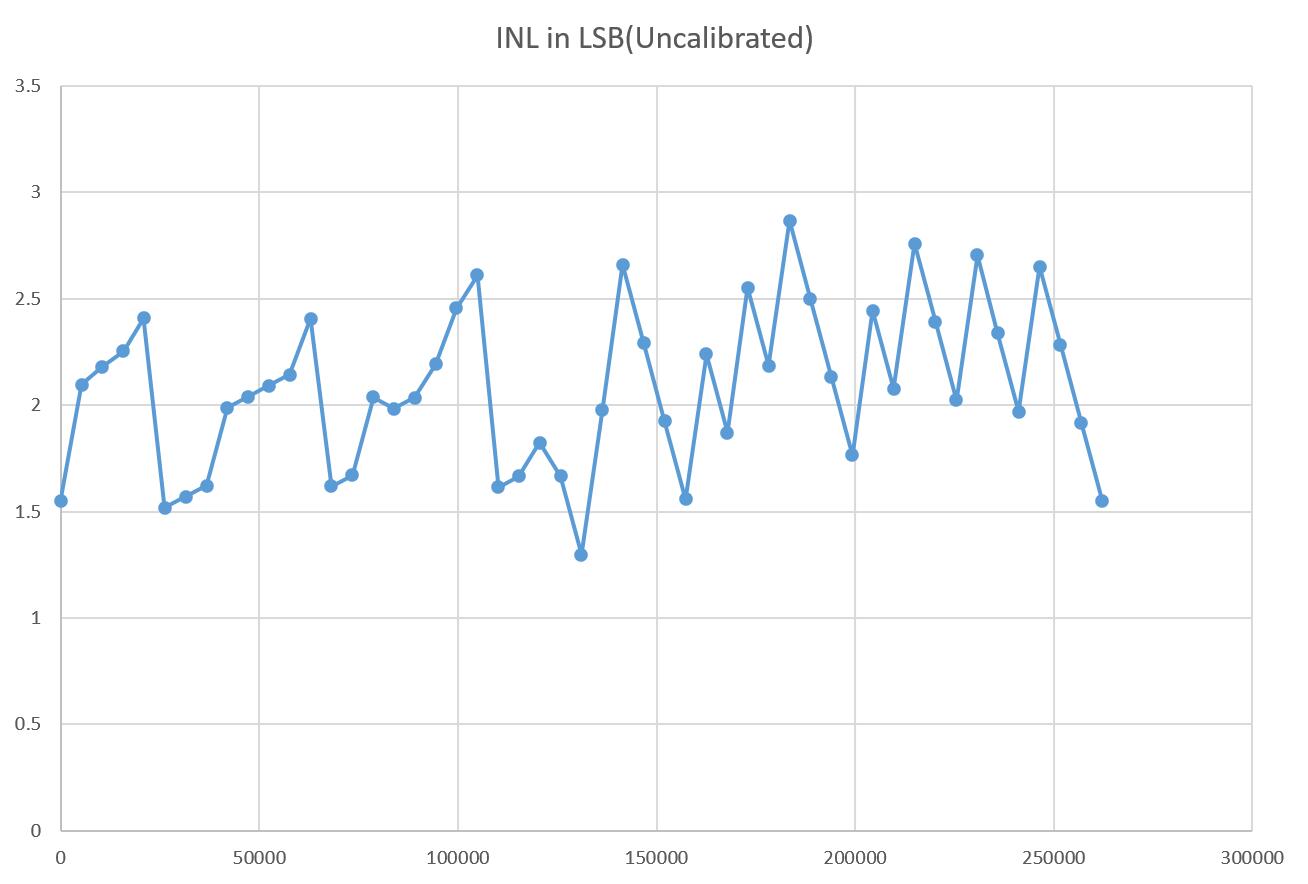

未校准offset和gain测量的INL

测得输出后,依照 End-Point Method 用最大值和最小值计算V_{LSB},然后根据此值计算各点处的积分非线性度,计算出INL。计算过程如下:

V_{LSB} = (V(0X3FFFF)-V(0X00000))(2^{18}-1) \\

=(2500.19-0.0148)/262143=9.537448 \ (uV)对于任意一代码点,记码值为CODE,此点测得的输出电压为 V_{code},那么此点的INL如下:

INL_{code}=[V_{code}-(CODE*V_{LSB})]/V_{LSB}依据上述公式在EXCEL中绘制折线图,画出DAC的传输函数曲线和INL曲线如下:

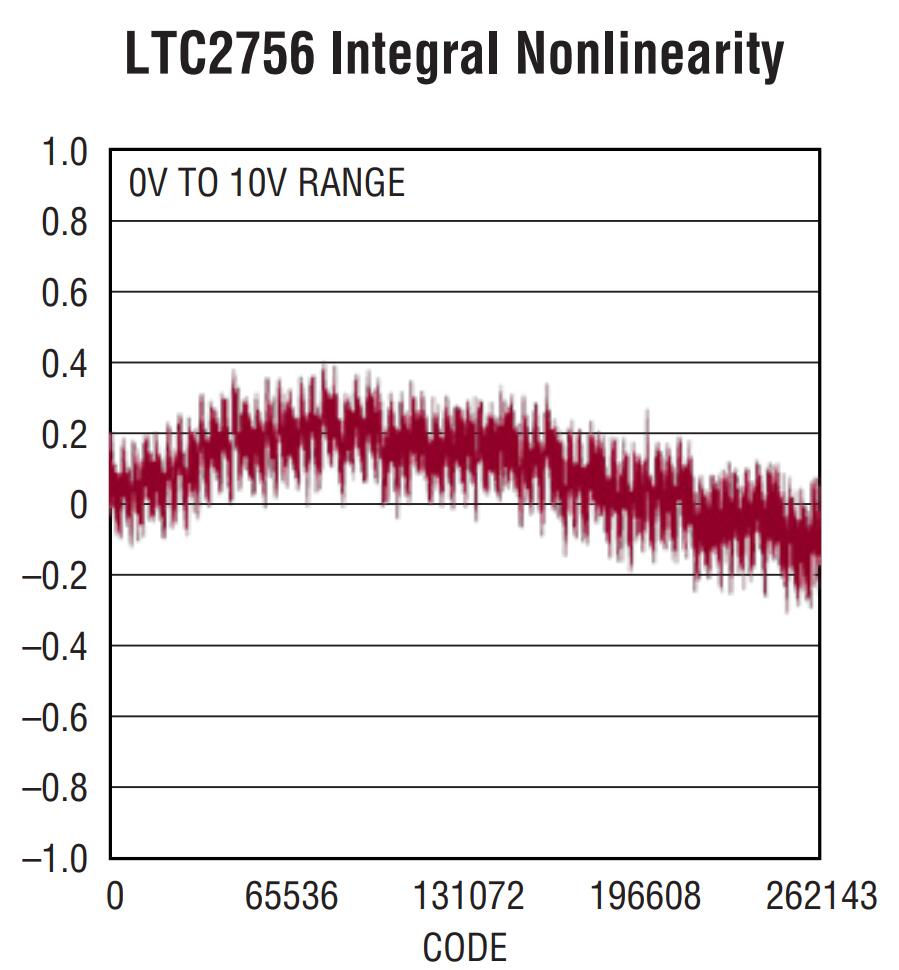

然而LTC2756的手册中标出的INL曲线如下:

Well,我们可以看出,这个INL似乎有点大。

Calibrate before calculation!

经过前辈的指点,在这篇 Technical Article中,介绍到在测试ADC/DAC的INL和DNL之前,必须先将静态offset和gain error给校准掉,而且通常这个校准通过软件完成,所以我上面绘制的INL折线图可以说是无效的。

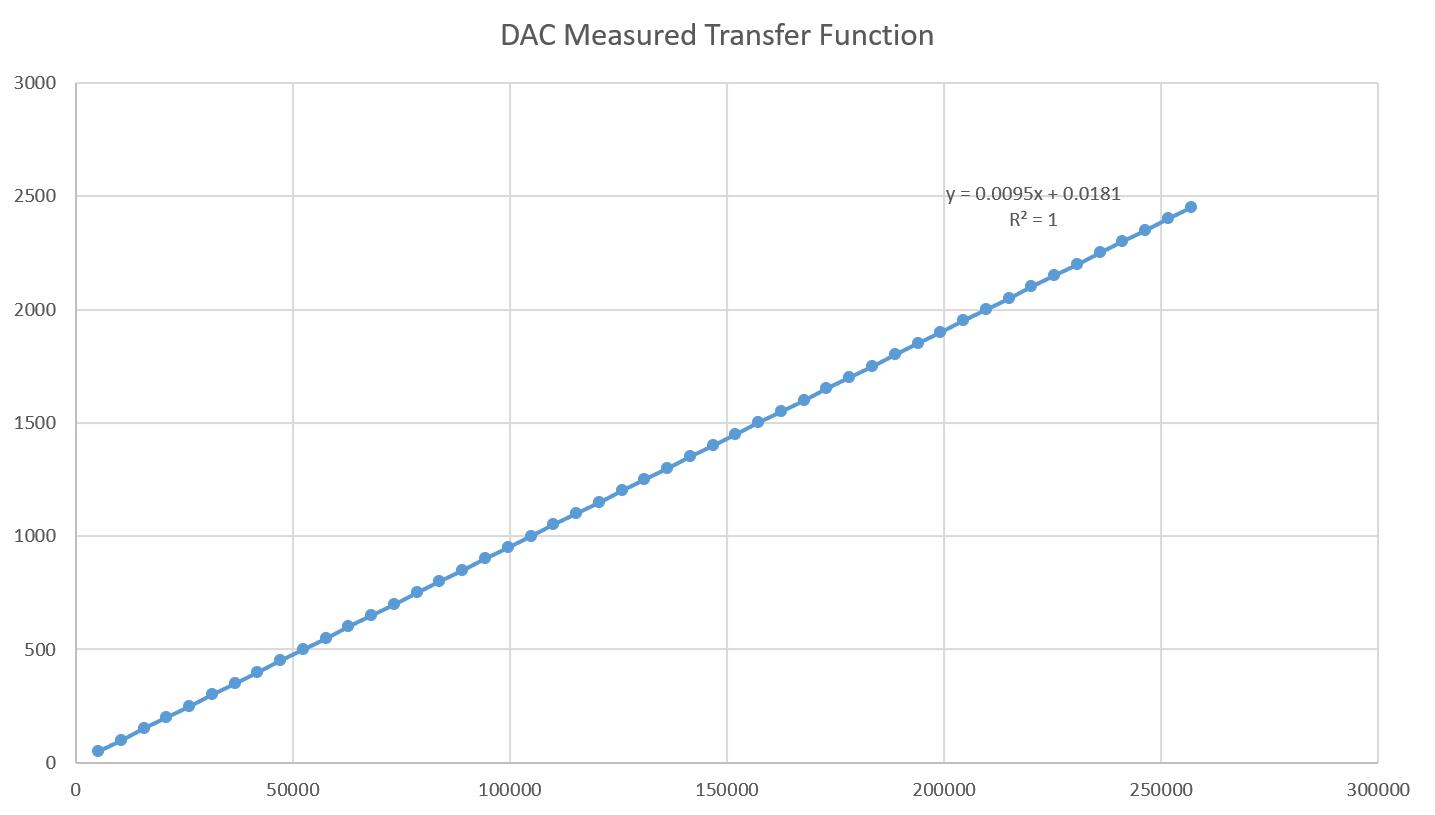

将原始测量数据复制一份,画出数据的散点图,然后去掉第一个数据和最后一个数据,用剩下的数据做线性拟合曲线,得到DAC的拟合传输函数如下:

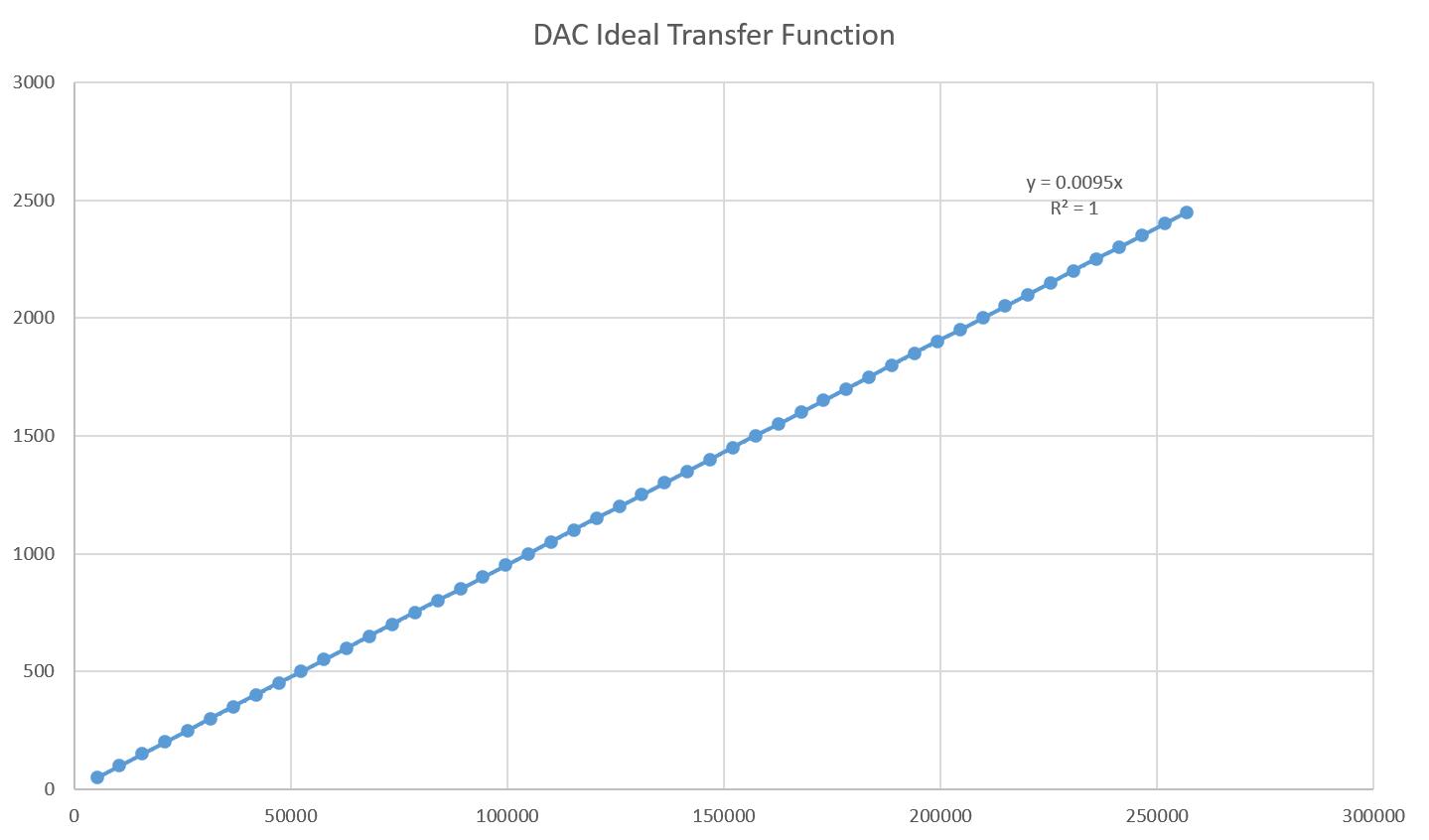

然后再选取理想的DAC输出电压列,画出散点图,拟合出理想的DAC传输函数:

通过拟合的曲线表达式可以看出,实际测量的曲线斜率和理想曲线的斜率完全一致,这说明DAC的增益几乎没有误差!但是,实际测量的DAC传输函数有着一个常数项(+0.0181),而这个常数项就是我们需要校正掉的静态误差(Offset)。

当然这里不排除一种情况,即Excel拟合出来的传输函数的系数有效位精度不够,实际上两个传输函数曲线存在着非常微弱的差异,但是没有体现出来。另一种可能是,我使用的6位半DMM不足以分辨这细微的Gain error,如果是这样的话那就太痛了:(

绘制INL Cal之前和Cal之后的对比图,可以看到实际上Cal的过程是把INL曲线整体向下搬移了一个offset。因为此处并没有用到增益校准(增益较为理想),所以INL曲线的形状并未发生改变。

可以看到,经过offset校正后的INL曲线被搬移到了约±1.0 LSB的范围之内,算是非常理想的表现了。

此处只是粗略测量了2756的INL性能,如果需要完整地测试,还是需要逐点测量绘制曲线。人工去设置、测量、填写2^18个数据点有点…不太现实,所以还是等🐟拿PyVISA或者LabView写个全自动测试脚本吧~(用于连接DMM的GPIB卡已经有了)

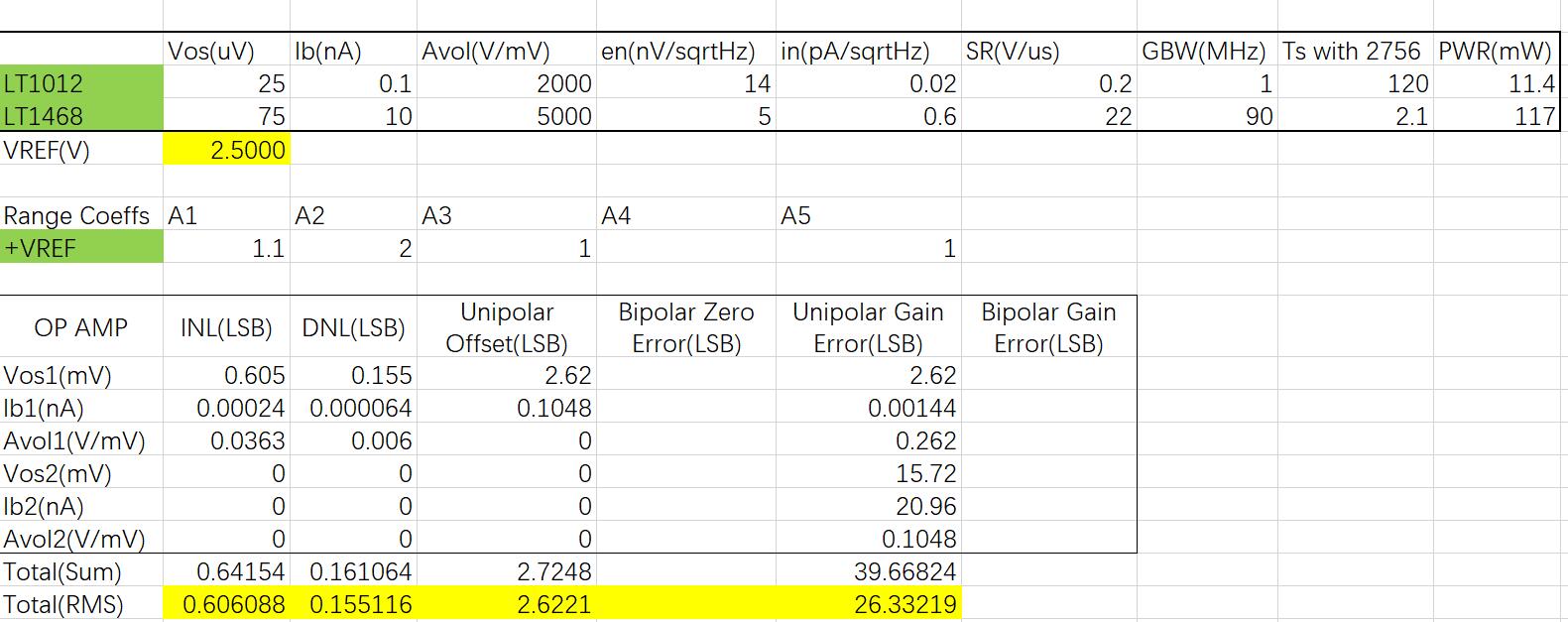

INL误差分析

LT2756的数据手册中提供了一个误差分析表格,非常方便计算(虽然从手册中并未告知计算公式的依据和来源…)。我做了个Excel表格计算器,粗略估算了一下:

唔姆,看来LT1012+LT1468的组合为整个系统带来了约0.6个LSB的INL误差,并且可能有着2.6个LSB的静态offset电压,以及26个LSB的增益误差。(实测发现INL和offset误差差不多吻合,但是增益为何……)不过这个表格的作用是用于估算误差的大致范围的,实际上运放的参数可能要优于典型值,也可能会更差。鉴于我用的是拆机运放…我倾向于最终的系统指标会更差。

另外,我发现DMM的读数误差对测量结果影响非常可观。比如说我第一次把INL画出来后,发现有一个点出现了-9LSB的峰值,然后我折回去看测试数据,发现是我读数的时候小数点后多读了一个0,本应是1300.11mV的,我写成了1300.011mV,结果上就直接偏出去了8个LSB之多。(1LSB约为9.53uV,根据计算也能得到同样的偏差结果),如果最后一位读数有着1uV的偏差,那么结果就直接会偏出约0.1LSB。所以测量这种精度级别的DAC器件时,🐟感觉还是得需要一个 至少7位半的DMM 才能保证测量精度。MAXIM推荐DMM能测试到待测DAC的1个LSB的1/100,对于VREF=2.5V的18-bit DAC来说,一个LSB约9.5uV,那么测试用万用表需要能测到100nV级别…(这就开坑做个nanoVolt Meter(bushi

此时还没用到LTC2756的Gain和Offset Trim功能,如果用上之后,接上高位DMM进行校准,那结果会更美妙~(等俺有钱了一定.jpg

顺便欣赏一下新版本的电子涩图~

Next?

2023.6.25晚6点,ADI的微信公众号发布了一篇推文,是这篇技术文章的翻译: How to Successfully Calibrate an Open-Loop DAC Signal Chain

555,有种宇宙为我而闪烁的感觉(误。

既然我们测量了2756的传输函数,那么我们是不是可以依据此函数对其进行幅度校正,就如上面提到的那篇技术文章一样,让这个小模块的输出电压更Precise呢?答案当然是肯定的,况且我还在这个板子上塞了个24-bit的Σ-Δ ADC呢(虽然直到现在我都没有写代码23333)

最近🐟要好好休息一下,等哪天休息好了再来更新!

参考文献与资料

- Josephson Voltage Standard

- Kelvin–Varley divider

- Fluke 720A Kelvin–Varley divider

- 中国工程院-高洁

- 约瑟夫森效应

- ADR1000 Product details

- LTZ1000 datasheet

- xDevs-ADI ADR1000, new ultra-low noise zener voltage reference

- CN-0531 Reference Design

- AD5791 datasheet

- LTC2756 datasheet

- AN4159:Measuring the Linearity of Differential-Output,Current-Mode Digital-to-Analog Converters (DACs)

- INL/DNL Measurements for High-Speed Analog-to-Digital Converters (ADCs)

- How to Successfully Calibrate an Open-Loop DAC Signal Chain

学习资源

MT-087:基准电压源

MT-015:DAC基本架构Ⅱ:二进制加权DAC

用20位DAC实现1ppm精度—精密电压源

The Data Convertion Handbook (2005)

![Read more about the article 雷达信号处理-[2]-信号滤波与降噪](https://www.emoe.xyz/wp-content/uploads/2021/11/symlet-Wavelet-300x124.gif)

![雷达信号处理-[4]-匹配滤波与脉冲压缩](https://www.emoe.xyz/wp-content/uploads/2021/11/10-600x452.jpg)

![雷达信号处理-[1]-噪声信号与雷达基带信号产生](https://www.emoe.xyz/wp-content/uploads/2021/11/4-2-600x316.jpg)

呜呜呜好涩的板子

Hi Floydfish: can you please give your email here, I will contact you if you want to have samples from us.

you should make zero and gain calibration first before inl measurement

I’m very pleased to hear from you:) and thanks for your advise!

Currently the design I made does not support gain and offset trim, because I didin’t fan out the GEadj and VOSadj pin of LTC2756 for calibration…and to achieve this, I will need an additional 2-ch DAC to perform this cal work:D. During the next evaluation maybe I will complete this design and make more improvements.

My email address is summer200816@outlook.com, hope to hear from you, and Thank you again!